MAX2235為三級功率放大器,工作在800MHz至1000MHz范圍,在GSM和ISM應用中可產生高達30dBm的功率放大器。實現最大性能并非易事,最好的起點是良好的 PC 板布局。本文回顧了經過驗證的布局實踐,并幫助讀者了解PA的性質和所提議技術背后的基本原理。

常規

MAX2235為三級功率放大器,工作頻率范圍為800MHz至1GHz,在GSM和ISM應用中可產生高達30dBm的輸出功率。實現這種類型的性能不是一件小事,最好的起點是良好的 PC 板布局。相反,更重要的是,設計不良的 PC 板布局絕對無法實現最佳性能。

本文將回顧經過驗證的布局實踐,并幫助讀者理解該IC的性質和所提出技術背后的基本原理。作為新布局的指南,它將幫助任何使用MAX2235進行設計的人避免常見的陷阱,并充分利用其設計。

供應旁路和級間匹配

也許這個IC最不被理解和最重要的方面之一是階段間匹配。由于放大器實際上由三個獨立的級組成,并且每個級的阻抗特性略有不同,因此它們必須相互匹配以提供最大的功率傳輸。

Vcc器件上的引腳 3、5、8 和 9 并非需要旁路的純電源輸入。施加到這些引腳的集總元件電容(和寄生效應)在內部與器件相互作用,并提供一定程度的級間匹配。這允許設計人員為其特定應用自定義匹配項。

為了充分利用這種設計的靈活性,旁路電容位置應沿VCC走線進行一定程度的調節,VCC通孔和器件引腳之間的電容應保持一定程度的偏差。通過沿VCC走線滑動電容,可以根據經驗確定級間電容和IC引腳之間的最佳走線長度,以獲得所需的工作頻率(見圖1)。在這些位置使用高Q值電容器通常可提供最佳匹配,0402尺寸組件使調諧的物理過程易于管理(與幾乎沒有調整空間的0603和可能更難物理操作的0201相反)。村田制作所GJM1555系列(以前的GJ615)已用于此應用,并取得了良好的效果。它們的Q因數在900MHz時大于100。

圖1.沿 V 可調旁路電容器位置抄送跟蹤。

鑒于PA的電源引腳充當級間匹配,因此盡可能將線路彼此隔離非常重要。(注意:“隔離”一詞在這里純粹是RF意義上的。當然,這些線路是直流耦合的。如果不做到這一點,RF能量可能會以一種不利于性能的方式從一個級耦合到另一個級。使用“星形拓撲”是一種有效隔離每個階段的電源線的方法。在這種配置中,每條電源線都源自一個點,在那里用一個大電容器旁路。然后,這些線路在印刷電路板的底層上運行,并盡可能合理地彼此物理分離。VCC線路之間的耦合在底層減少,因為線路由接地層隔開,而不是內層的電介質。每個單獨的線路都由級間匹配帽在本地繞過,該帽同時匹配級間節點。最好將蓋子放在頂部,因為這可以非常接近定位并最大程度地控制比賽。圖2顯示了這些元件的推薦放置和方向。

圖2.“星形拓撲”的元件放置。

接地

MAX2235采用TSSOP-EP封裝,底部配有裸露接地焊盤。該焊盤絕對必須接地,因為PA的輸出級從該連接中獲得接地。如果沒有低電感接地路徑,將發生不希望的發射極退化,從而導致增益性能下降。從IC到PCB接地層的熱傳遞也是通過這種物理連接完成的。最好采用具有較大表面積的設計,用于焊接裸露焊盤。在組裝過程中允許焊料流動的路徑也很重要 - 在印刷電路板焊盤本身中提供多個直通孔。IC的GND引腳應全部直接布線回同一焊盤。這也為其他PA級提供了最短的接地路徑(見圖3)。

圖3.裸露的槳必須接地。

輸出網絡

當前的評估套件在這方面可能具有誤導性。它是為非常特定的性能頻段設計的,雖然功能強大,但不一定應該復制用于其他應用。評估板采用30AWG導線與0Ω電阻并聯,從引腳16至Vcc.Maxim目前不建議在新設計中使用導線短路和電阻上拉作為輸出。相反,使用 L||C 組合拉至 V抄送.如果仔細選擇LC的并聯諧振,它將在目標頻率下看起來像高阻抗(因此不會影響匹配),但將有助于大大衰減諧波。在915MHz的設計中,10nH和3.3pF的值產生了非常好的諧波抑制和最小的輸出匹配干擾。

在設計輸出匹配時,可以使用與級間類似的方法。沿傳輸線滑動輸出分流電容可以精確調整PA輸出的阻抗。評估板使用雙元件匹配演示該方法。為了獲得更多的調整能力,四元件匹配(L系列、分流C、L系列、分流C)已被證明工作良好(見圖4)。無論采用何種阻抗轉換方法,都建議使用由多個相鄰接地過孔包圍的受控阻抗傳輸線。這最大限度地減少了 PC 板損耗,并通過沿線路提供暢通無阻的 RF 接地返回路徑來改善諧波抑制。另請注意,在匹配中使用高Q值組件(目標頻率為>100)對于在原型和生產中實現最佳性能至關重要。再次推薦使用村田制作所GJM1555系列(或同等產品)。

圖4.四元件輸出與高 Q 值電感器和電容器匹配。

總結

與所有RF功率放大器一樣,MAX2235的最佳性能取決于印刷電路板布局過程中的謹慎決策。在構建第一個原型之前,應徹底考慮以下事項:

臺間比賽放置 Vcc旁路/級間匹配電容盡可能靠近IC引腳(3、5、8和9),并允許在初始整定期間進行位置調整。使用高 Q 值成分以獲得最佳效果。

Vcc路由使用允許不同PA級電源線之間最大距離(從而最小耦合)的拓撲結構。印刷電路板底層的“星形拓撲”在這里非常有效。旁路 V抄送全球。

接地為 IC 引腳提供最短、最低的接地電感路徑。考慮 IC 底部裸露焊盤的焊接流動性和制造能力。這必須綁在地平面上!

輸出匹配使用高Q值元件和四元件匹配,然后使用受控阻抗傳輸線。可以在匹配之前在上拉電感上實現諧波陷阱,而不會影響阻抗變換。

圖5顯示了這些關鍵項目的實現,圖6給出了另一塊Maxim評估板上的“星形拓撲”實際示例。

圖5.實現在構建第一個原型之前要考慮的關鍵項目。

圖6.Maxim評估板上的“星形拓撲”示例

審核編輯:郭婷

-

放大器

+關注

關注

143文章

13634瀏覽量

214216 -

電容器

+關注

關注

64文章

6256瀏覽量

100239 -

功率放大器

+關注

關注

102文章

3626瀏覽量

132296

發布評論請先 登錄

相關推薦

版圖設計資料推薦

國科大《集成電路先進光刻技術與版圖設計優化》課程分享之二:浸沒式光刻工藝缺陷種類、特征及自識別方法

MAX2235 pdf datasheet (+3.6V,

如何為MAX1470超外差接收機選擇石英晶體振蕩器

MAX2235的電路板布局優化技術

用于GSM和900MHz-ISM頻段的超低成本+30dBm

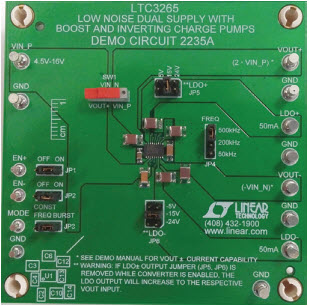

基于DC2235A直流到直流多輸出電源的參考設計

基于人工智能技術的版圖級優化設計流程

MAX2235EVKIT+ 射頻評估和開發套件,開發板

MAX2235EVKIT 射頻評估和開發套件,開發板

超低成本+30dBm PA,適用于GSM和900MHz-ISM應用

CMP工藝影響下的版圖優化

MAX2235—版圖優化技術

MAX2235—版圖優化技術

評論