什么是 UVM transaction?

UVM 中的事務是一個具有信號屬性(例如地址和數據)以及錯誤、延遲等額外信息的類。總之,這個所謂事務封裝了所有和DUT激勵項相關的信息. 但是,我們無法僅通過單個事務去驗證設計,我們需要一組相關的事務。

注意:這里的“相關”也正體現了驗證工程師的經驗,試想如果全依賴隨機如何能夠沖擊到DUT 的corner case呢?

這里就引入了uvm sequence。

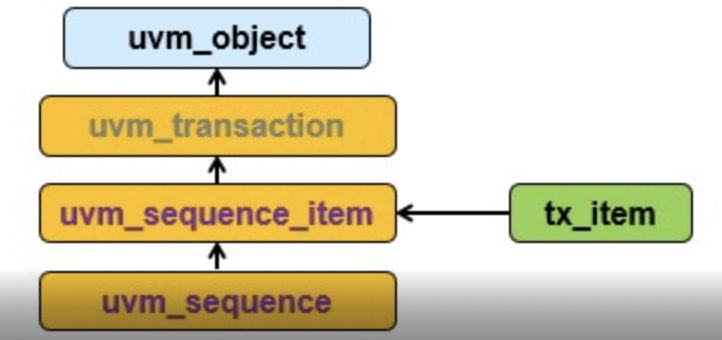

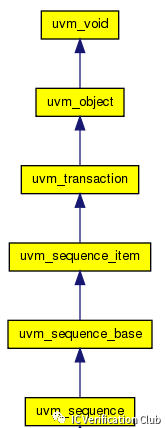

UVM中的一組相關事務稱為uvm sequence,單個事務稱為sequence items。當你開發一個事務項類時,需要擴展自uvm_sequence_item,而不是 uvm_transaction。

上面是事務項類的層次結構,其中tx_item就是我們施加給DUT的單個事務。

使用uvm_sequence_item而不是uvm_transaction 的優勢

uvm_transaction 類是遺留下來的驗證方案中的一部分,它的缺點是不知道上下文,即不知道自己是否屬于一組事務中的一部分。

而uvm_sequence_item類中除了前面提到的接口屬性之外,還加入了幾個連接到外部世界的屬性。

舉個例子,像內存讀寫這樣的事情,一般都會有一個“響應”,它會告訴上游模塊是否已經完成了讀寫操作以及讀取的值。

uvm驗證環境中的driver也可能同時處理多個sequence,所以同樣需要將響應路由到正確的sequence。所以,uvm_sequence_item類帶有一個sequence ID 屬性,因此響應能夠被返回到正確的位置(sequence)。

UVM sequencer就像是一個交通路口紅綠燈,因為多個sequence可能會通過同一個driver激勵DUT,其中sequencer會在sequence之間進行仲裁。

uvm_sequence_item中有一個uvm_sequencer的句柄(通過sequence的start方法傳遞),如下所示:

my_sequence.start(env.agt.sqr);sequence是可以分層的,一個sequence可以啟動其他sequence,這種情況下每個 uvm_sequence_item 都有一個指向parent sequence的句柄。

結論

當開發UVM 測試平臺時,事務類一定需要從 uvm_sequence_item 擴展,而不是uvm_transaction。

審核編輯:劉清

-

UVM

+關注

關注

0文章

182瀏覽量

19228 -

DUT

+關注

關注

0文章

189瀏覽量

12490

原文標題:為什么使用 uvm_sequence_item 而不是uvm_transaction構建 UVM 事務?

文章出處:【微信號:芯片驗證工程師,微信公眾號:芯片驗證工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

數字IC驗證之“什么是UVM”“UVM的特點”“UVM提供哪些資源”(2)連載中...

數字IC驗證之“搭建一個可以運行的uvm測試平臺”(5)連載中...

什么是uvm?uvm的特點有哪些呢

如何構建UVM寄存器模型并將寄存器模型集成到驗證環境中

談談UVM中的uvm_info打印

UVM中seq.start()和default_sequence執行順序

典型的UVM Testbench架構

UVM中uvm_config_db機制背后的大功臣

UVM中uvm_config_db機制背后的大功臣

一文詳解UVM設計模式

UVM設計中的sequence啟動方式有哪幾種呢?

為什么不是uvm_transaction構建UVM事務呢?

為什么不是uvm_transaction構建UVM事務呢?

評論