ChatGPT在后端設(shè)計中有什么應(yīng)用?ChatGPT懂后端EDA工具么?

本以為ChatGPT對于IC后端設(shè)計幫助應(yīng)該不大,畢竟它非常依賴EDA工具,它對于EDA工具這種非常專業(yè)的、非常Custom的東西了解和訓(xùn)練的數(shù)據(jù)應(yīng)該不多,所以可能幫不上什么忙。

所以我在基本后端知識、EDA工具的使用方面問了ChatGPT,我們看一下它的回復(fù),整體的結(jié)果還是有點(diǎn)超出我的想象的。

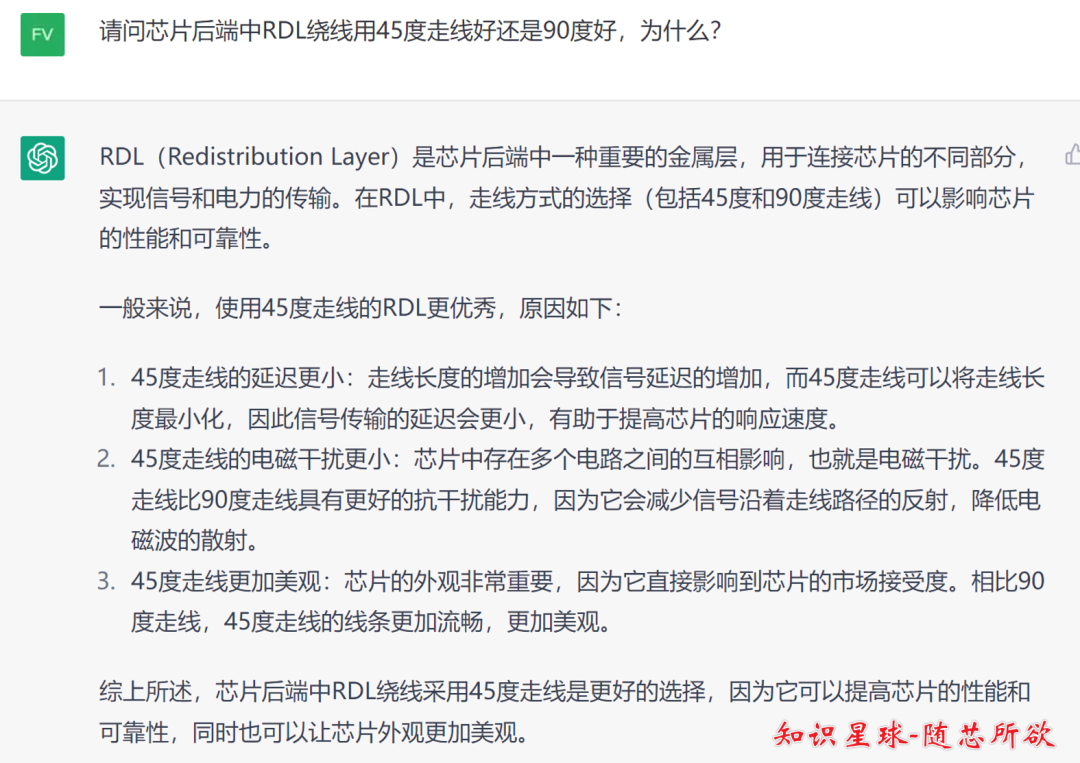

1、后端中的一些知識

從中可以看出工具給的回復(fù)還是有一些參考性的,從中我們能找到一些想要的結(jié)果。

2、ChatGPT對于EDA工具以及Flow的理解

從下面的回復(fù)中可以看出ChatGPT對于DC做綜合的流程還是有一個大概的了解的,且說的內(nèi)容也都是大體正確的,某些命令可能有些問題(比如讀入時序約束文件一般用read_sdc而非read_file,設(shè)置周期也是在sdc里面創(chuàng)建clock或者generate clock,而非set_clock_period),其他的大問題基本上沒啥。

問:麻煩寫一個用Synopsys公司的design compiler軟件做邏輯綜合的教程

ChatGPT的回答:

好的,下面是一個使用Synopsys公司的Design Compiler軟件進(jìn)行邏輯綜合的簡單教程。

步驟1:準(zhǔn)備設(shè)計文件和約束文件

在使用Design Compiler進(jìn)行邏輯綜合之前,必須準(zhǔn)備好設(shè)計文件和約束文件。設(shè)計文件通常是Verilog或VHDL代碼,而約束文件包含時序和其他綜合約束。確保這些文件在同一個目錄下,并且已經(jīng)準(zhǔn)備好進(jìn)行綜合。

步驟2:啟動Design Compiler

打開終端窗口,輸入dc_shell命令啟動Design Compiler。dc_shell是Design Compiler的主要交互式控制臺。在dc_shell控制臺中,可以輸入各種命令,例如編譯、優(yōu)化、綜合等。

步驟3:設(shè)置工作目錄和綜合庫

在Design Compiler中,必須指定工作目錄和綜合庫。工作目錄是當(dāng)前正在使用的目錄。使用cd命令更改工作目錄。綜合庫包含所有必要的庫文件,例如模擬模型、物理庫和邏輯庫。使用以下命令將綜合庫添加到Design Compiler中:

set target_library

其中,library_name是綜合庫名稱。可以使用list_libraries命令列出所有可用的庫。例如,使用以下命令列出所有庫:

list_libraries

步驟4:讀取設(shè)計文件和約束文件

使用以下命令在Design Compiler中讀取設(shè)計文件和約束文件:

read_file

read_file

其中,design_file_name是設(shè)計文件的名稱,constraint_file_name是約束文件的名稱。如果文件位于當(dāng)前工作目錄中,則不需要輸入完整路徑。

步驟5:綜合設(shè)計

使用以下命令對設(shè)計進(jìn)行邏輯綜合:

compile -map_effort high -area_effort high

其中,top_module_name是頂層模塊的名稱。map_effort和area_effort參數(shù)控制綜合的時間和面積的優(yōu)化程度。通常,將它們設(shè)置為“high”可以獲得最佳的綜合結(jié)果。

步驟6:分析綜合結(jié)果

使用以下命令分析綜合結(jié)果:

report_area

report_timing

report_power

這些命令將分別顯示面積、時序和功耗報告。在綜合完成后,應(yīng)該始終檢查這些報告,以確保綜合結(jié)果符合要求。

步驟7:保存綜合結(jié)果

使用以下命令將綜合結(jié)果保存為Verilog網(wǎng)表文件:

write_verilog

其中,netlist_file_name是要保存的網(wǎng)表文件名。

這是一個簡單的使用Synopsys公司的Design Compiler軟件進(jìn)行邏輯綜合的教程。請注意,這只是一個基本的示例,并請注意,這只是一個基本的示例,并且Design Compiler擁有許多功能和選項(xiàng),可以根據(jù)需要進(jìn)行自定義和調(diào)整。在實(shí)際使用中,您可能需要更深入地了解Design Compiler的功能和選項(xiàng),并調(diào)整綜合設(shè)置以獲得最佳結(jié)果。

以下是一些有用的Design Compiler命令和選項(xiàng):

set_input_delay:設(shè)置輸入延遲

set_output_delay:設(shè)置輸出延遲

set_clock_period:設(shè)置時鐘周期

set_max_area:設(shè)置最大面積限制

set_max_fanout:設(shè)置最大負(fù)載限制

set_max_delay:設(shè)置最大延遲限制

set_dont_touch:設(shè)置不綜合的信號或模塊

此外,Design Compiler還提供了許多優(yōu)化選項(xiàng),例如綜合策略、綜合限制和優(yōu)化級別等。根據(jù)實(shí)際需求進(jìn)行適當(dāng)調(diào)整可以獲得更好的綜合結(jié)果。

最后,請注意Design Compiler是一款商業(yè)軟件,需要購買許可證才能使用。此外,Design Compiler還有許多其他工具和插件,例如PrimeTime和Formality等,可以進(jìn)行時序分析和形式驗(yàn)證等操作。如果需要使用這些工具,請參閱Synopsys公司的官方文檔以獲取更多信息。

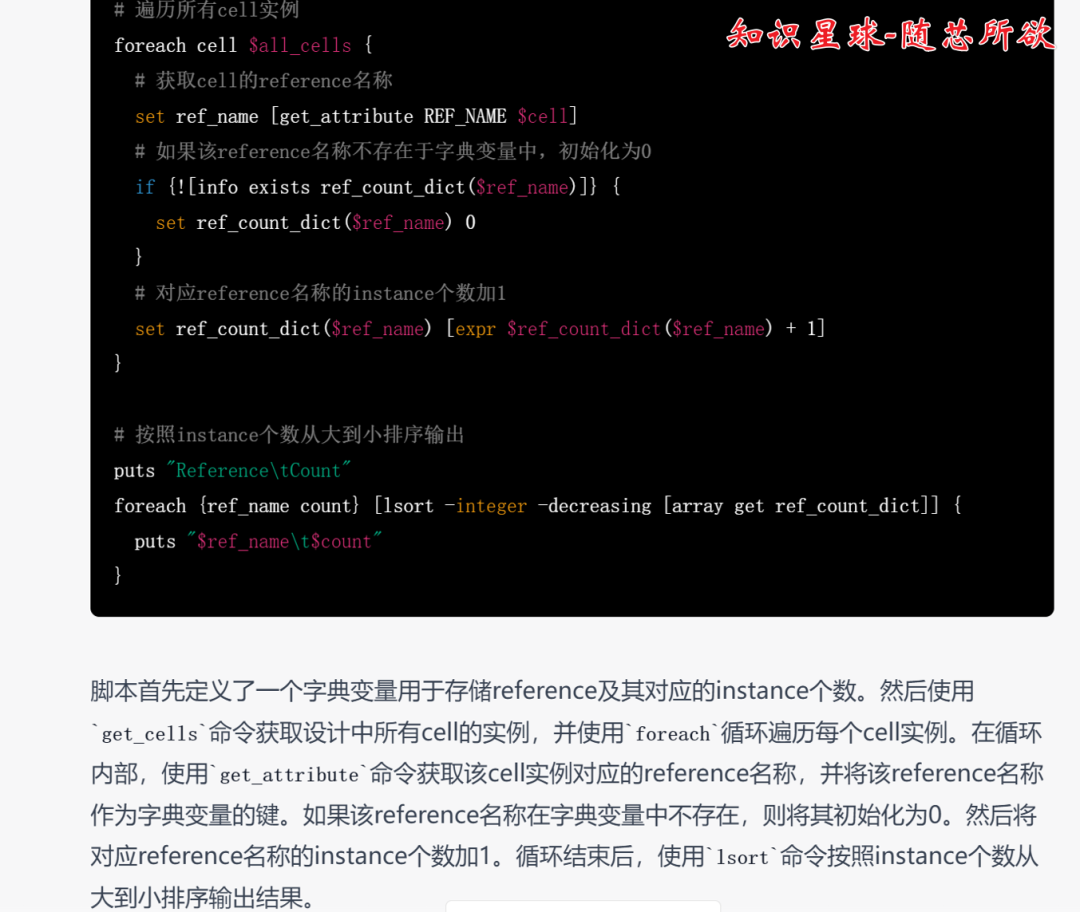

3、后端工具內(nèi)的tcl腳本的編寫

ChatGPT給出的腳本:

# 定義一個字典變量用于存儲reference及其對應(yīng)的instance個數(shù)

set ref_count_dict {}

# 獲取設(shè)計中所有cell的實(shí)例

set all_cells [get_cells -hier *]

# 遍歷所有cell實(shí)例

foreach cell $all_cells {

# 獲取cell的reference名稱

set ref_name [get_attribute REF_NAME $cell]

# 如果該reference名稱不存在于字典變量中,初始化為0

if {![info exists ref_count_dict($ref_name)]} {

set ref_count_dict($ref_name) 0

}

# 對應(yīng)reference名稱的instance個數(shù)加1

set ref_count_dict($ref_name) [expr $ref_count_dict($ref_name) + 1]

}

# 按照instance個數(shù)從大到小排序輸出

puts "Reference Count"

foreach {ref_name count} [lsort -integer -decreasing [array get ref_count_dict]] {

puts "$ref_name $count"

}

從中能看出幾個問題:

1、ChatGPT混用了字典和array,下面用的是array get,前面卻說的是字典dict。

2、另外在get_cells的時候需要把hier的Cell給濾掉,工具沒有濾掉。

3、對于get_cells得到的結(jié)果,應(yīng)該用foreach_in_collection去循環(huán)而非foreach。

4、對于工具native的命令,ChatGPT可能會用錯,get_attr $cell ref_name才是正確的用法

5、在用lsort對ref list按照個數(shù)排序時,它沒有指定-stride和-index

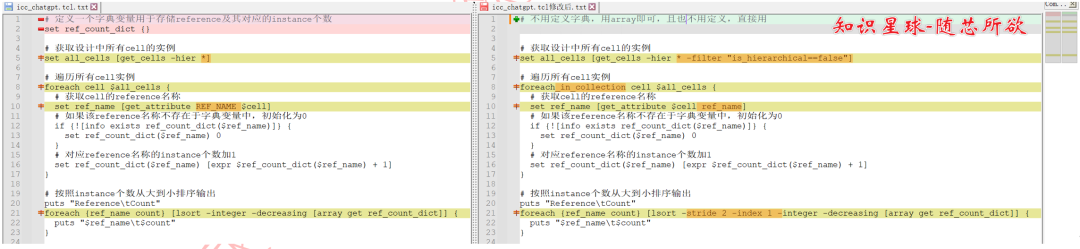

下面是ChatGPT給出的tcl腳本和我修改后的版本的對比:

下面是我修改后的腳本:

# 不用定義字典,用array即可,且也不用定義,直接用

# 獲取設(shè)計中所有cell的實(shí)例

set all_cells [get_cells -hier * -filter "is_hierarchical==false"]

# 遍歷所有cell實(shí)例

foreach_in_collection cell $all_cells {

# 獲取cell的reference名稱

set ref_name [get_attribute $cell ref_name]

# 如果該reference名稱不存在于字典變量中,初始化為0

if {![info exists ref_count_dict($ref_name)]} {

set ref_count_dict($ref_name) 0

}

# 對應(yīng)reference名稱的instance個數(shù)加1

set ref_count_dict($ref_name) [expr $ref_count_dict($ref_name) + 1]

}

# 按照instance個數(shù)從大到小排序輸出

puts "Reference Count"

foreach {ref_name count} [lsort -stride 2 -index 1 -integer -decreasing [array get ref_count_dict]] {

puts "$ref_name $count"

}

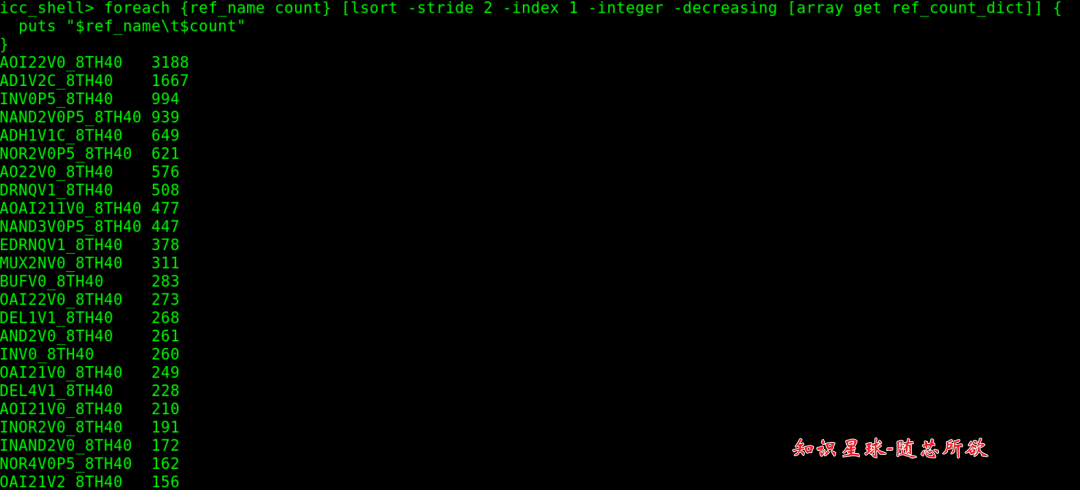

我修改之后的腳本的執(zhí)行結(jié)果:

4、總結(jié)與展望

后邊我又試了其他幾個腳本編程的Case,ChatGPT給出的結(jié)果當(dāng)然會有各種各樣的問題,畢竟關(guān)于工具native的命令ChatGPT沒有那么多Training的樣本,但是它給出的結(jié)果還是有點(diǎn)出乎我的以外的,具有一定的參考性的,整體的思路還是比較正確的。

發(fā)散一下,再過幾年,在用更多后端EDA工具的UG以及相關(guān)腳本對GPT訓(xùn)練的話,那么ChatGPT可以做的事情肯定會非常非常多,前途不可限量!!!!如果把ChatGPT嵌入到EDA工具中或者Solvnet/Cadence home上,那么對于Designer而言會有非常大的幫助。也許User只需要做一些簡單的描述,工具就能很快給出參考的腳本或者對用戶提出的問題給出參考的解決方案。

審核編輯:劉清

-

EDA工具

+關(guān)注

關(guān)注

4文章

268瀏覽量

31941 -

Verilog語言

+關(guān)注

關(guān)注

0文章

113瀏覽量

8309 -

VHDL源碼

+關(guān)注

關(guān)注

0文章

2瀏覽量

1199 -

ChatGPT

+關(guān)注

關(guān)注

29文章

1570瀏覽量

8067

原文標(biāo)題:ChatGPT在后端設(shè)計中有什么應(yīng)用?ChatGPT懂后端EDA工具么?

文章出處:【微信號:集成電路設(shè)計及EDA教程,微信公眾號:集成電路設(shè)計及EDA教程】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

【國產(chǎn)FPGA+OMAPL138開發(fā)板體驗(yàn)】(原創(chuàng))6.FPGA連接ChatGPT 4

在FPGA設(shè)計中是否可以應(yīng)用ChatGPT生成想要的程序呢

OpenAI 深夜拋出王炸 “ChatGPT- 4o”, “她” 來了

讓chatGPT幫我寫硬件代碼,是懂行的,好助手!#chatgpt #物聯(lián)網(wǎng)開發(fā) #python開發(fā)板

#chatgpt 使用chatGPT輔助開發(fā)第一彈-電路設(shè)計,讓它設(shè)計一個放大電路,看下效果#人工智能

科技大廠競逐AIGC,中國的ChatGPT在哪?

TIA電路在后端加濾波器的時候看到方波變形的情況怎么解決?

前后端協(xié)同的時鐘樹設(shè)計方法

后端系統(tǒng),后端系統(tǒng)是什么意思

數(shù)字后端基本概念介紹

virtIO中有兩種方式控制前后端的notify

學(xué)后端的學(xué)前端有必要嗎?

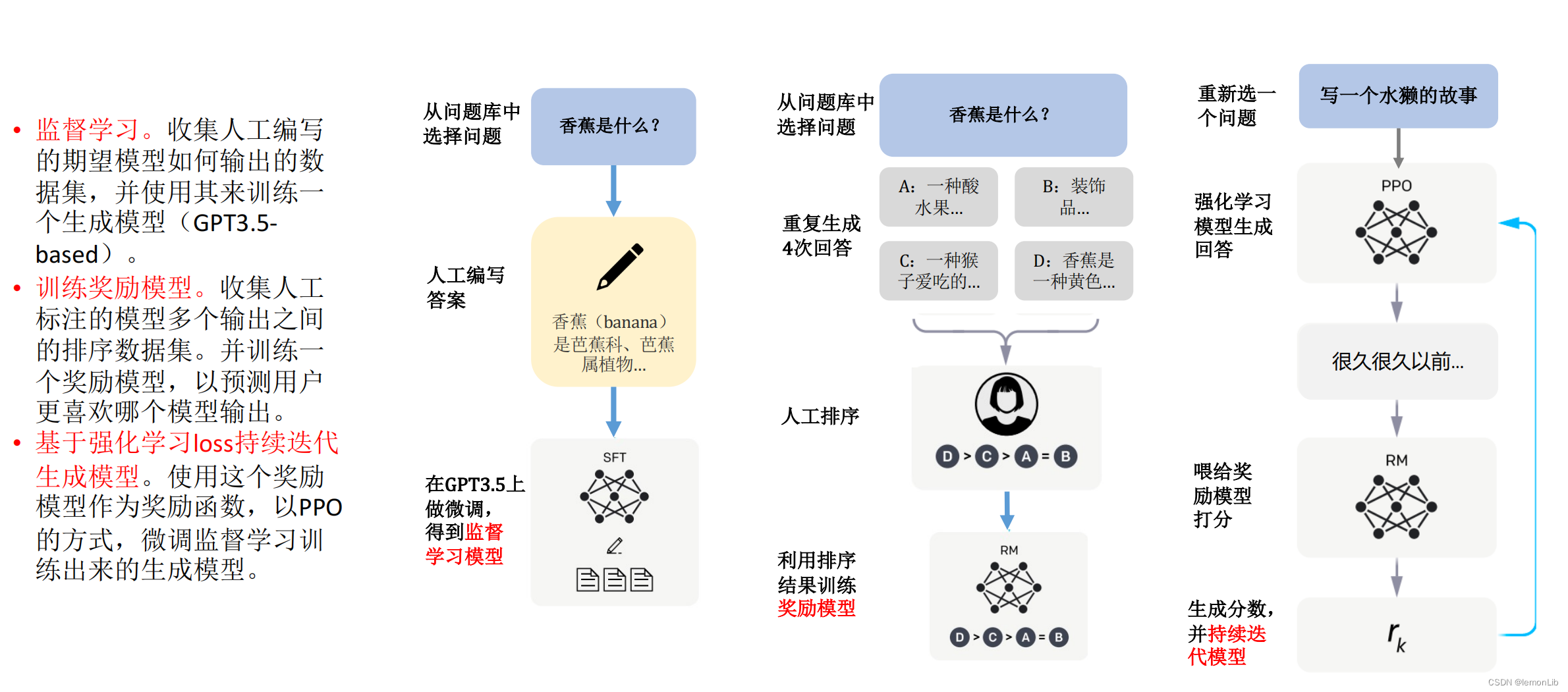

ChatGPT原理 ChatGPT模型訓(xùn)練 chatgpt注冊流程相關(guān)簡介

ChatGPT在后端設(shè)計中有什么應(yīng)用?

ChatGPT在后端設(shè)計中有什么應(yīng)用?

評論