上次我們介紹了RS觸發器,他是由兩個(或非門)或者(與非門)組成的。

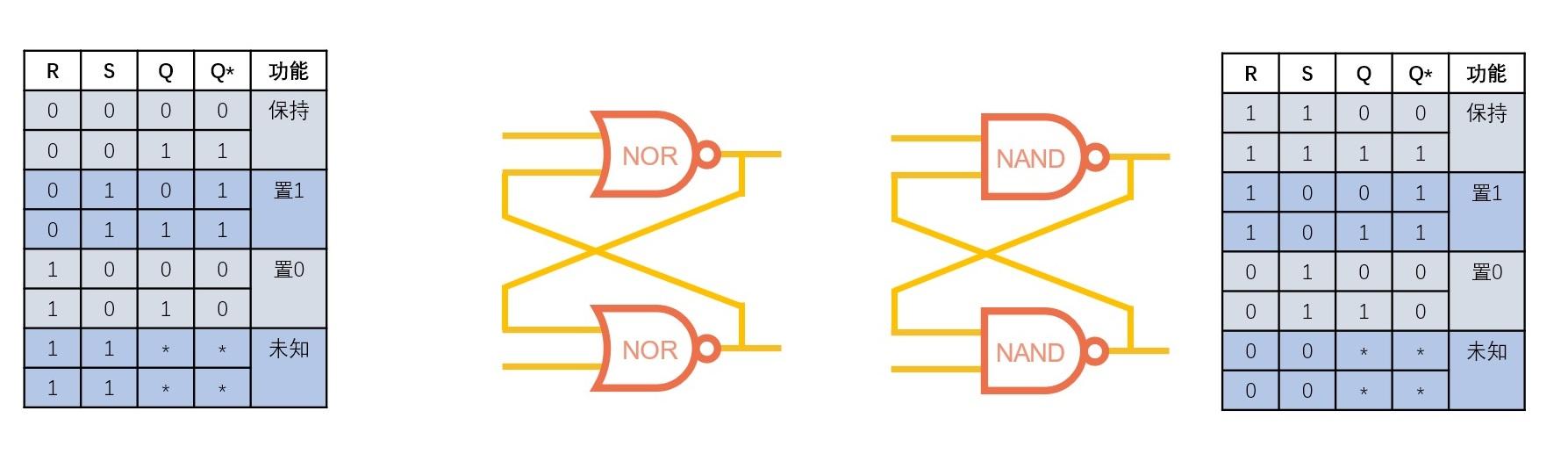

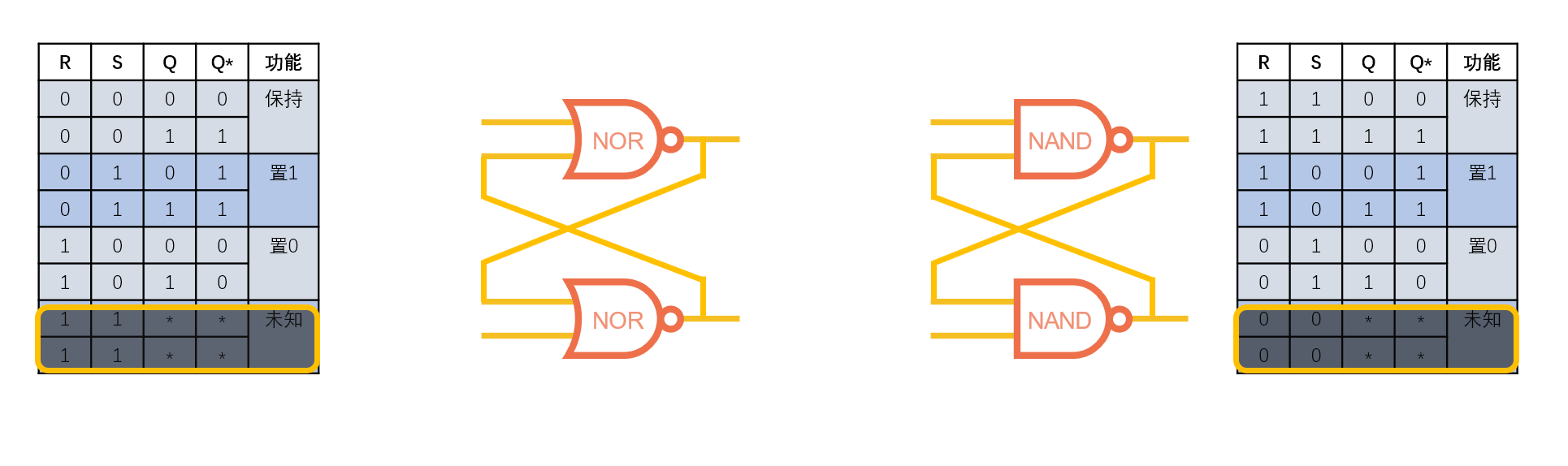

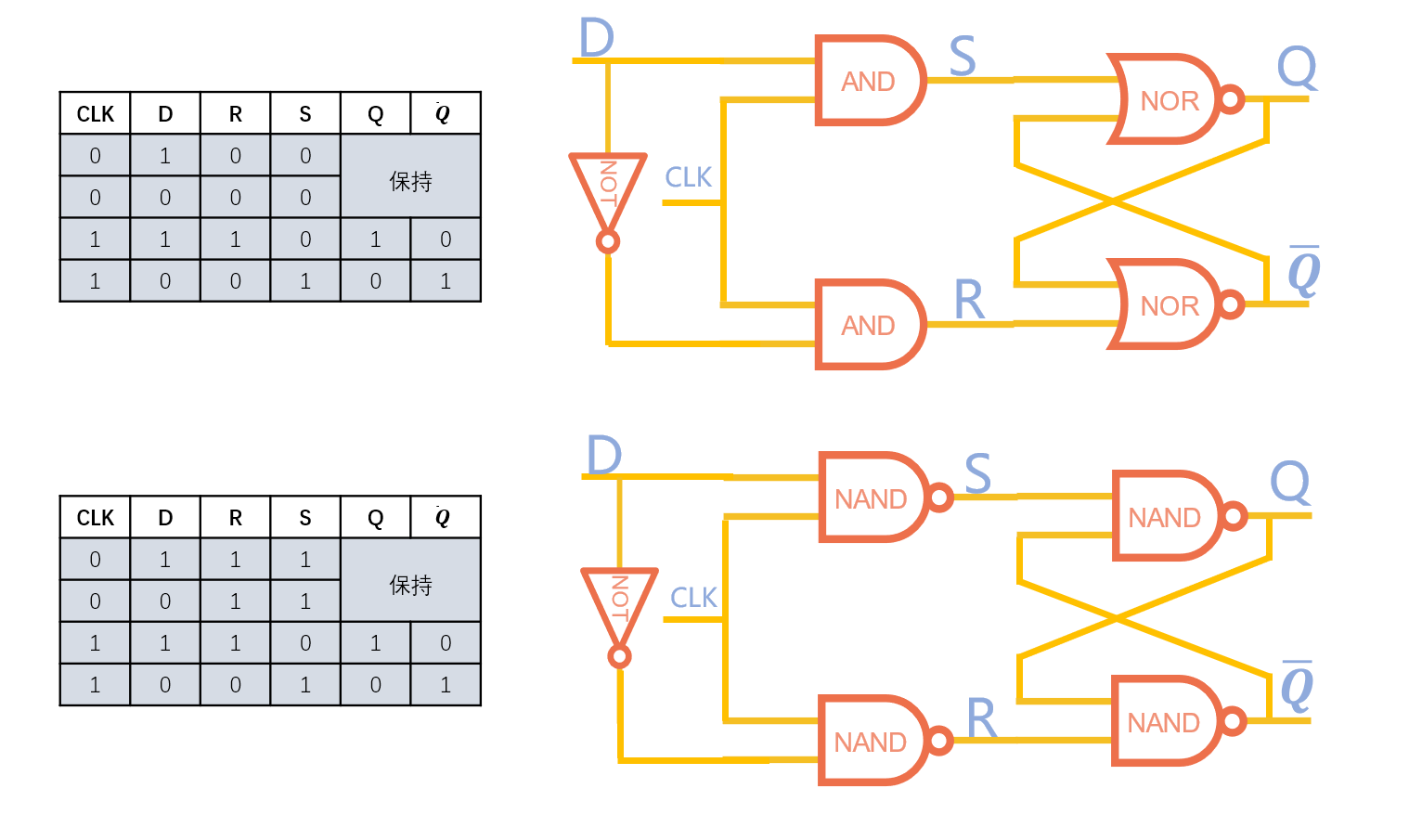

或非門RS觸發器(左) 與非門RS觸發器(右)

其核心就是圖上的這個交叉反饋連接,而這條小小的反饋就完成了從組合邏輯到時序邏輯的跨越。讓這個小小的電路有了記憶,可以記住上一刻發生的事(0和1)。

做過網絡運維的小伙伴,一看到這個叉心里肯定一激靈。一個叉畫起來簡單,復雜性卻是指數上升。

讓我們來仔細把玩一下RS觸發器。

先看一下兩種電路的真值表。(或非門)組成的RS觸發器R=0,S=0時是保持狀態,(與非門)的R=1,S=1時是保持狀態。如下圖所示

RS觸發器的保持態

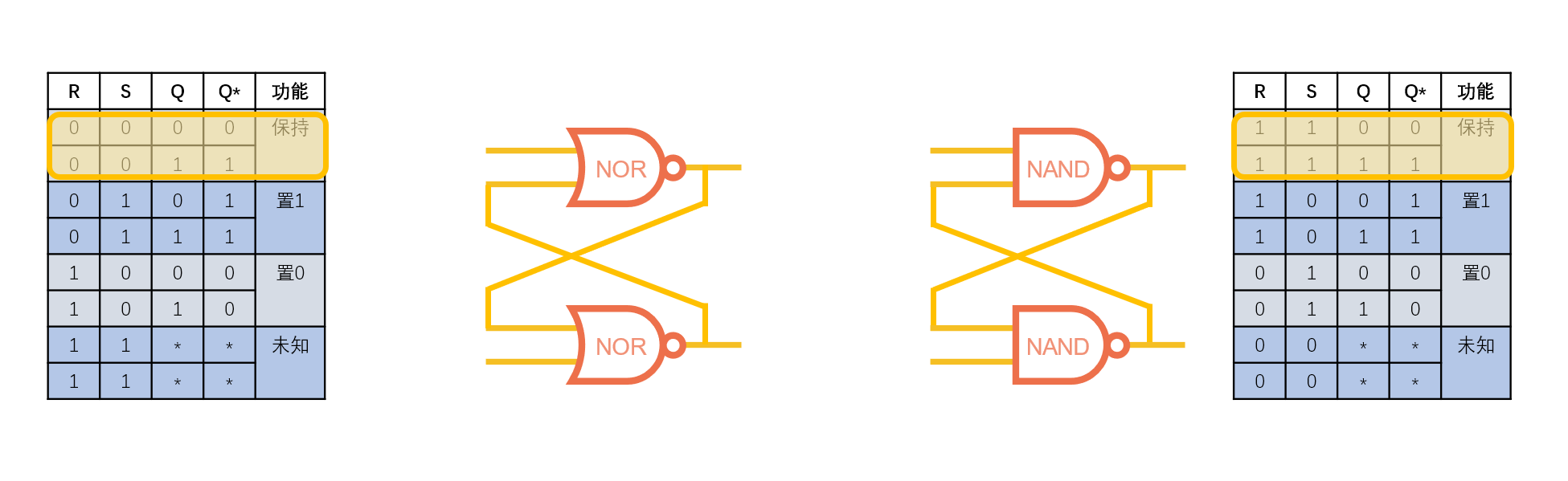

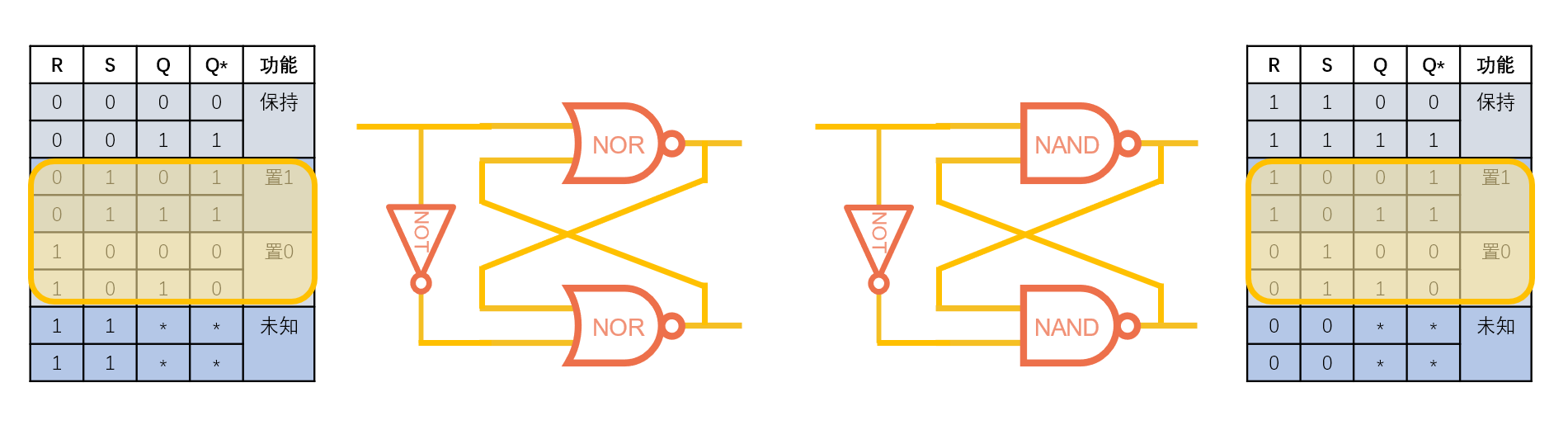

R=0,S=1時,(或非門)觸發器的功能是置1,(與非門)的置1正好相反,是R=1,S=0。如下圖所示

RS觸發器置1

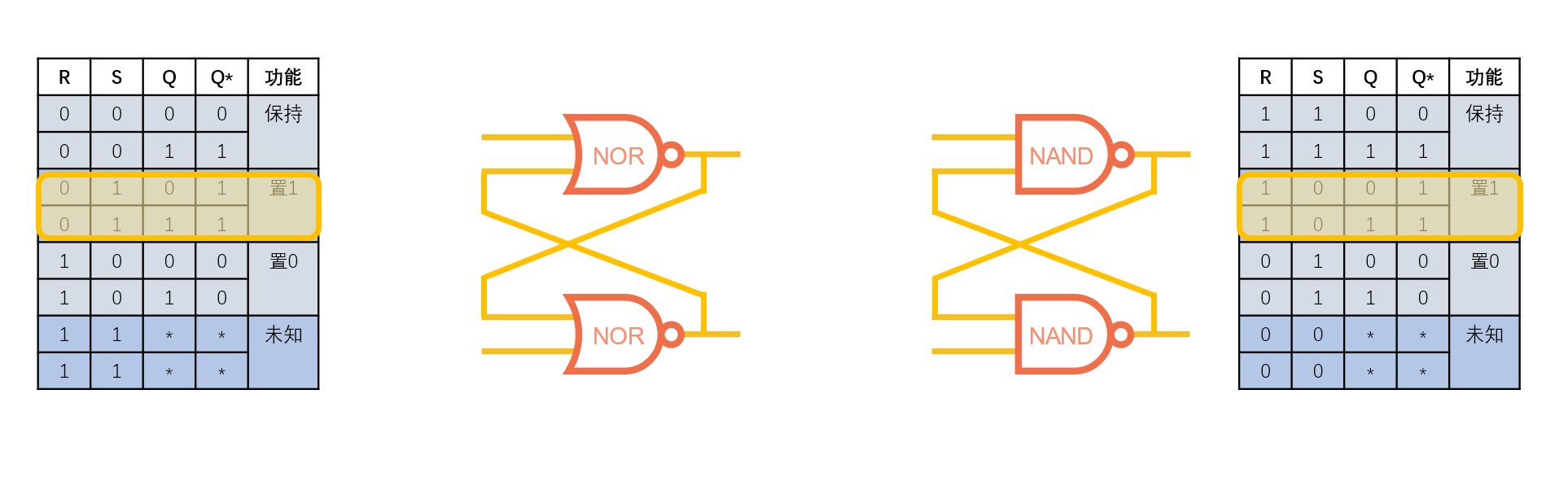

R=1,S=0時,(或非門)觸發器置0,(與非門)反過來,是R=0,S=1。如下圖所示

RS觸發器置0

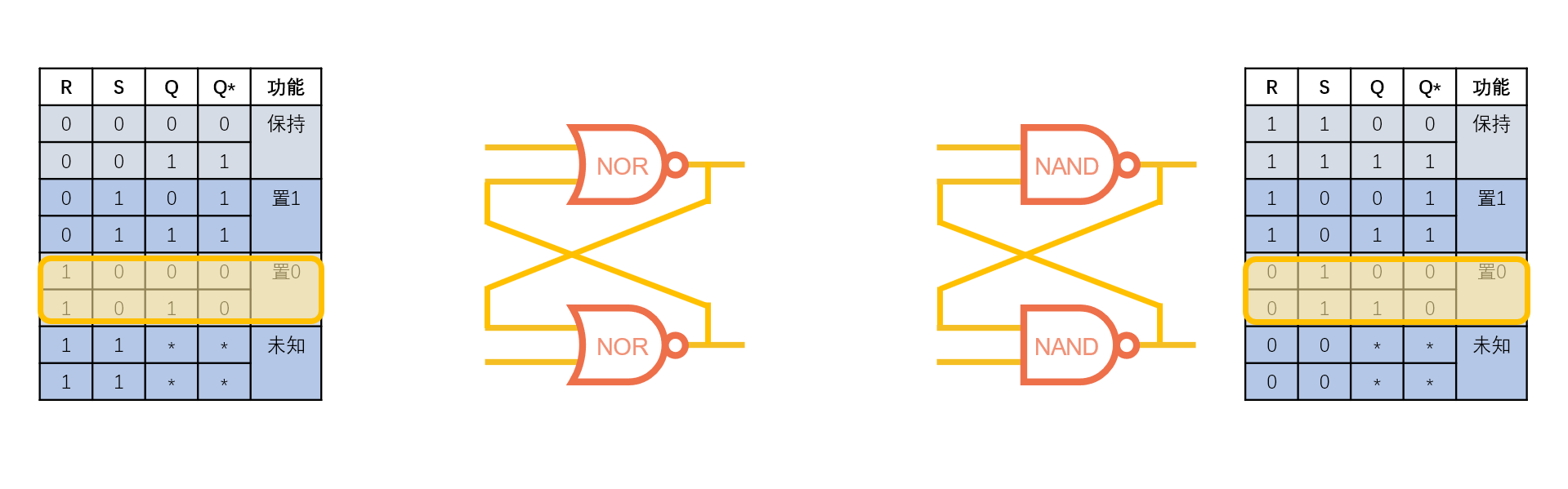

RS觸發器有一個不可知的狀態,對(或非門)電路來說,是RS同為1,(與非門)是同為0。如下圖所示

RS觸發器狀態未知

不可知的狀態并不是電路沒有輸出了,只是無法根據輸入來確認輸出,也就是說輸出可能是這樣,也可能是那樣,因此我們沒有辦法來利用這個狀態。

最初級的D寄存器

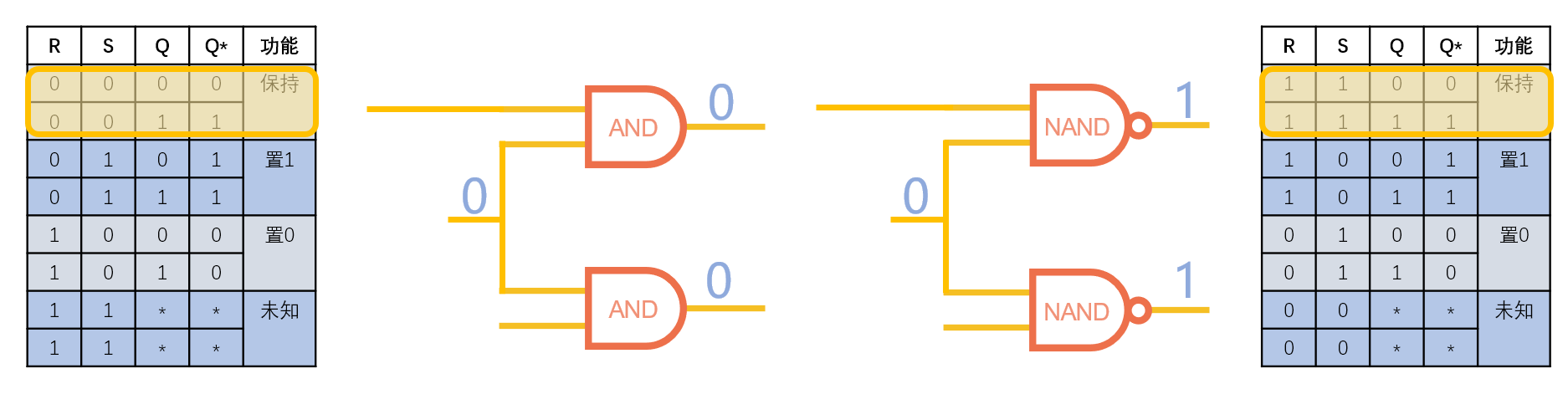

因為RS觸發器存在一種輸入在輸出的時候無法確認狀態,因此在使用的時候我們需要想辦法避免這種輸入的發生。

我們在輸入的R和S之間加入一個(非門),使得RS永遠不會相等,這樣就變成了一個最簡的D寄存器,D寄存器的D代表Data,可以實現數據的輸入。如上圖所示

相信大家已經發現,我們加入的(非門),雖然避免了RS觸發器輸出未知狀態的可能,但卻帶來了新的的問題,電路的保持功能同樣失效了,這意味著寫入數據的功能也變得毫無意義,一旦輸入信號撤走,或發生變化,電路輸出的結果也會跟著改變。

RS 觸發器輸入裝置

如何既要屏蔽未知輸出,又要不失去觸發器的保持功能呢?

我們需要給RS觸發器設計一個前置輸入裝置。

我們看真值表,對于(或非門)組成的RS觸發器,當RS同為0時,保持觸發器所存的數據。對 (與非門) 來說是RS同為1。因此我們用兩個(與門) 或者兩個 (與非門) 來實現這個功能,如上圖所示。

我們把(與門)或者(與非門)的一個輸入相連變成一個新的輸入,我們叫這個新的輸入CLK,根據(與門)和(與非門)的特點,我們給CLK輸入0時,(與門)的邏輯一定輸出兩個0,(與非門)的邏輯一定輸出兩個1。

再把(與門)和(與非門)的另一個輸入端之間放置一個(非門),(非門)的輸入我們叫他D。新裝置的真值表如下圖,這個裝置就能幫我們實現RS觸發器所有的有效輸入。

RS 觸發器輸入裝置

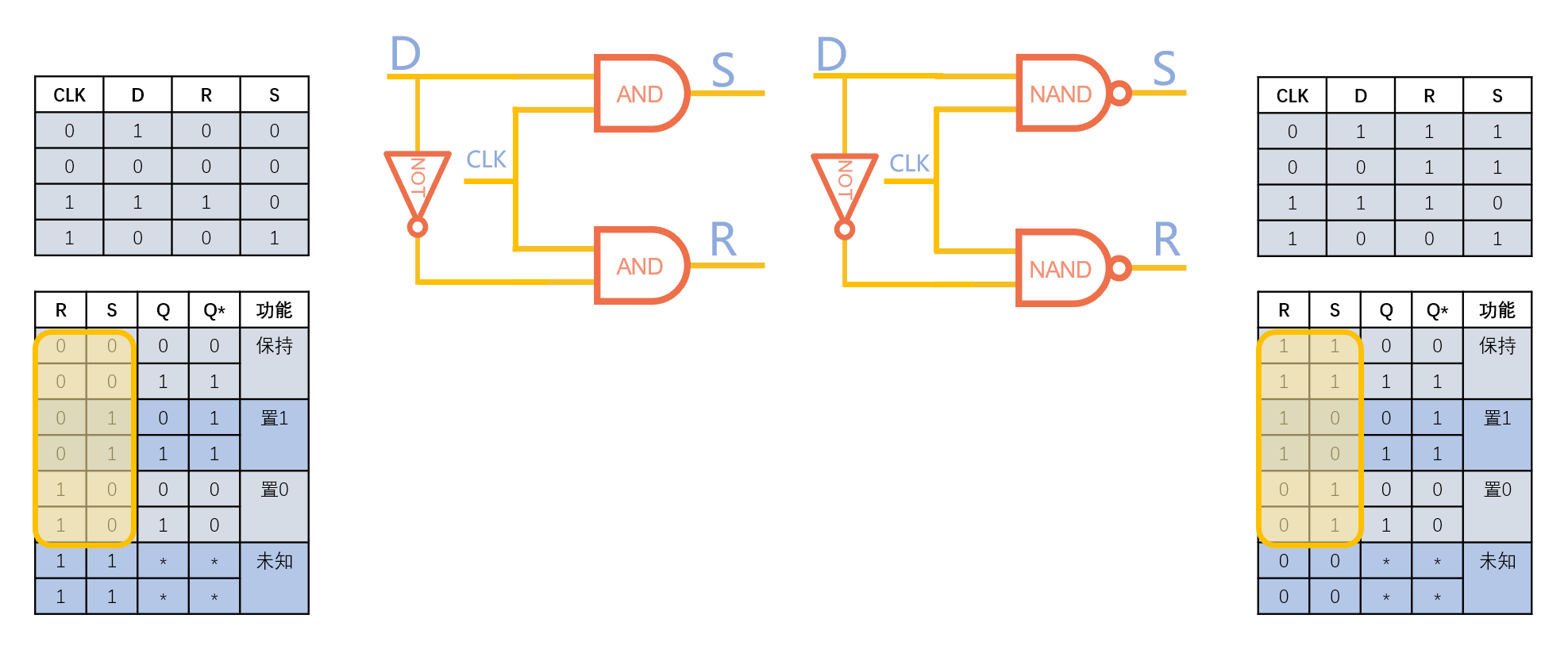

這時我們再把RS觸發器拿出來,放置在這個輸入裝置的后端,這樣就獲得了一個有實際用途的D觸發器。如下圖所示。

看一下用不同門組成的D觸發器和他們的真值表,仔細觀察下他們之間的差異。

我們可以發現,功能上他們是完全一樣的,電路上的差異,大家可以仔細端詳一下。

D觸發器有完整的讀寫控制能力,當CLK=0時,觸發器處于保存狀態,也就是無論這個時候D給出什么輸入,觸發器的內容不會變化。

當CLK=1的時候,D的值就會被寫入觸發器,完成寫操作。

CLK可以是時鐘信號,也可以是讀寫信號。

D觸發器

以上簡單的介紹了D觸發器。D觸發器實現了受控的數據存儲能力,并且速度非常快,類似CPU中的寄存器就可以由D觸發器來實現。

-

或非門

+關注

關注

0文章

21瀏覽量

15398 -

D觸發器

+關注

關注

3文章

164瀏覽量

48020 -

RS觸發器

+關注

關注

3文章

101瀏覽量

18042 -

觸發器

+關注

關注

14文章

2003瀏覽量

61347 -

與非門

+關注

關注

1文章

123瀏覽量

12814

發布評論請先 登錄

相關推薦

RS觸發器是什么?解讀rs觸發器的作用和數字電路中的rs觸發器的作用

一文詳解RS觸發器和D觸發器

一文詳解RS觸發器和D觸發器

評論