由于項(xiàng)目需要,小編使用Aurora核對(duì)數(shù)據(jù)進(jìn)行光纖傳輸,這篇文章主要介紹如何生成Aurora核、仿真上板測(cè)試。

一、Aurora IP建立

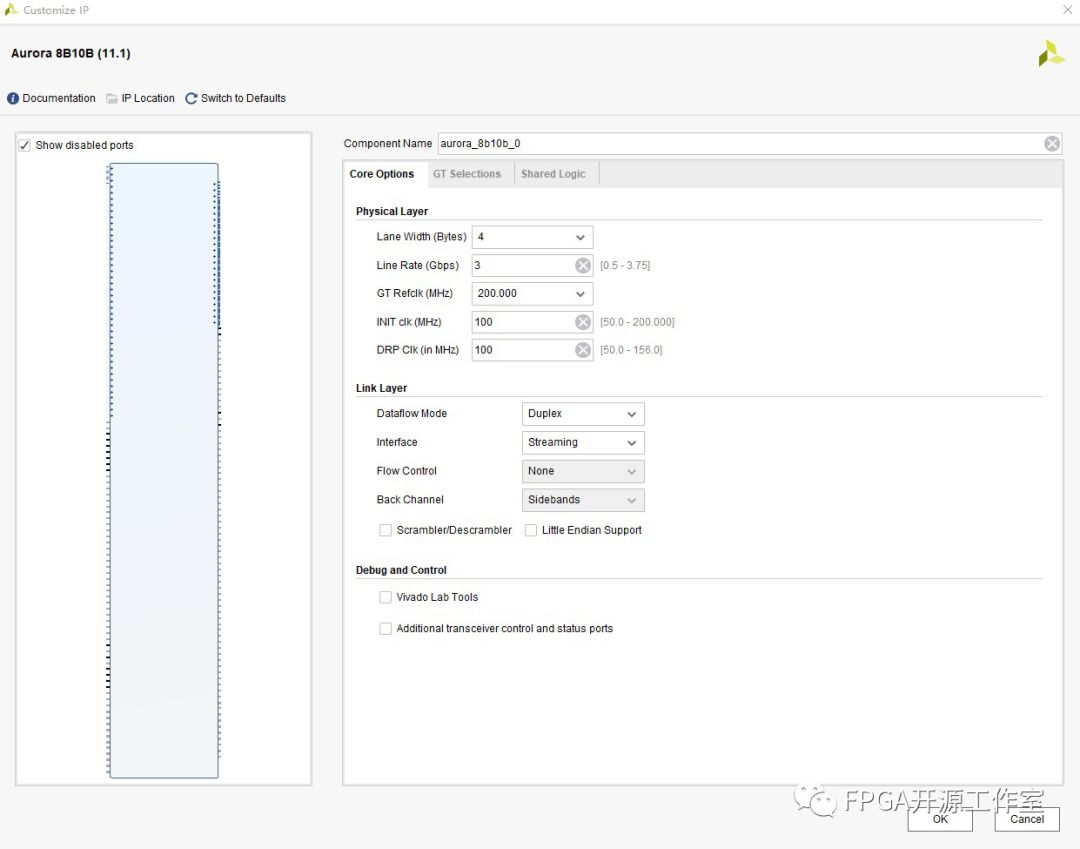

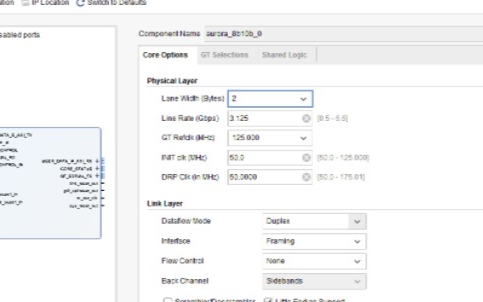

第一步

1》lane Width:用戶數(shù)據(jù)接口 4(32bit) 2(16bit)

2》Line Rate:3Gbps 假設(shè)圖像數(shù)據(jù)為1280x1024 @60 RGB(24bit),那么 1280 pixels/row x 1024 rows x 8bits/element gray scale x 3 elements/pixel x60 Hz refresh x 1.25 8b/10b x 1.05 (typical FC-AV protocol overhead) is approximately equal to 2.5 Gbps.

3》GT Refclk:200(此處查看板子原理圖即可)

4》INIT clk:100MHz

5》DRP clk:100MHz

上述兩個(gè)時(shí)鐘在參考范圍內(nèi)設(shè)置相同即可,本頁(yè)其他選項(xiàng)如圖設(shè)置即可 。

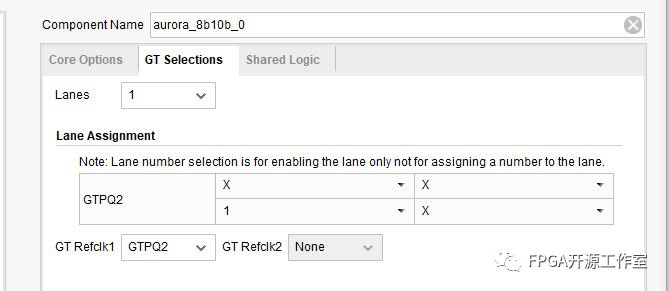

第二步

選擇高速串行通道的位置,默認(rèn)即可 。

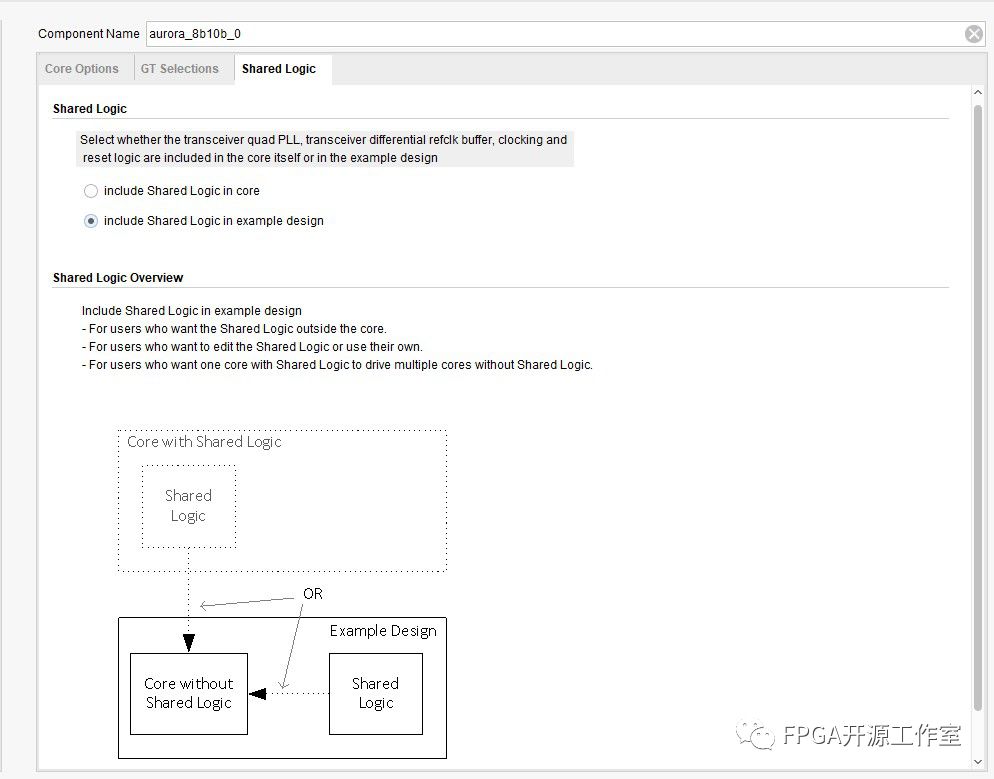

第三步

默認(rèn)即可。

二、仿真測(cè)試

在Vivado軟件中,我們生成好IP后可以可以打開帶有例子的工程,進(jìn)行仿真查看LANE_UP和CHANNEL_UP信號(hào)拉高后,即可認(rèn)為光纖通道初始化成功,在對(duì)其數(shù)據(jù)接口進(jìn)行查看,官方給的例程主要分為三大塊,數(shù)據(jù)產(chǎn)生模塊、光纖傳輸模塊、數(shù)據(jù)檢查模塊 。

三、上板測(cè)試(光纖初始化)

我們需要對(duì)INIT_CLK_P、INIT_CLK_N、DRP_CLK、GT_RESET_IN、RESET四個(gè)信號(hào)進(jìn)行修改。

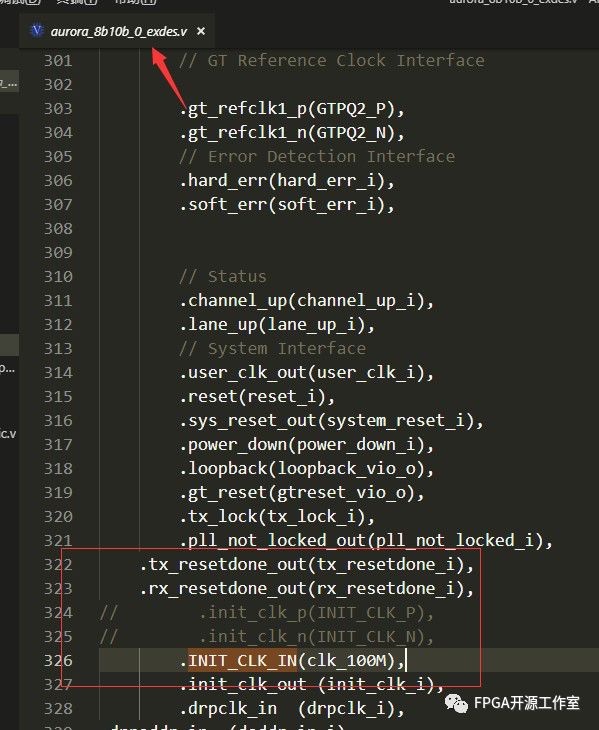

第一步

INIT_CLK_P、INIT_CLK_N:我們利用板子的單端輸入時(shí)鐘27M進(jìn)行pll倍頻出的100M提供給INIT_CLK_IN。

將aurora_8b10b_0_exdes文件做如下修改

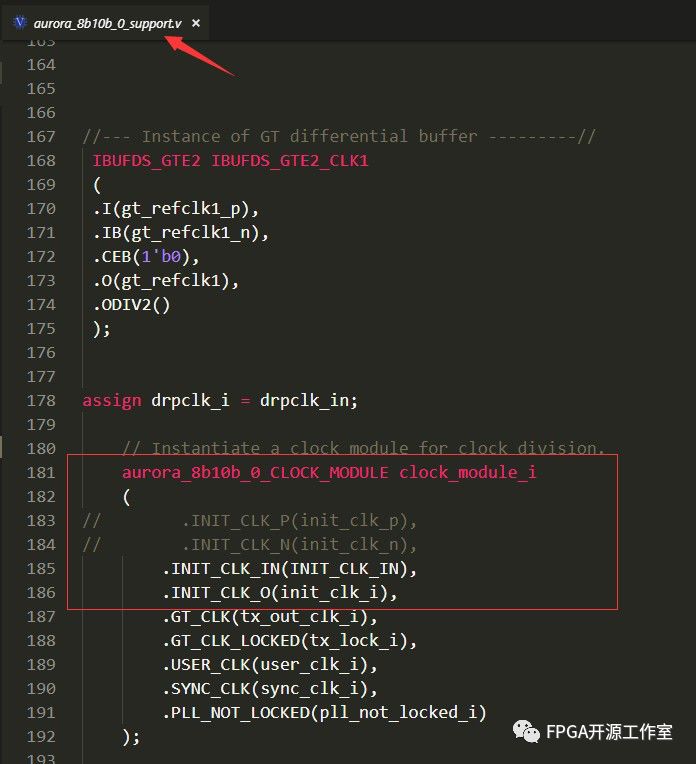

將aurora_8b10b_0_support文件做如下修改

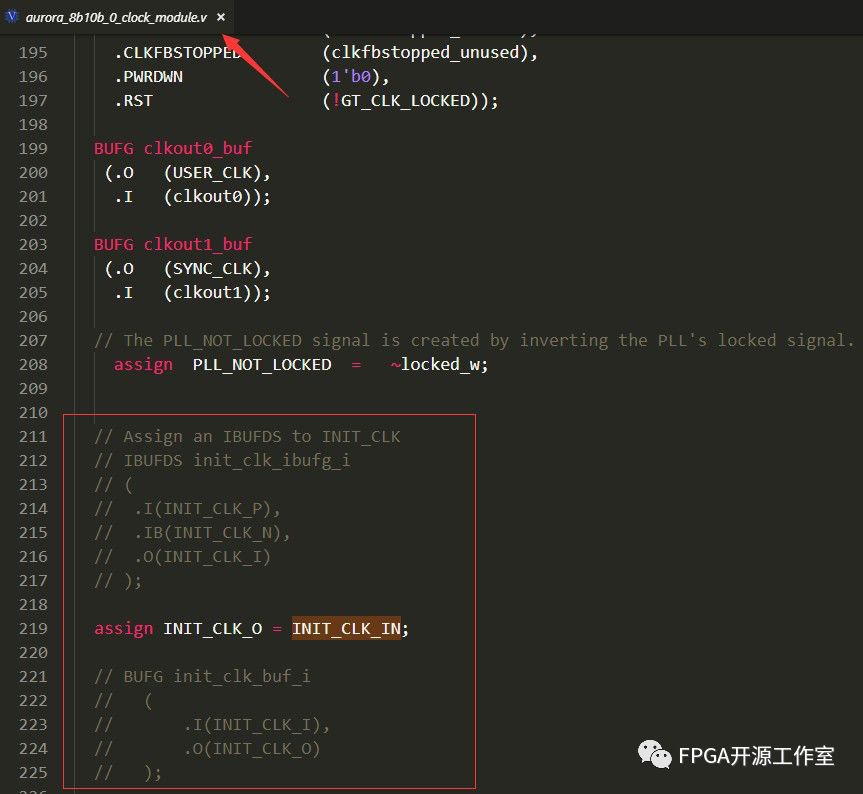

將aurora_8b10b_0_CLOCK_MODULE文件做如下修改

第二步

DRP_CLK:將倍頻出的100M時(shí)鐘輸入給DRP_CLK即可。

第三步

GT_RESET_IN、RESET:如果板子上有硬復(fù)位(低有效),對(duì)其取反賦給其即可,在頂層aurora_8b10b_0_exdes中修改。

assign RESET = ~sys_rst_n;

assign GT_RESET_IN = ~sys_rst_n;

第四步

如果我們板子上有指示燈,我們可以通過(guò)指示燈來(lái)查看是否初始化成功。在頂層aurora_8b10b_0_exdes中修改。

assign CHANNEL_UP_led = ~CHANNEL_UP;

assign LANE_UP_led = ~LANE_UP;

我們的指示燈是低電平亮,所以對(duì)其取反,上板燒寫例程代碼后可以看到兩個(gè)指示燈點(diǎn)亮,我們就可以認(rèn)為此時(shí)光纖核初始化成功。

學(xué)會(huì)使用Aurora核之后,那么我們就需要利用相關(guān)協(xié)議進(jìn)行傳輸,小編在本次項(xiàng)目中使用ARINC818協(xié)議

對(duì)數(shù)據(jù)進(jìn)行封裝,然后過(guò)光纖進(jìn)行傳輸,最后回傳到sdi芯片進(jìn)行顯示,開發(fā)者可根據(jù)項(xiàng)目需要選擇協(xié)議對(duì)數(shù)據(jù)進(jìn)行傳輸。

審核編輯 :李倩

-

仿真

+關(guān)注

關(guān)注

50文章

4124瀏覽量

133986 -

光纖通道

+關(guān)注

關(guān)注

0文章

224瀏覽量

14159

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

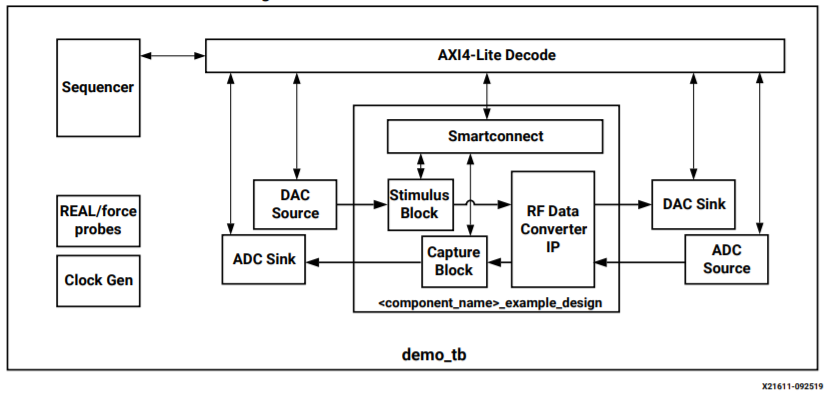

RF Data Converter IP設(shè)計(jì)仿真測(cè)試激勵(lì)文件原理

【米爾-Xilinx XC7A100T FPGA開發(fā)板試用】+04.SFP之Aurora測(cè)試(zmj)

Aurora 8b/10b IP核問(wèn)題

GTY 100G Aurora IP的一些問(wèn)題

Aurora IP 8b10b如何生成bitfile?

用于26Km光纜的Aurora IP v11.0通道上行/上行故障的解決辦法?

如何使用Aurora 8B / 10B建立僅傳輸?

怎么禁用Aurora IP Core 8B / 10B中的時(shí)鐘補(bǔ)償功能?

40Gbs交換IP軟核驗(yàn)證和測(cè)試

一種新的IP仿真測(cè)試平臺(tái)的實(shí)現(xiàn)

Aurora OS是個(gè)什么來(lái)頭?

Xilinx平臺(tái)Aurora IP介紹(三)Aurora配置及接口

Xilinx平臺(tái)Aurora IP介紹(一)Aurora基礎(chǔ)知識(shí)

Aurora IP建立仿真及測(cè)試

Aurora IP建立仿真及測(cè)試

評(píng)論