功耗分析和優化在最近幾年逐漸引起了人們的重視,大多數 IC 設計團隊現在都會為了功耗管理在自己的流程中納入功率管理步驟和工具。盡管如此,功耗分析任務往往要基于驗證場景,而這些場景過于基礎,并且與實際系統使用完全脫節。

本白皮書將解釋說明,使用真實的有效載荷為何對于準確估算功耗和執行優化任務而言至關重要。之后,我們將會展示Veloce客戶如何使用硬件加速仿真來實現可靠性高得多的使用模型,并且利用這一模型,可以更可靠地識別和分析潛在的功耗問題。

有效矢量的激勵

在功耗方面,設計人員有著許多不同的目標和關注點。一方面,團隊需要確保其芯片的平均功耗足夠低,以保證延長電池的續航時間。另一方面,團隊的主要關注點可能是預防出現局部感性電壓降,該電壓降會破壞芯片的功能。但不論哪種情況,使用不夠真實的矢量執行任何分析都會導致所得的結論和決定不正確。

功率估算

其中一個使用最普遍的功耗分析任務是估算整個芯片在較長時段內的平均功耗。執行此任務的目的通常是確保憑借低能耗芯片保證延長電池續航時間,節省能源費用和/或簡化散熱方案,從而獲得競爭優勢。很顯然,通過仿真生成有代表性的有效載荷可能變得極具挑戰性,而且很多設計人員都會采用分而治之的方法,這種情況下,他們可以收集不同子模塊的數據并組合在一張電子表格中。這種方法是否值得信賴,這是設計團隊在從制造廠取回自己的芯片之前苦思冥想的一個問題。

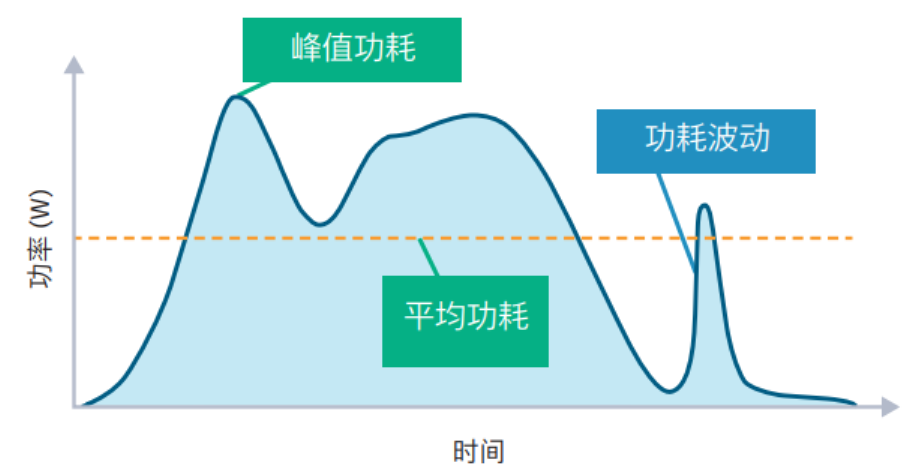

圖 1. 不同類型的功率估算。

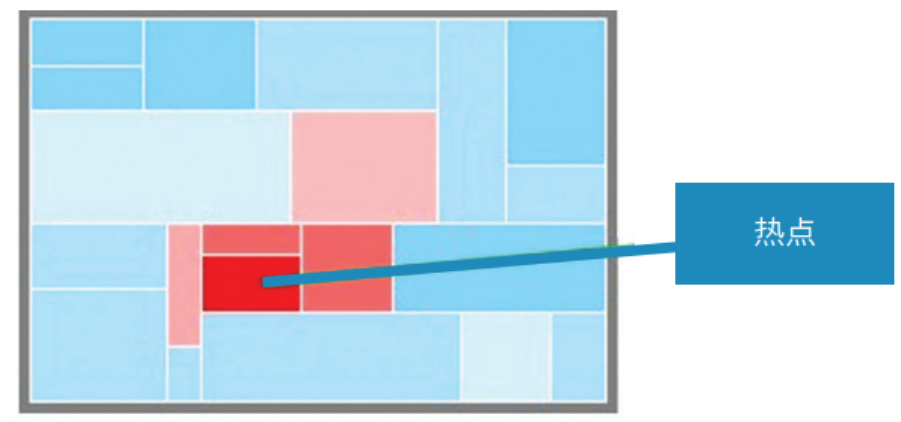

而在其他情況下,人們關注的是峰值功耗(圖 1)。關于峰值功耗,根據問題的性質,必要的分析可能因空間和時間范圍而大相徑庭。舉個例子,問題可能出在一個局部的快速現象,例如可能在一個時鐘周期內發生的電壓降(阻性或感性)。或者,也可能是更全局性的問題,例如當電流高于給定閾值的時間超過一定時間(譬如說幾毫秒)時所導致的電源完整性違規等。如果關注的是散熱問題,需要識別的峰值還可能分布在較寬的范圍。而且,如果空間范圍小于整個 SoC,則設計人員將需要識別局部熱點,并執行層次化或基于底層規劃的分析(圖 2)。

圖 2. 局部熱點識別。

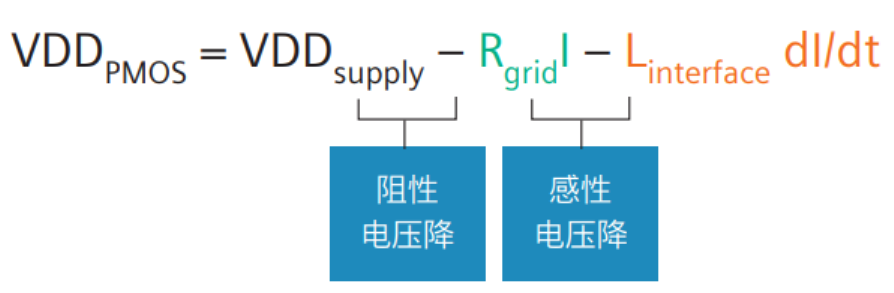

最后,除了空間和時間范圍考慮之外,有時設計人員感興趣的不僅僅是功耗水平,還有變化率。這是因為在高級技術節點,電壓降的感性分量會變得與阻性分量一樣關鍵(圖 3)。

圖 3. 電壓降類型。

降低功耗

除以上所列的全部功率估算目標之外,使用有代表性的活動數據對于相關的功耗驗證和優化任務也是至關重要的。例如,可以考慮一個非常復雜的 SoC 情形,其中往往可以看到幾十個電源域(其中一些使用保留策略)和復雜的時鐘方案。這種情形下,特別當功率控制器是基于軟件時,能否以統一功率格式 (UPF) 的形式考量實際系統使用并解釋功耗意圖,對于完整的功耗驗證非常關鍵。

要在 RTL 中降低功耗,也是如此。降低功耗所用的大多數(即使不是全部)方法對于信號層的活動水平估算非常敏感。確定是否應該直接對數據門控或時鐘門控運用穩定性或可觀測性條件取決于出現這類條件的概率。因此,設計人員在接受工具自動建議或實施的修改之前,需要考慮真實的系統有效載荷。

審核編輯:湯梓紅

-

芯片

+關注

關注

456文章

51192瀏覽量

427305 -

IC設計

+關注

關注

38文章

1302瀏覽量

104289 -

仿真

+關注

關注

50文章

4124瀏覽量

133999 -

硬件

+關注

關注

11文章

3382瀏覽量

66456 -

功耗

+關注

關注

1文章

828瀏覽量

32080

原文標題:使用硬件加速仿真進行有意義的功耗分析

文章出處:【微信號:Mentor明導,微信公眾號:西門子EDA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

高通收購NXP真的有意義嗎?

MCU廠推多樣解決方案 DSP/FPU硬件加速芯片整合

橫河測量測試 對于要求較高的測試應用,非常有意義

請問stm32f103zet6搭配256Mbit SDRAM有意義嗎?

Mentor Graphics硬件加速仿真服務使用Veloce 硬件加速仿真平臺加速驗證

Mentor Graphics Veloce 硬件加速仿真平臺協助 Barefoot Networks 驗證全球首個完全可編程開關

MD5算法硬件加速模型

憶芯科技利用Veloce 硬件加速仿真平臺進行高速企業級固態硬盤存儲設計

Veloce仿真環境下的SoC端到端硬件加速器功能驗證

使用硬件加速仿真的功耗分析

基于Arduino的矯枉過正但具有意義的COVID流行病展示

使用硬件加速仿真進行有意義的功耗分析

使用硬件加速仿真進行有意義的功耗分析

評論