如果SoC設計規模小,在單個FPGA內可以容納,那么只要系統中的FPGA具有所SoC所設計需要時鐘的數量,SoC時鐘網絡將由FPGA中的復雜時鐘網絡來解決,包括PLL、時鐘分頻、倍頻以及本地時鐘和全局時鐘之間的同步。 一旦SoC設計規模很大,必須跨多個FPGA進行分區,則時鐘方案的復雜性就上來了。

實際上,整個原型驗證系統的時鐘網絡結構的頂層需要由FPGA原型驗證系統板級解決,而不是在FPGA芯片內部解決,因為不同FPGA芯片內部的時鐘源很難做到同步。我們可以將整個FPGA原型驗證系統的硬件電路板視為“超級FPGA”,是一個更加宏觀的系統,由FPGA加上將它們連接到整體平臺中的頂級時鐘資源連合組成。

要在原型驗證系統的電路板級復制FPGA的時鐘功能的完整層次結構,需要與每個FPGA內部的資源類似的資源。例如,我們需要板級PLL、時鐘復用、時鐘分頻器和乘法器、時鐘同步電路等等。

在許多情況下,我們可以通過使用工具或者技巧將SoC系統中的時鐘簡化為在FPGA原型驗證系統電路板上處理的時鐘來簡化這一需求。例如,將SoC設計的一些門控時鐘轉換為等效的全局FPGA時鐘,加上和此同源關系的時鐘啟用,以減少時鐘域的總數。這種門控時鐘轉換可以在不改變RTL的情況下自動進行。

將靈活的時鐘資源構建到一個FPGA原型驗證系統的電路板中,以滿足各種SoC設計的要求,需要大量的經驗和專業知識。電路板僅使用時鐘源和映射特定SoC設計所需的其他資源,這肯定比為所有基于FPGA的原型驗證完全靈活使用要容易得多。然而,如果設計在項目期間發生某種程度的變化,時鐘資源靈活性不足的母板將對分區決策造成更大的限制。

這也將大大降低整個FPGA原型驗證系統電路板在多個項目中使用的能力,因為一個SoC項目的時鐘資源可能與后續項目的時鐘資源不匹配,我們需要的是一個通用的原型驗證平臺。

板間匹配時鐘延遲

SoC中的時鐘系統將在實際流片的芯片中實現,并對時鐘分配延遲進行嚴格控制和分析。當這樣的SoC系統被拆分到多個FPGA時,我們不能在系統FPGA時鐘網絡中引入偏差。將SoC設計劃分為多個FPGA,那么就需要控制FPGA間延遲,特別是如果要使用多個FPGA平臺板間級聯,則需要控制板間延遲。

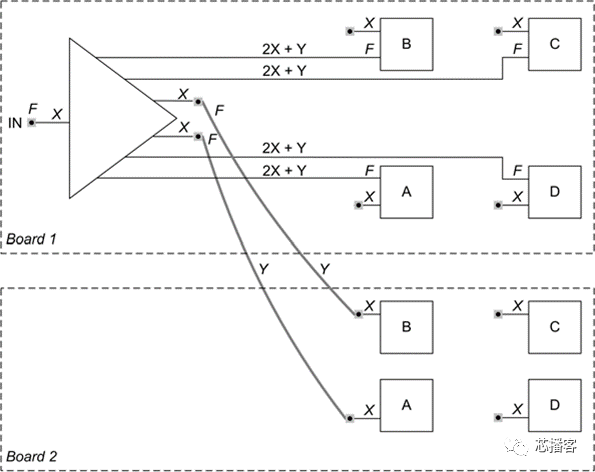

其中一些可以通過適當地限制FPGA工具來完成,并且可以通過降低原型的總體目標時鐘速度來簡化任務。然而,無論時鐘速度如何,減輕這一任務的最佳方法是設計具有匹配和可預測時鐘分布資源的板級電路。作為延遲匹配的一個例子,我們看SynopsysHAPS系列電路板。這些都是用延遲量來布置的,這些延遲量在時鐘分布路徑的關鍵點處重復。

延遲X和Y,它們在電路板設計期間用作基本值。Y是典型時鐘沿具有高質量屏蔽和同軸連接器的特定標準長度同軸電纜的延遲,該同軸電纜大量生產并廣泛用于基于HAPS的平臺。具有相對恒定延遲的單一類型和長度的電纜意味著板載可以設計為相同值Y。

對于PCB設計者來說,延遲電路板上的匹配是一件小事,盡管采用的Z字形跡線布線可能會增加對額外電路板布線層的需求。另一個延遲量X是FPGA引腳和附近連接器之間的線延遲,保持恒定相對簡單。X和Y的值將是給定系列電路板的特征值,例如,對于一系列電路板,X=0.44ns,Y=1.45ns。

小心地,可以在新電路板設計中保持X和Y值,以便在同一原型中更容易地混合舊電路板和新電路板。我們現在可以從圖中看到,時鐘源和任何FPGA時鐘引腳之間的時鐘延遲將是相同的值,2X+Y。

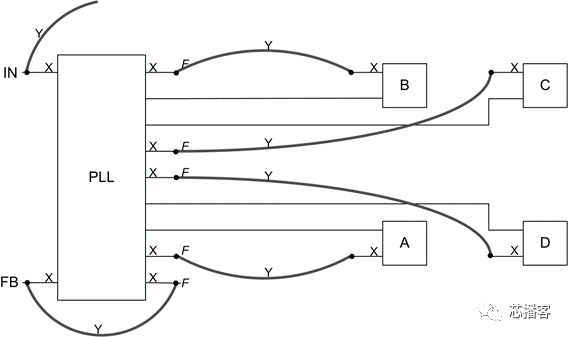

PLL對于消除交叉板時鐘中的插入延遲非常有用

網絡可以減少原型不同部分之間的時鐘偏差。圖中顯示了驅動四個FPGA的板級PLL。通過使用長度匹配,可以使每個FPGA時鐘輸入端的短截線和PLL輸出端的短截線等于值X。

在生產運行中,X的絕對值可能會變化,但對于任何給定的電路板都足夠一致。另外,FPGA通過等長電纜或延遲Y連接到PLL輸出。強烈建議使用同軸電纜和高保真時鐘連接,以獲得最佳可靠性和性能。

我們可以看到從PLL到每個FPGA的板上延遲是匹配的。為了在“超級FPGA”的頂層提供必要的時鐘資源,電路板應包括PLL功能,這對于許多任務都很有用。盡管所使用的FPGA可能包括其自己的PLL功能,但電路板應包括分立的PLL設備,例如從眾多供應商商購的那些。

系統時鐘生成

一旦了解FPGA原型驗證系統中的可用時鐘資源,我們應該確定哪些額外的外部時鐘源并正確利用它們,并為所有未來應用保持最大的靈活性。 時鐘來源于哪里?FPGA板上的時鐘源生成。主板外部時鐘源。在FPGA中的時鐘源生成。

需要什么時鐘速率?估計可能的FPGA時鐘頻率范圍。計劃生成具有一定精度的任意時鐘速率。 可以容忍什么樣的時鐘偏移?FPGA間同步:確保所有FPGA以可接受的偏差接收時鐘源。板間同步:在大型系統中,確保所有時鐘以可接受的偏差到達所有FPGA。

在解決上述問題時,通常可能包括以下大部分或全部要素:

板載時鐘合成:通常是由晶振參考驅動的PLL,具有可配置的參數以選擇所需的時鐘頻率。為了增加靈活性,晶振是可移除的。可能需要多個時鐘發生器來支持具有多個時鐘的系統。

輸入時鐘源選擇器:考慮到可以從中獲取時鐘的多個源,例如本地(板上、FPGA)或外部,應實現時鐘源多路復用器。多路復用器的管理可以通過手動開關進行,也可以通過單獨的軟件實用程序進行編程。

時鐘分布:無論時鐘源如何,時鐘分布必須確保時鐘以可接受的偏差在整個FPGA系統當中。過度偏斜可能會導致不正確的邏輯傳播,并降低兩個或多個FPGA或子系統之間的的裕度,從而將同步信號傳遞給彼此。在保持可接受的信號質量的同時,必須考慮和均衡板間和連接器延遲。

外部時鐘源:必須考慮從一個FPGA板到另一個FPGA板的傳播延遲,并且應通過適當的相移來均衡傳播延遲。必須特別注意在時鐘路徑的源和目標之間級聯多個PLL的情況,因為如果設計不當,可能會發生不穩定和鎖不住穩定時鐘的情況。

特殊的高速時鐘:除了應用時鐘之外,可能需要高速時鐘在一個引腳上多路復用多個信號。這通常在兩個FPGA之間的信號數量大于它們之間的可用引腳數量時使用。使用高速時鐘,信號可以在源端的單個引腳上進行時間復用,然后在接收端進行解復用。為了使該方案正常工作,接口的兩側必須具有相同的高速時鐘,且偏差最小。

時鐘分頻與倍頻:時鐘的靈活性要求頂級時鐘可以縮放到設計各個部分的正確頻率。雖然分頻器和其他邏輯資源可以在FPGA設備內部用于此,但PLL也有其作用。

審核編輯:劉清

-

FPGA設計

+關注

關注

9文章

428瀏覽量

26632 -

分頻器

+關注

關注

43文章

447瀏覽量

50074 -

SoC芯片

+關注

關注

1文章

617瀏覽量

35040 -

乘法器

+關注

關注

8文章

206瀏覽量

37193 -

時鐘網絡

+關注

關注

0文章

16瀏覽量

6583

原文標題:FPGA原型驗證系統的時鐘資源

文章出處:【微信號:于博士Jacky,微信公眾號:于博士Jacky】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

驗證中的FPGA原型驗證 FPGA原型設計面臨的挑戰是什么?

ASIC設計-FPGA原型驗證

高頻RFID芯片的FPGA原型驗證平臺設計及驗證

基于FPGA原型的GPS基帶驗證系統設計與實現

FACE-VUP:大規模FPGA原型驗證平臺

FPGA開發板vs原型驗證系統

FPGA原型驗證系統的時鐘資源設計

FPGA原型驗證系統的時鐘資源設計

評論