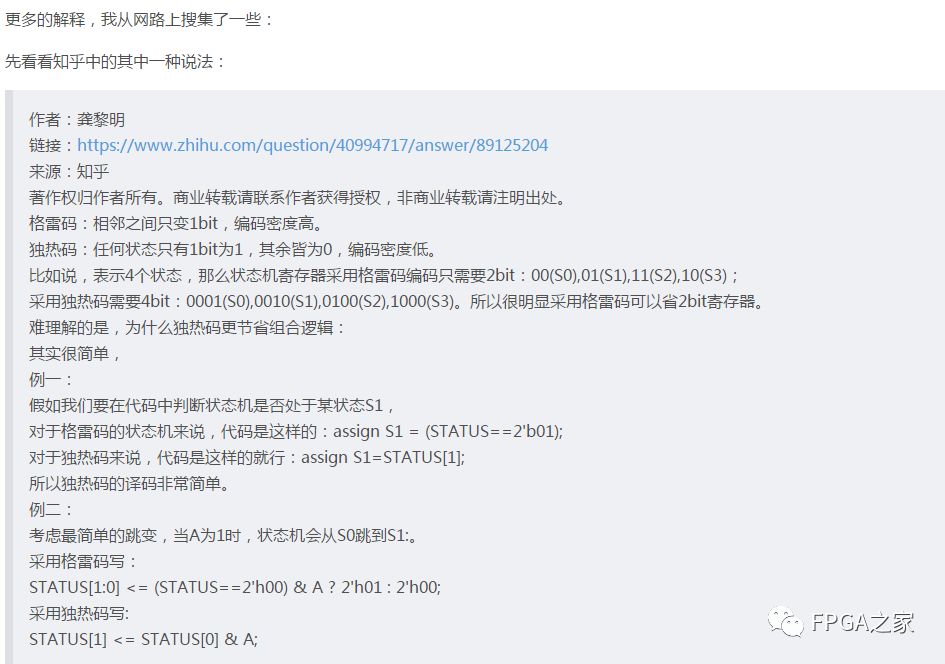

看《從算法設(shè)計(jì)到硬件邏輯的實(shí)現(xiàn)》這本電子書(shū)時(shí),遇到了一個(gè)問(wèn)題,就是有限狀態(tài)機(jī)的編寫(xiě)中,狀態(tài)編碼是采用格雷碼還是獨(dú)熱碼呢?究竟采用哪一種編碼呢?

采用獨(dú)熱碼為什么節(jié)省許多組合電路?

等等問(wèn)題,就這些問(wèn)題我收集了一些說(shuō)法,覺(jué)得很有意思,在這里我們一起討論下。

還是先簡(jiǎn)介下有限狀態(tài)機(jī):

有限狀態(tài)機(jī)是由寄存器組和組合邏輯構(gòu)成的硬件時(shí)序電路,其狀態(tài)(即由寄存器組的1和0的組合狀態(tài)所構(gòu)成的有限個(gè)狀態(tài))只可能在同一時(shí)鐘跳變沿的情況下才能從一個(gè)狀態(tài)轉(zhuǎn)向另一個(gè)狀態(tài),究竟轉(zhuǎn)向哪一狀態(tài)還是留在原狀態(tài)不但取決于各個(gè)輸入值,還取決于當(dāng)前所在狀態(tài)。這里是指Mealy型有限狀態(tài)機(jī)。

Moore型有限狀態(tài)機(jī)的狀態(tài)轉(zhuǎn)移只取決于當(dāng)前狀態(tài),與輸入值無(wú)關(guān)。

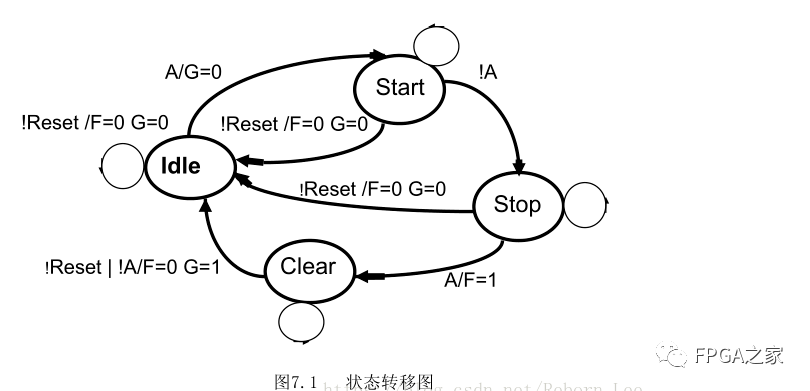

在Verilog HDL中可以用許多種方法來(lái)描述有限狀態(tài)機(jī),最常用的方法是用always語(yǔ)句和case語(yǔ)句。下面的狀態(tài)轉(zhuǎn)移圖表示了一個(gè)有限狀態(tài)機(jī):

上面的狀態(tài)轉(zhuǎn)移圖表示了一個(gè)四狀態(tài)的有限狀態(tài)機(jī),它的同步時(shí)鐘是Clock,輸入信號(hào)是 A 和 rst_n ,輸出信號(hào)是 F 和 G。狀態(tài)的轉(zhuǎn)移只能在同步時(shí)鐘(Clock)的上升沿時(shí)發(fā)生,往哪個(gè)狀態(tài)的轉(zhuǎn)移則取決于目前所在的狀態(tài)和輸入的信號(hào)(Reset 和 A)。

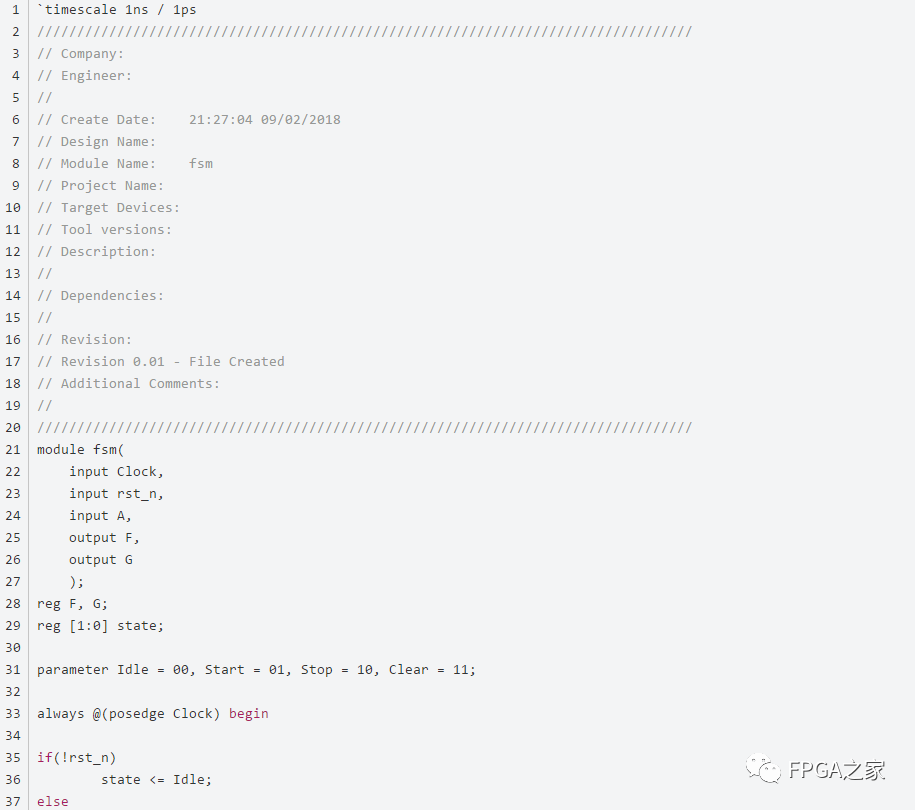

我們采用兩種狀態(tài)編碼方式來(lái)實(shí)現(xiàn)這個(gè)有限狀態(tài)機(jī):

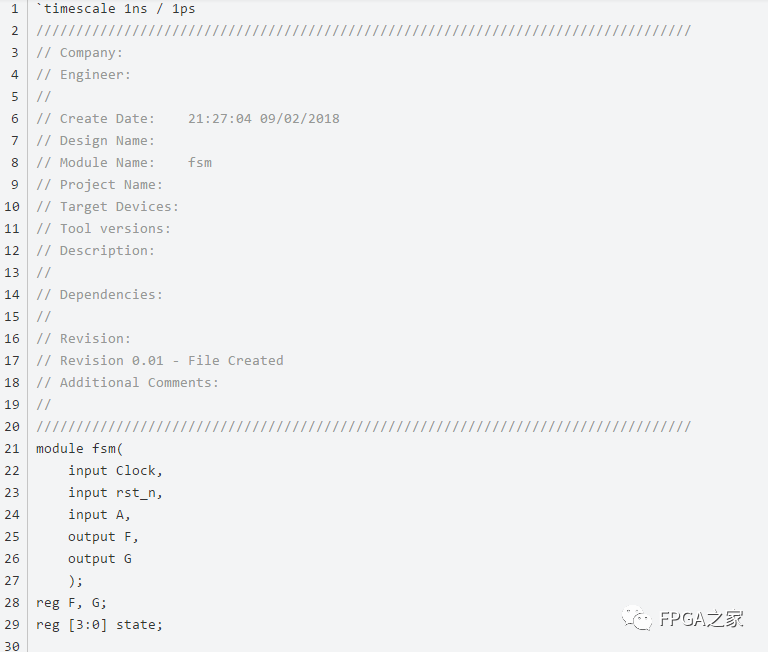

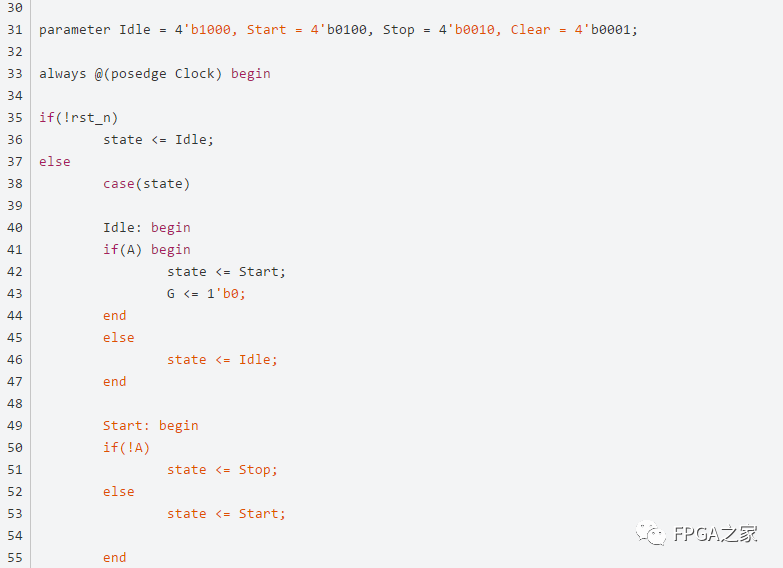

1)采用格雷碼:

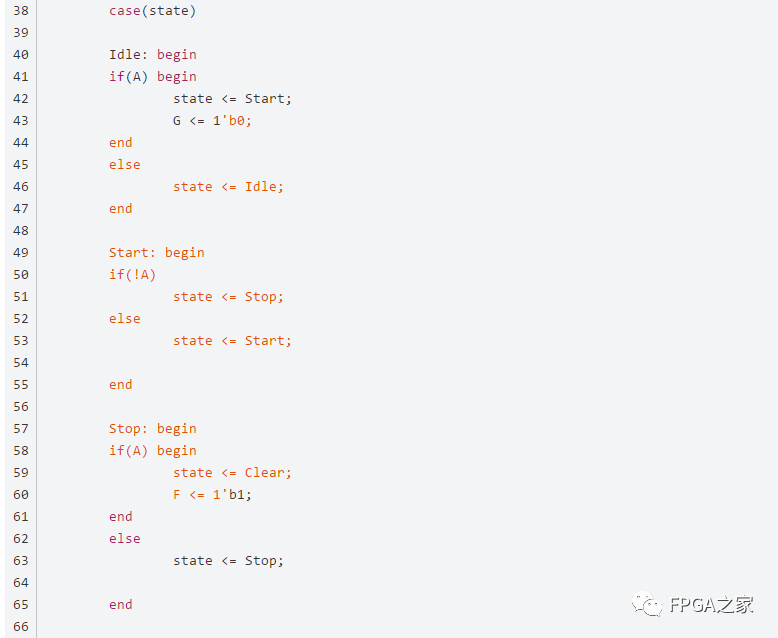

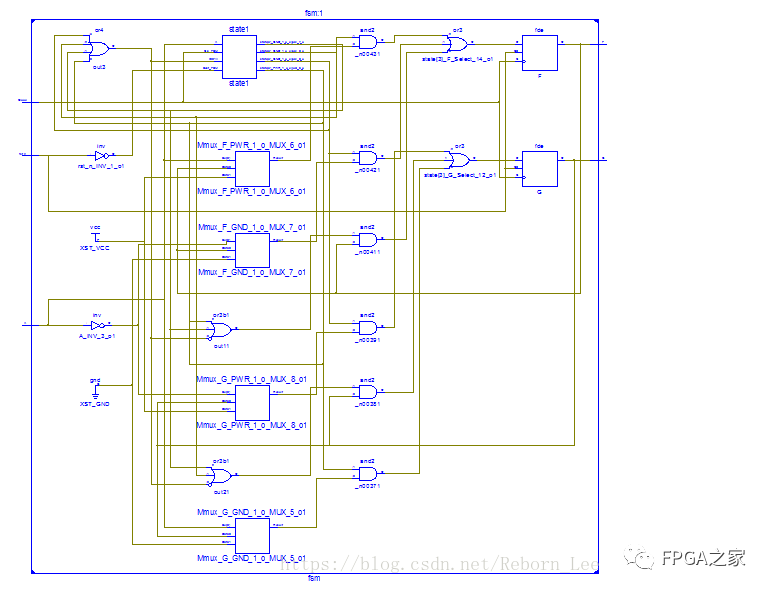

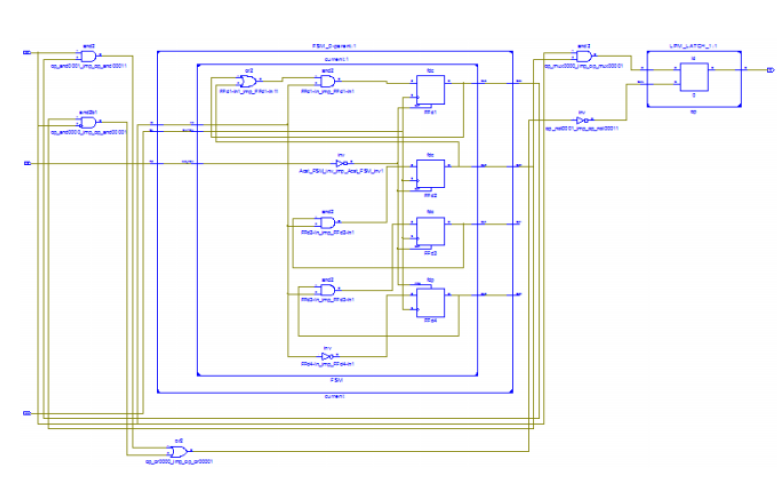

在ISE中,綜合后,得到的RTL Schematic:

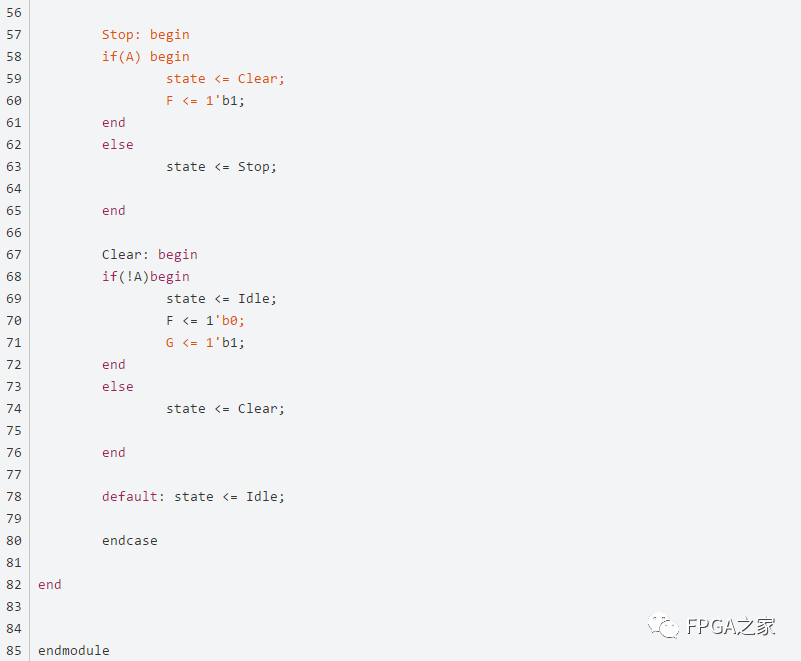

2)采用獨(dú)熱碼:

程序和上面的幾乎一樣,只需要改下,各個(gè)狀態(tài)對(duì)應(yīng)的編碼值即可,還有最后的default:state 《= Idle;

還是給出程序吧:

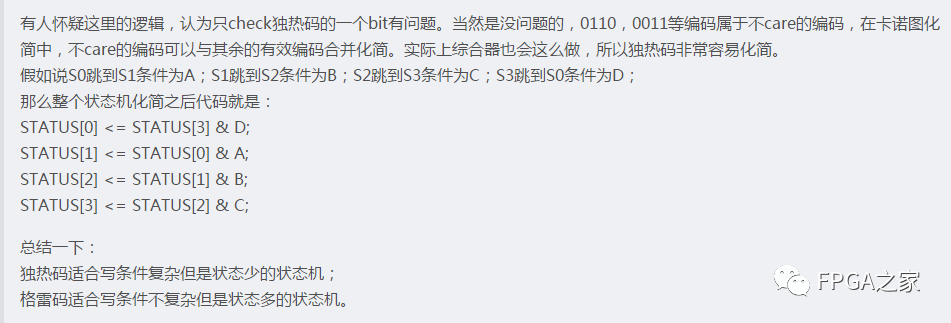

上面兩個(gè)程序的主要不同點(diǎn)是狀態(tài)編碼,2)采用了獨(dú)熱編碼,而1)則采用Gray碼,究竟采用哪一種編碼好要看具體情況而定。對(duì)于用FPGA實(shí)現(xiàn)的有限狀態(tài)機(jī)建議采用獨(dú)熱碼,因?yàn)殡m然采用獨(dú)熱編碼多用了兩個(gè)觸發(fā)器,但所用組合電路可省下許多,因而使電路的速度和可靠性有顯著提高,而總的單元數(shù)并無(wú)顯著增加。采用了獨(dú)熱編碼后有了多余的狀態(tài),就有一些不可到達(dá)的狀態(tài),為此在CASE語(yǔ)句的最后需要增加default分支項(xiàng),以確保多余狀態(tài)能回到Idle狀態(tài)。

上面所說(shuō)的多余狀態(tài)是:4位編碼有16種,獨(dú)熱碼只列出了4種,剩下了12種,就是多余的狀態(tài)。

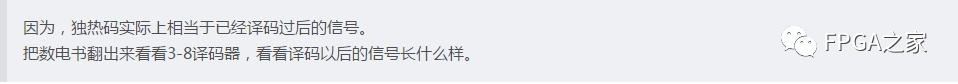

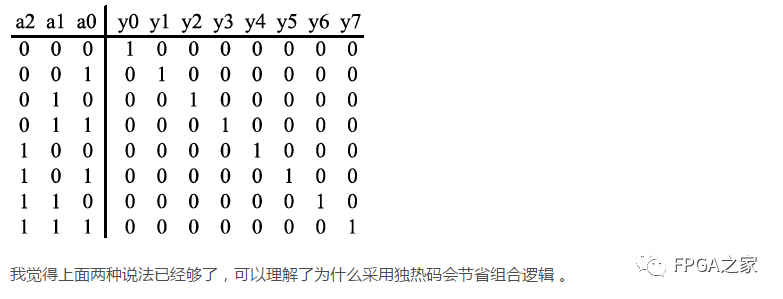

另一位大牛只說(shuō)了一句話,但很有啟發(fā):

那我把3—8譯碼器的真值表給出來(lái),確實(shí)如此。

審核編輯 :李倩

-

FPGA

+關(guān)注

關(guān)注

1630文章

21796瀏覽量

605996 -

寄存器

+關(guān)注

關(guān)注

31文章

5363瀏覽量

121158 -

輸出信號(hào)

+關(guān)注

關(guān)注

0文章

291瀏覽量

11936

原文標(biāo)題:FPGA中有限狀態(tài)機(jī)的狀態(tài)編碼采用格雷碼還是獨(dú)熱碼?

文章出處:【微信號(hào):FPGA研究院,微信公眾號(hào):FPGA研究院】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

FPGA設(shè)計(jì)的獨(dú)熱碼的使用和調(diào)試技巧的詳細(xì)概述

FPGA Verilog HDL 設(shè)計(jì)實(shí)例系列連載--------有限狀態(tài)機(jī)設(shè)計(jì)

為什么相對(duì)于格雷碼來(lái)說(shuō),獨(dú)熱碼會(huì)使用更多的觸發(fā)器和更少的組合邏輯???

【FPGA開(kāi)源教程連載】第七章 狀態(tài)機(jī)設(shè)計(jì)實(shí)例

fpga Default Latch FPGA設(shè)計(jì)的獨(dú)熱碼的使用和調(diào)試技巧的詳細(xì)概述

有限狀態(tài)機(jī)有什么類(lèi)型?

有限狀態(tài)機(jī)的建模與優(yōu)化設(shè)計(jì)

VHDL有限狀態(tài)機(jī)設(shè)計(jì)-ST

初學(xué)者對(duì)有限狀態(tài)機(jī)(FSM)的設(shè)計(jì)的認(rèn)識(shí)

如何使用FPGA實(shí)現(xiàn)序列檢測(cè)有限狀態(tài)機(jī)

FPGA中有限狀態(tài)機(jī)的狀態(tài)編碼采用格雷碼還是獨(dú)熱碼?

FPGA中有限狀態(tài)機(jī)的狀態(tài)編碼采用格雷碼還是獨(dú)熱碼?

評(píng)論