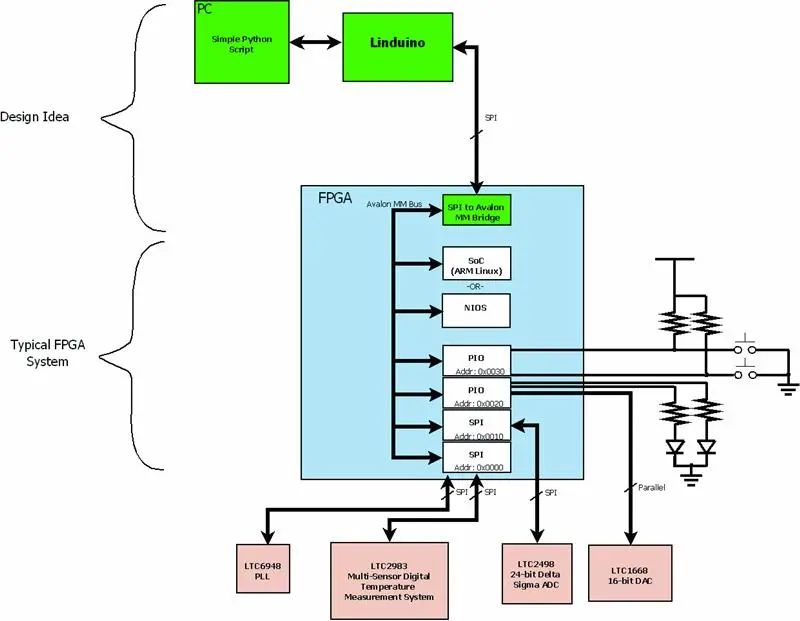

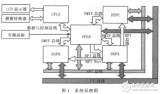

許多 FPGA 設(shè)計(jì)使用嵌入式處理器進(jìn)行控制。一個(gè)典型的解決方案涉及使用 Nios 等軟處理器,盡管帶有內(nèi)置硬處理器的 FPGA SoC 也變得很流行。圖 1顯示了一個(gè)典型的 Altera FPGA 系統(tǒng),它包含處理器和通過(guò) Altera 的Avalon內(nèi)存映射 (MM) 總線(xiàn)連接的混合外設(shè) 。這些處理器大大簡(jiǎn)化了終應(yīng)用程序,但需要強(qiáng)大的編程背景和復(fù)雜工具鏈的知識(shí)。這會(huì)阻礙調(diào)試,特別是如果硬件工程師需要一種簡(jiǎn)單的方法來(lái)讀取和寫(xiě)入外圍設(shè)備而無(wú)需糾纏軟件工程師。

圖 1 使用 Avalon 內(nèi)存映射總線(xiàn)連接的典型 Altera FPGA 系統(tǒng)

該設(shè)計(jì)理念使用 Altera 的SPI 從器件到 Avalon MM 橋接器來(lái)提供跳到 Avalon 總線(xiàn)上的簡(jiǎn)單方法。這種技術(shù)有兩個(gè)優(yōu)點(diǎn):它不損害原來(lái)的系統(tǒng)設(shè)計(jì),橋可以與嵌入式處理器共存。對(duì)于圖 1所示的系統(tǒng),SPI 橋允許工程師直接控制 LTC6948 小數(shù) N PLL 的頻率,設(shè)置 LTC1668 DAC 電壓,從 LTC2498 ADC 讀取電壓,或從 LTC2983 讀取溫度,就像處理器可以。

Altera 為 SPI-Avalon MM 橋接器提供參考設(shè)計(jì)。不幸的是,文檔充其量是稀疏的,并且使用 Nios 處理器作為 SPI 主機(jī)。這實(shí)際上違背了 SPI 橋的目的,因?yàn)?Nios 可以直接連接到 Avalon MM 總線(xiàn)。一個(gè)實(shí)用的 SPI 主控制器是凌力爾特的Linduino 微控制器,它是一個(gè) Arduino 克隆,具有連接到 LT 演示板的額外功能。一項(xiàng)額外功能是電平轉(zhuǎn)換 SPI 端口。當(dāng)連接到電壓低至 1.2V 的 FPGA I/O bank 時(shí),這種電平轉(zhuǎn)換功能特別有用。Linduino 固件可用于通過(guò)虛擬 COM 端口接受命令并將命令轉(zhuǎn)換為 SPI 事務(wù)。

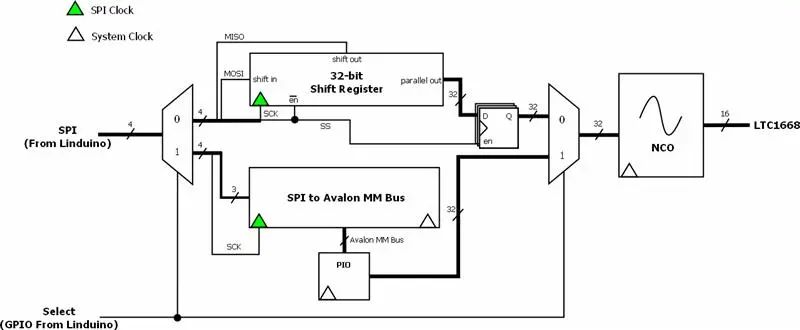

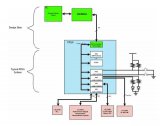

在對(duì) Altera 示例設(shè)計(jì)(圖 2的左側(cè))進(jìn)行逆向工程后,開(kāi)發(fā)了一個(gè) Python 庫(kù)來(lái)創(chuàng)建網(wǎng)橋可以接受的數(shù)據(jù)包。然后將這些數(shù)據(jù)包翻譯成 Linduino 命令。然后,Python 腳本允許硬件工程師完全控制項(xiàng)目,而無(wú)需重新發(fā)明接口協(xié)議。LinearLabTools Python 文件夾中提供了一個(gè)示例 Python 腳本,用于控制 LTC1668 DAC 的數(shù)字模式發(fā)生器的頻率。圖 3顯示了演示設(shè)置。

圖 4顯示了系統(tǒng)框圖。請(qǐng)注意,數(shù)控振蕩器 (NCO) 可由移位寄存器或 PIO 內(nèi)核控制。包含移位寄存器用于調(diào)試,因?yàn)樗试S直接控制 NCO。將 GPIO 線(xiàn)設(shè)置為高電平可啟用 SPI-Avalon 橋接器,它進(jìn)而控制 Avalon 總線(xiàn)上的 32 位 PIO 端口。然后 PIO 輸出控制 NCO 頻率。

圖4 FPGA系統(tǒng)框圖

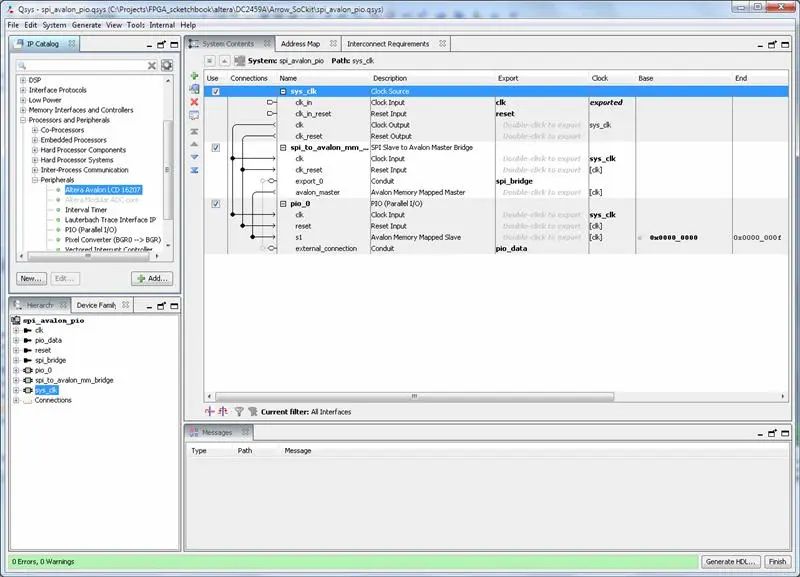

在基本系統(tǒng)運(yùn)行的情況下,可以將額外的外圍內(nèi)核連接到總線(xiàn)。為了設(shè)計(jì)系統(tǒng),Altera 提供了一種名為 Qsys 的工具,它提供了一個(gè) GUI 來(lái)將 IP 相互連接。Qsys 將 GUI 設(shè)計(jì)的系統(tǒng)(圖 5)轉(zhuǎn)換為 HDL。外設(shè)地址是完全可配置的。在這種情況下,PIO 設(shè)置為基址 0x0。

圖 5 Qsys GUI

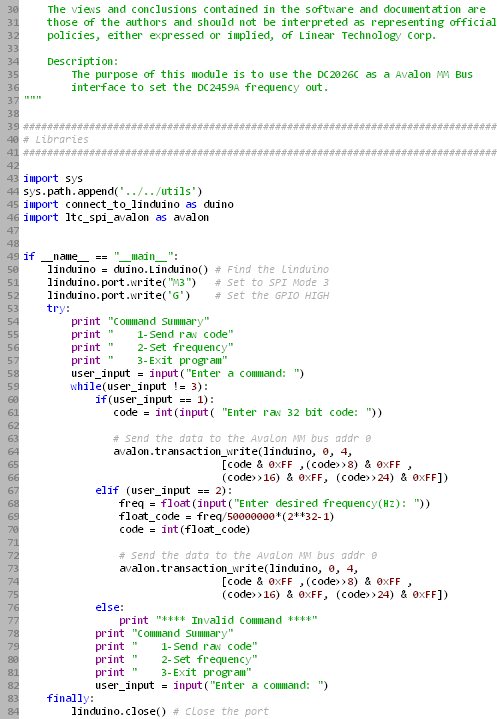

在 FPGA 中實(shí)現(xiàn)設(shè)計(jì)后,LinearLabTools 中提供的 Python 庫(kù)包含兩個(gè)與設(shè)計(jì)接口的函數(shù):

transaction_write (dc2026, base, write_size, data)

transaction_read (dc2026, base, read_size)

這些函數(shù)的個(gè)參數(shù)是 Linduino 串行端口實(shí)例。第二個(gè)參數(shù)是外設(shè)在 Avalon 總線(xiàn)上的地址。這些函數(shù)分別接受和返回字節(jié)列表。這兩個(gè)函數(shù)的編寫(xiě)是為了在寫(xiě)入和讀取 IP 時(shí)提供靈活性。要為提供的示例設(shè)置 NCO,只需要transaction_write 函數(shù)。公式 1 用于確定調(diào)諧字。

要以 50MSPS 采樣率將 NCO 設(shè)置為 1kHz,調(diào)整值為 85899 或 0x00014F8B,它作為四個(gè)字節(jié)的列表傳遞。因此,將 DAC 設(shè)置為 1kHz 的 python 代碼是:

transaction_write (linduino_serial_instance, 0, 0, [0x0, 0x01, 0x4F, 0x8B])

圖 6 Python Avalon 總線(xiàn)示例

圖 6中的 Python 腳本說(shuō)明了配置 NCO 的簡(jiǎn)單文本界面。重要提示:橋接器使用 SPI 模式 3。這被痛苦地確定為正確的 通過(guò)反復(fù)試驗(yàn)?zāi)J剑⑼ㄟ^(guò)分析 Altera 示例中的 Nios 處理器的 SPI 接口進(jìn)行驗(yàn)證。

該設(shè)計(jì)理念提供了在不接觸嵌入式處理器的情況下控制系統(tǒng)的能力,允許硬件工程師在不打擾軟件工程師的情況下推進(jìn)項(xiàng)目,并且對(duì)硬件設(shè)計(jì)的影響。

審核編輯:湯梓紅

-

處理器

+關(guān)注

關(guān)注

68文章

19405瀏覽量

231159 -

FPGA

+關(guān)注

關(guān)注

1630文章

21796瀏覽量

605969 -

嵌入式

+關(guān)注

關(guān)注

5092文章

19177瀏覽量

307632 -

Altera

+關(guān)注

關(guān)注

37文章

787瀏覽量

154160 -

總線(xiàn)

+關(guān)注

關(guān)注

10文章

2903瀏覽量

88384

原文標(biāo)題:不使用處理器控制 FPGA 總線(xiàn)

文章出處:【微信號(hào):gh_9d70b445f494,微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

專(zhuān)用處理器,未來(lái)電機(jī)驅(qū)動(dòng)的主流

不使用處理器的I2C控制器

什么是總線(xiàn)微處理器

DSP處理器與通用處理器的比較

多媒體應(yīng)用處理器的原理和應(yīng)用

什么是通用處理器

流水線(xiàn)操作,應(yīng)用處理器,應(yīng)用處理器的結(jié)構(gòu)和原理是什么?

基于i.MX257應(yīng)用處理器數(shù)據(jù)手冊(cè)

基于FPGA和多DSP的多總線(xiàn)并行處理器設(shè)計(jì)

不用處理器就可以控制FPGA總線(xiàn)的方法你知道嗎?

應(yīng)用處理器芯片行業(yè)科普

什么是專(zhuān)用處理器?專(zhuān)用處理器的設(shè)計(jì)方法和工具介紹

不使用處理器控制FPGA總線(xiàn)

不使用處理器控制FPGA總線(xiàn)

評(píng)論