一 關于這篇文章

如果沒有接觸過以太網相關硬件設計的話,也許會好奇,RJ45網口到控制器內部的物理通路是什么樣的,我的這系列文章希望能夠幫助到需要的人。內容初步規劃為三個部分:以太網硬件設計需要知道的基礎知識、以太網硬件設計細節、以太網測試,這篇是關于是以太網硬件設計需要知道的基礎知識,能夠對單板上以太網硬件設計的框架有個系統性認識。

二 單板上以太網硬件設計框架

2.1 以太網協議的基本構成

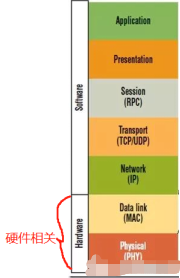

由于以太網的接口形態、信號的傳輸媒介和標準非常多(在IEEE 802.3中定義),這里只介紹最熟悉的,我們生活中最常見的以銅質雙絞線為媒介的10Base-T、100Base-TX、1000Base-T網絡,也就是我們常說的十兆、百兆、千兆網絡(單位兆是Mbps,Million bits per second),這三者可以在同一硬件架構上自動兼容,取決于PHY芯片的支持。標準以太網的整個通信鏈路被分為7層(許多協議復用以太網硬件架構,將以太網上層軟件協議進行擴展和修改,譬如EtherNET、GigE Vision、PROFINET等協議),與硬件設計相關的僅僅是數據鏈路層(MAC)、物理層(PHY)。

圖 1開放式系統互聯通信參考模型(此圖來自網絡)

2.2 以太網的硬件部分的基本構成

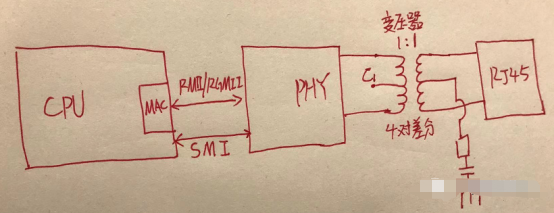

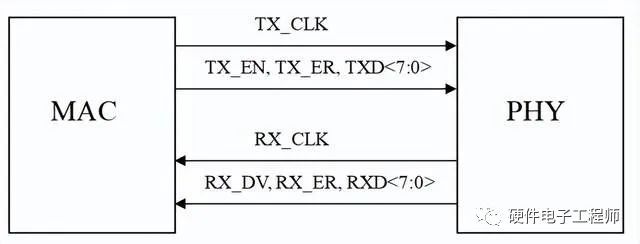

以太網協議與硬件相關的2層中,主控制器的接口為MAC,MAC口連接的外圍芯片PHY(有些主控內部集成了PHY,外部直接連網絡變壓器即可),MAC和PHY通信的接口有很多種(其實大同小異),用得最多的有RMII(最大支持百兆帶寬,MCU用得比較多)和RGMII(最大支持千兆帶寬,高性能平臺芯片用得比較多),其中SMI接口為PHY的寄存器配置引腳(MDIO,MDC),CPU可以通過該接口對PHY進行寄存器配置以及狀態的讀取。硬件的框圖如下:

圖2硬件框架簡圖

從框圖可以看到,電路并不復雜,CPU通過MAC的高速數字接口RMII/RGMII與PHY進行交互,PHY作為物理層,起到將CPU發送過來的網絡數據編碼成差分信號給到外部網絡接口MDI,同樣的,本機的PHY將與RJ45連接的另一頭的PHY發送過來的差分信號轉換為RGMII信號發送給CPU。圖中變壓器原邊中心抽頭C1的連接方式取決于PHY的類型,電流型PHY,C1連接電源,電壓型PHY,C1連接電容到信號地,PHY芯片的Datasheet中會有說明。

PHY的主要作用:

以太網底層協議的處理,包括自協商、link狀態、網線自動翻轉、沖突檢測等等,這些信息同步體現在寄存器中,可以通過SMI接口進行讀或寫。

RMII/RGMII數據的編解碼工作,在不同的帶寬下編解碼不一樣,1000BASE-T是4D-PAM編碼(5電平),100BASE-TX是MLT-3編碼(3電平),10BASE-T是曼徹斯特編碼。

在10/100兆網中,RJ45的1、2為TX,3、6為RX,現在的PHY芯片基本都支持自動MDI/MDI-X技術,TX和RX無需考慮交叉(如果不放心可以在PHY的datasheet中搜索“Automatic MDI/MDIX”,不支持可以使用交叉網線,參考《網線T568A與T568B(交叉網線)》)。1000兆網的使用8根線,采用混合調制技術(后續專門寫一篇文章講這個),4對差分線可以同時進行收發。

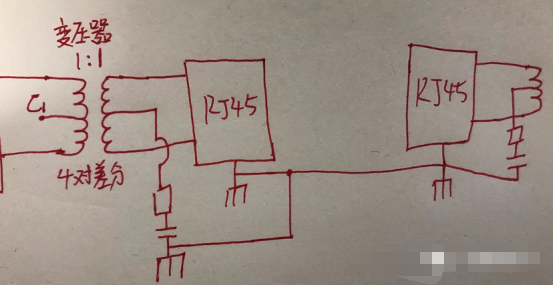

變壓器次級線圈的中心抽頭通過阻容連接到機殼地,電阻一般取值75Ω,電容一般取值1nF/2KV,主要作用是提供共模噪聲通路和濾波(變壓器內部還有共模濾波電感,圖中沒有畫出),如果網線是帶屏蔽的,屏蔽線連接機殼地(最好是圍繞信號線360°端接的方式),從而提供一個共模信號回流路徑,效果會更好。如下圖:

如果沒有屏蔽線,則兩設備通過電容或者遠端地線提供共模回路,從而共模信號的環路較大,工模信號的輻射也會較大。

圖中電路沒有保護電路,一般在變壓器的初級(靠近PHY芯片一側)放置ESD陣列即可,由于是高速信號,ESD的結電容原則上不超過1pF,如果在工作環境比較惡劣的場景,需要選用功率更高的管子,結電容可適當增加,原則上不超過2pF,次級也需要增加保護器件,具體情況具體分析。

-

控制器

+關注

關注

112文章

16445瀏覽量

179445 -

保護電路

+關注

關注

46文章

899瀏覽量

101779 -

以太網

+關注

關注

40文章

5460瀏覽量

172723 -

接口

+關注

關注

33文章

8691瀏覽量

151912 -

硬件設計

+關注

關注

18文章

399瀏覽量

44668

發布評論請先 登錄

相關推薦

以太網控制器(MAC)的基本框架怎么搭建

哪里可以做硬件故障單板的整改,USB2./USB3.0/以太網/MIPI/電源

基于Xilinx公司的SOPC的以太網設計

單板上以太網硬件設計框架

單板上以太網硬件設計框架

評論