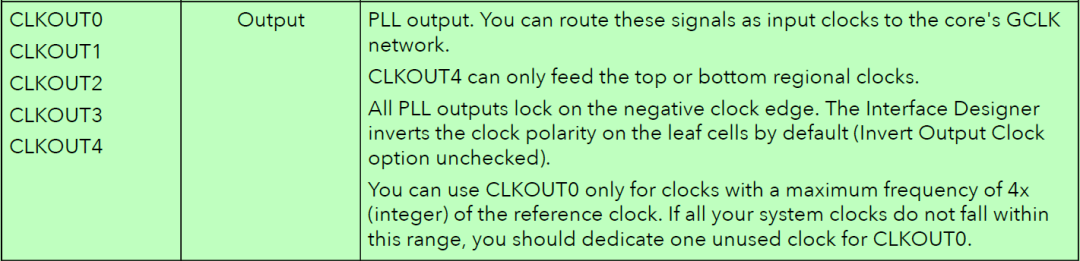

關(guān)于clkout4的說明其實不多,在PLL的說明中提到CLKOUT4只用于top和bottom的區(qū)域時鐘,但是不能驅(qū)動Core邏輯。

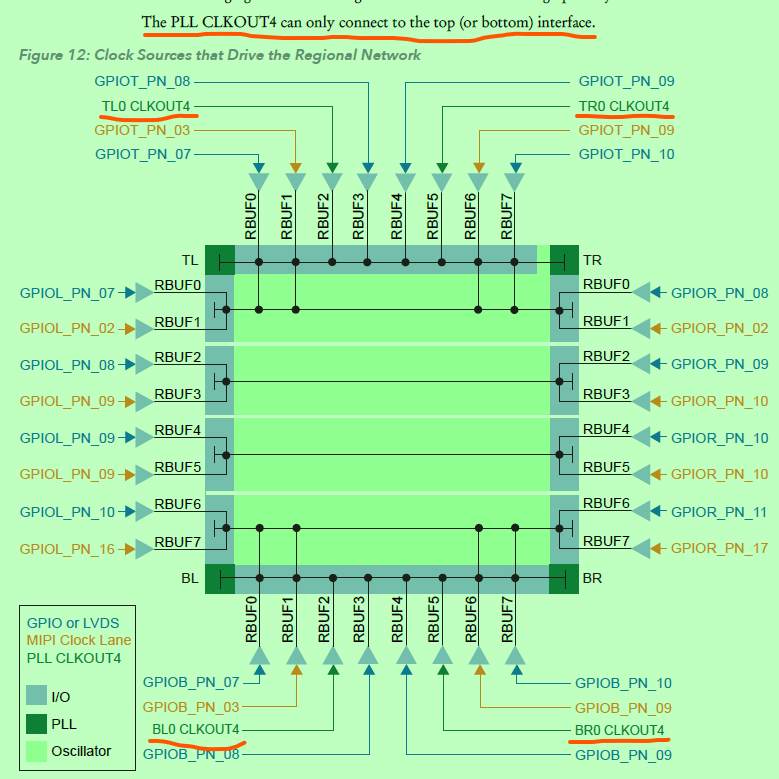

在區(qū)域時鐘部分又提到CLKOUT4只用于連接top或者bottom的interface。我們對interface的理解就是interface designer。

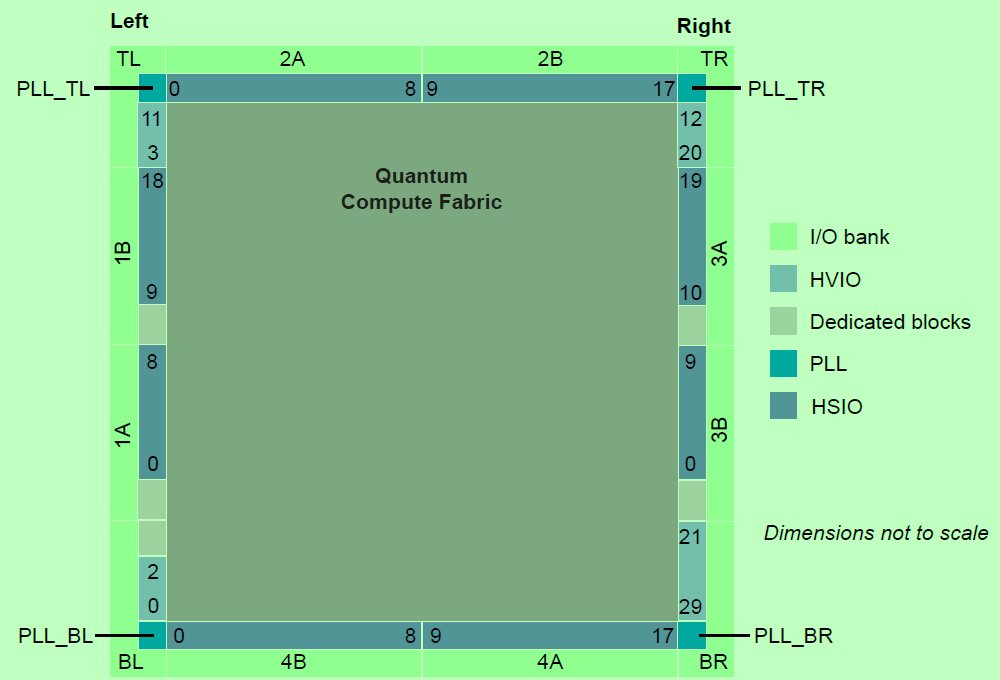

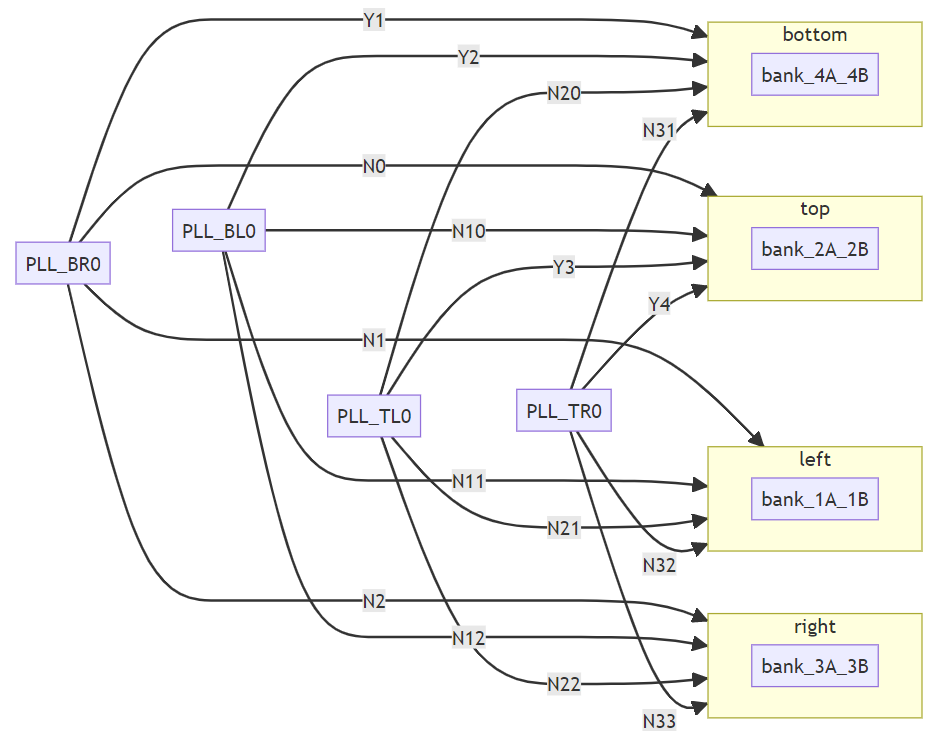

那這個top和bottom怎么理解呢?這里我們以Ti60F225為例。下圖是我們截取的Ti60F225的管腳位置平面圖。top我們認為就是bank 2A,2B,bottom我們認為是Bank 4B,4A. left就是bank 1A,1B,right就是Bank 3A,3B.

一、驅(qū)動IO測試

測試1:top和bottom驅(qū)動所在側(cè)的IO

在2A,2B bank各找5個GPIO并把它們設(shè)置成clkout類型,它們分別由TL和TR PLL驅(qū)動。

在4B和4A bank中也各找了5個GPIO并設(shè)置成clkout類型,時鐘由BR PLL的clkout4提供。

經(jīng)過編譯可以通過。

結(jié)論:TL和TR clkout4可以驅(qū)動BANK 2A和2B的IO.

BL和BR clkout4可以驅(qū)動BANK 4A 4B的IO

測試2:Top PLL clkout4驅(qū)動左側(cè)GPIO

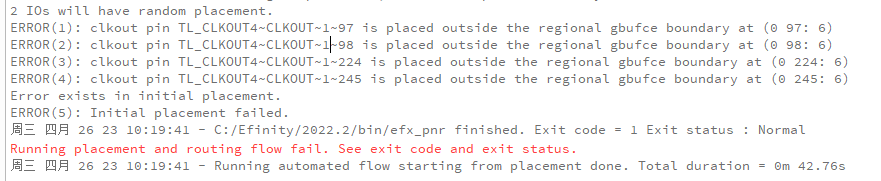

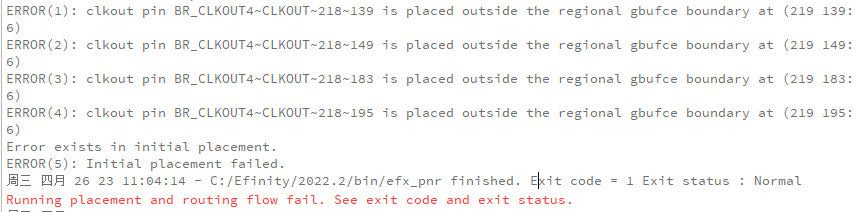

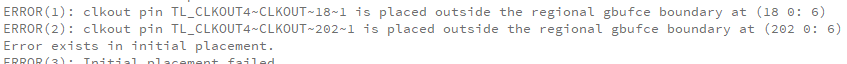

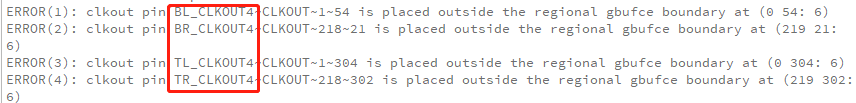

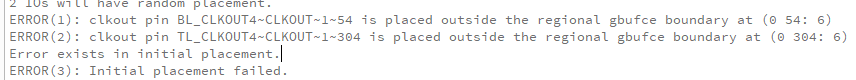

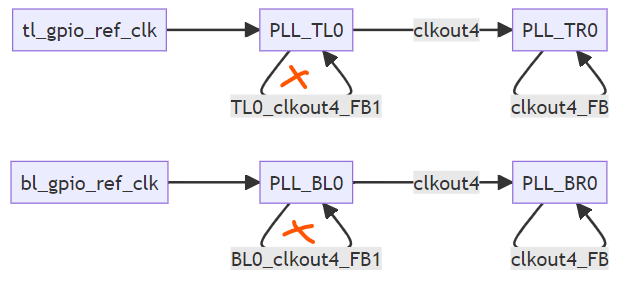

在測試1的基礎(chǔ)上,我們在bank 1A和1B上各找了兩個GPIO,設(shè)置成clkout類型,時鐘由TL PLL的clkout4來驅(qū)動或者BL PLL的clkout4來驅(qū)動都會報以下錯誤。

測試3:bottomPLL clkout4驅(qū)動右側(cè)GPIO

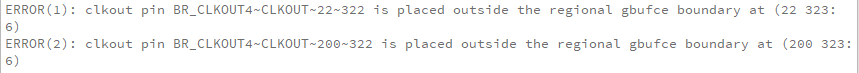

在測試1的基礎(chǔ)上,我們在bank 3A和3B上各添加了2個GPIO,由BR clkout4和TR clkout4來驅(qū)動。

結(jié)論:由測試2和測試3可以得出clkout4不能驅(qū)動左右兩側(cè)的IO。

另外我們還測試top PLL的clkout4驅(qū)動bottom 的IO,結(jié)論依然是不能驅(qū)動 ,反之亦然。于是我們有了下面的圖。圖中Y表示Yes,N表示N,后面的數(shù)字是編號,總之YX表示可以驅(qū)動,NX表示不可以驅(qū)動。

二、級聯(lián)測試

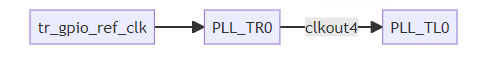

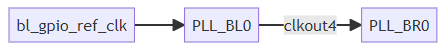

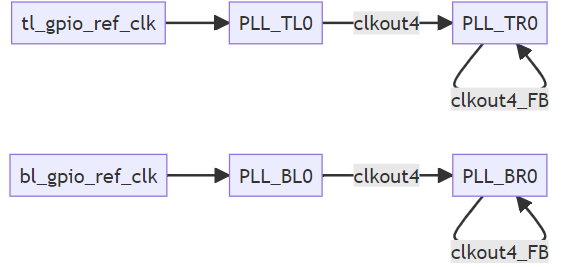

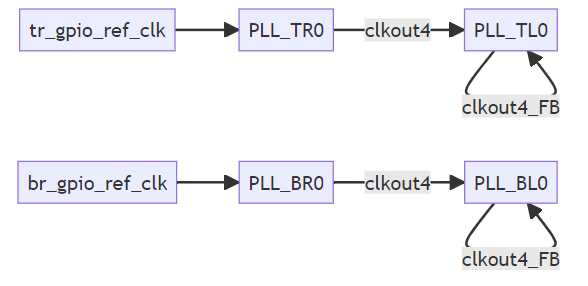

測試4:top或bottom的兩個PLL級聯(lián),但是clkout4不作為反饋

經(jīng)過測試可以編譯通過。

結(jié)論:clkout4可以在top或者bottom內(nèi)部實現(xiàn)兩個PLL級聯(lián)

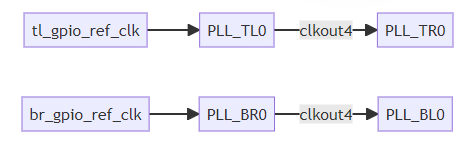

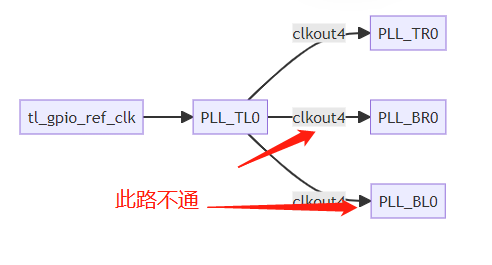

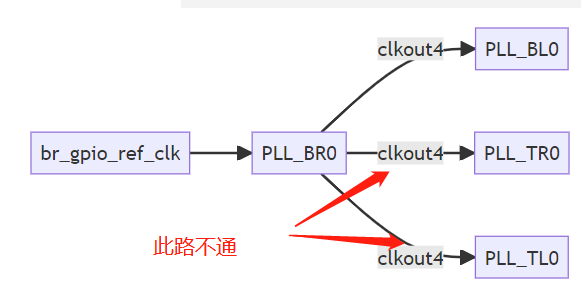

測試5:top與bottom的兩個PLL級聯(lián)

如果把TL0的clkout4作為BR0,BL0的參考時會報出兩個路徑出錯。

如果把BR0的clkout4作為TR0,TL0的參考時會報出兩個路徑出錯。

結(jié)論:top與bottom之間的PLL無法實現(xiàn)級聯(lián) 。

三、反饋測試

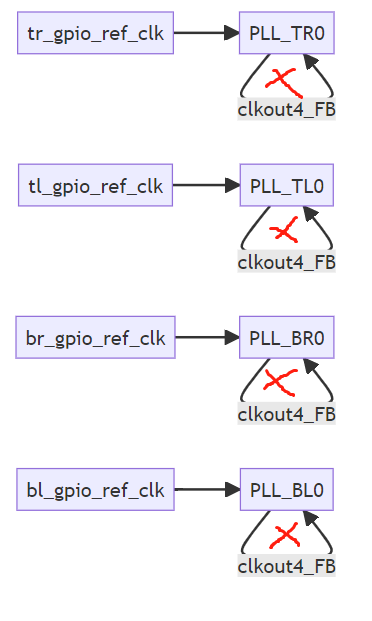

測試6:clkout4用作反饋

當PLL的參考時鐘為external時,用clkout4作為反饋時鐘,發(fā)現(xiàn)4個PLL都不能用作反饋。

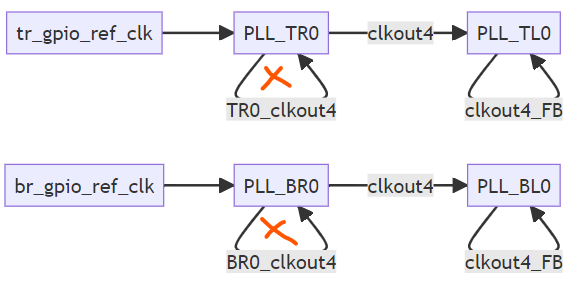

測試7:級聯(lián)反饋

如果級聯(lián)后,第一級的clkout4反饋也打開編譯也會出錯。經(jīng)過測試有以下結(jié)論。

結(jié)論:如果用clkout4用于級聯(lián),第二級的clkout4可以用作反饋。

綜上:

(1)top的PLL可以驅(qū)動top的IO,但不能驅(qū)動left,right和bottom的IO;同樣bottom的PLL可以驅(qū)動bottom的IO;但是不能驅(qū)動 top,left和right的IO.

(2)PLL可以通過clkout4實現(xiàn)級聯(lián),便是限制于(BL0,BR0)和(TL0,TR0)兩組內(nèi)部。

(3)PLL的clkout4也可以用作反饋,但是限制于級聯(lián)的兩個PLL的第二級。

審核編輯:湯梓紅

-

pll

+關(guān)注

關(guān)注

6文章

781瀏覽量

135333 -

時鐘

+關(guān)注

關(guān)注

11文章

1747瀏覽量

131803 -

管腳

+關(guān)注

關(guān)注

1文章

228瀏覽量

32121 -

GPIO

+關(guān)注

關(guān)注

16文章

1216瀏覽量

52379 -

反饋

+關(guān)注

關(guān)注

3文章

43瀏覽量

4902

原文標題:Ti60 PLL的clkout4使用限制--V0

文章出處:【微信號:gh_ea2445df5d2a,微信公眾號:FPGA及視頻處理】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

lmk04208 clkout0輸出不正常是什么原因?qū)е碌模?/a>

如何使PLL_BASE組件可配置?

PLL和FIFO的受約束問題

請問我能從PLL,DCM或級聯(lián)PLL DCM獲得多大的輸出頻率限制?

怎么查看ClkOut的延遲?

為什么dm8127的CLKOUT0未輸出時鐘信號?

請問PLL_ADV中CLKOUT2的輸出頻率是多少?

攝像機鏈接失敗切換限制約束

PLL屬性更改后時序失敗怎么辦?

Virtex-6有專用的clkout(PLL輸出)引腳嗎?

xc7k70t PLL最大輸出是多少?

【正點原子DFPGL22G開發(fā)板體驗】內(nèi)置IP核使用體驗-PLL之呼吸燈

LPC43xx PLL相位是否同步?

TI IWR6843單片60- 64-GHzmmWave傳感器解決方案

Ti60 PLL的clkout4使用限制

Ti60 PLL的clkout4使用限制

評論