演講嘉賓 | 曾建江

回顧整理 | 廖 濤

排版校對 | 李萍萍

嘉賓簡介

曾建江,亞琛工業大學博士,華為畢昇編譯器首席架構師、芯片軟件協同設計部部長,擁有多年編譯器與芯片軟件協同設計經驗,負責探索先進軟硬件協同設計技術、工具以及方法。

文章內容來源

第一屆開放原子開源基金會OpenHarmony技術峰會——開發者工具分論壇

視頻回顧

正 文 內 容

由C、C++、Java等高級語言編碼的人類可讀源代碼需要通過編譯器編譯,才能夠被翻譯成計算機可執行的目標代碼。在特定硬件平臺和編程語言的雙重約束條件下,應用程序的性能主要依賴于程序員編寫并行代碼的能力和編譯器的優化能力。華為多年自研的畢昇編譯器做了哪些優化工作,又如何賦能OpenHarmony開源生態呢?華為畢昇編譯器首席架構師曾建江在第一屆OpenHarmony技術峰會上,分享了幾點思考。

01?

畢昇編譯器介紹

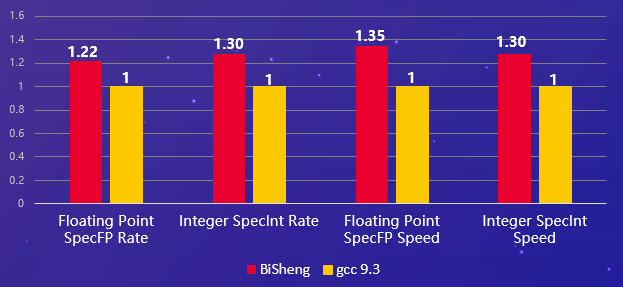

畢昇編譯器是華為自主開發的一款專注于C和C++代碼構建的系統底層組件,旨在發揮自研芯片的最佳性能。在鯤鵬服務器中,畢昇編譯器能夠與鯤鵬芯片協同,通過編譯器技術充分發揮芯片的性能。目前,畢昇編譯器for鯤鵬2.4.0版本的SPEC2017性能已經比GCC9.3提升了30%(測試環境及配置見https://www.spec.org/cpu2017/results/res2021q4/cpu2017-20211012-29727.html)。經過畢昇編譯器優化的超算領域HPC TOP應用的性能平均提升了10%,讓用戶在鯤鵬硬件平臺上能夠體驗到更好的業務性能。此外,畢昇編譯器與鯤鵬攜手已在政府、運營商、氣象、水利等多個國計民生行業落地商用,并持續在更多行業中拓展。今天,開發者可以方便地從鯤鵬套件中獲取到最新版的畢昇編譯器for鯤鵬(https://www.hikunpeng.com/zh/developer/devkit/compiler/bisheng)。

畢昇2.4.0版本與GCC的性能比較

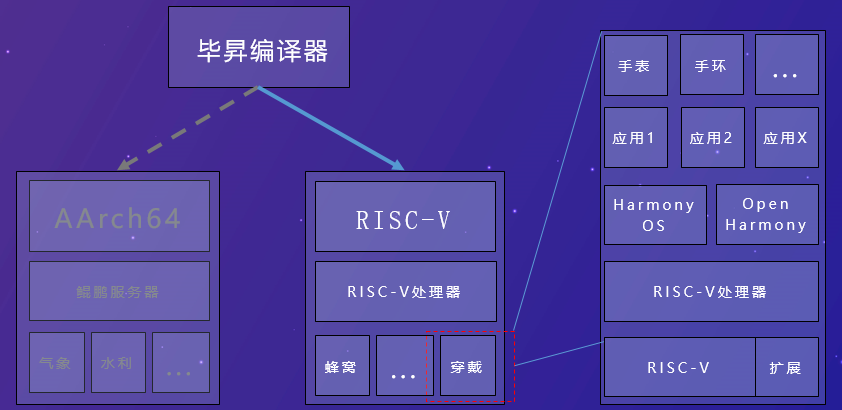

畢昇編譯器團隊很早就加入到RISC-V社區的開發中,形成深度協同。目前,畢昇編譯器已經基于RISC-V開發了MCU處理器,賦能穿戴智能終端,持續提升產品競爭力。此外,還積極參與OpenHarmony的生態建設工作,將MCU處理器上積累的Codesize和性能優化等編譯優化技術能力賦能到OpenHarmony生態的眾多其他設備上。

畢昇編譯器協同RISC-V

02?

Codesize和性能優化

在RISC-V的應用當中,特別是面向MCU成本特別得敏感,而Codesize的壓縮優化是節省MCU成本的有效方法之一。畢昇編譯器采用了函數跳轉壓縮、跳轉表壓縮和Global Propagation增強等技術,進一步精簡了編譯的代碼量。在函數跳轉中,畢昇編譯器基于RISC-V對整個跳轉過程進行優化,將原先兩條指令合成一條指令,每一次跳轉能夠節省32 Bytes的Codesize。在跳轉表中,畢昇編譯器采取基線地址偏移值代替絕對值的方法,保存表中相鄰元素的地址差值(8 Bytes)而非元素本身(32 Bytes),從而達到壓縮跳轉表的目的。此外,畢昇編譯器也通過全局變量傳遞的方法對其重復加載問題進行了優化。

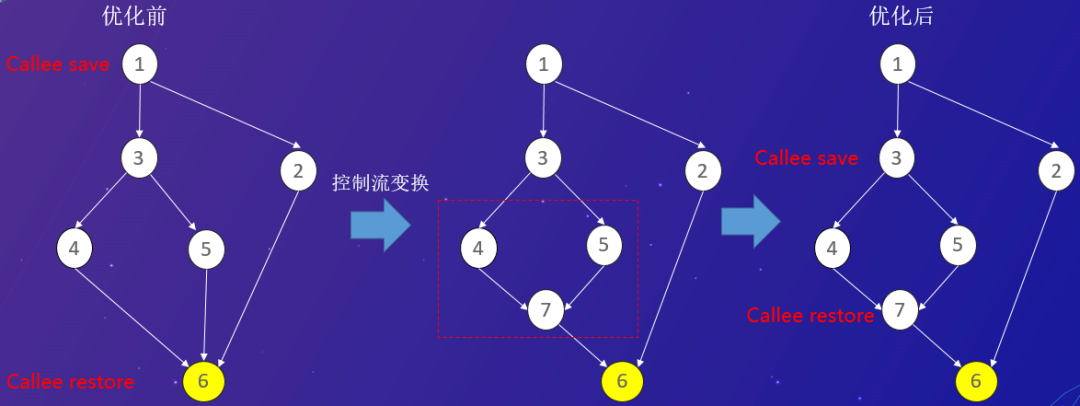

在性能方面,由于函數調用涉及頻繁的壓棧和出棧操作,造成了不必要的性能開銷。畢昇編譯器采取了Shrink wrap增強技術,通過重新安排函數prologue和epilogue的位置以減少函數的棧保存操作。

畢昇編譯器Shrink wrap增強

除了上述純編譯優化技術外,畢昇MCU編譯器還與華為自研的RISC-V擴展指令相配合,讓相關產品的軟件獲得領先的代碼體積與性能收益。即使只使能RISC-V社區標準的IMFADC等擴展的指令,在不使用自研擴展指令的前提下,畢昇MCU編譯器依舊能為開發者提供優秀的軟件性能與代碼體積。隨著華為MCU類產品的商用交付的推進,華為和RISC-VMCU的開發者將很快就能用上畢昇MCU編譯器。

03?

總結

未來,華為畢昇編譯器團隊將把畢昇編譯器的優化技術和能力通過開源貢獻到OpenHarmony社區,以此促進OpenHarmony軟件生態的發展,讓整個OpenHarmony生態都能夠獲得有競爭力的編譯技術支撐。

E N D

點擊下方閱讀原文獲取演講PPT。

關注我們,獲取更多精彩。

審核編輯黃宇

-

編譯器

+關注

關注

1文章

1642瀏覽量

49291 -

RISC-V

+關注

關注

45文章

2324瀏覽量

46604 -

OpenHarmony

+關注

關注

25文章

3747瀏覽量

16592

發布評論請先 登錄

相關推薦

明晚開播 |開源芯片系列講座第26期:奕斯偉RISC-V GCC工具鏈實踐分享

直播預約 |開源芯片系列講座第26期:奕斯偉RISC-V GCC工具鏈實踐分享

圣誕特輯 |開源芯片系列講座第25期:RISC-V架構在高性能領域的進展與挑戰

HighTec C/C++編譯器套件全面支持芯來RISC-V IP

RISC-V架構及MRS開發環境回顧

直播預約 |開源芯片系列講座第25期:RISC-V架構在高性能領域的進展與挑戰

HighTec C/C++編譯器支持Andes晶心科技RISC-V IP

RISC-V,即將進入應用的爆發期

2024 RISC-V 中國峰會:華秋電子助力RISC-V生態!

2024 RISC-V 中國峰會:華秋電子助力RISC-V生態!

中移芯昇加入甲辰計劃,共建 RISC-V 生態繁榮

玄鐵RISC-V生態大會深圳召開,達摩院引領RISC-V創新應用

峰會回顧第6期 | 畢昇編譯器與OpenHarmony RISC-V生態的進展

峰會回顧第6期 | 畢昇編譯器與OpenHarmony RISC-V生態的進展

評論