1串擾的基本信息

串擾是指有害信號從一個網絡轉移到相鄰網絡。任何一對網絡之間都存在串擾。通常把噪聲源所在網絡稱為動態網絡或攻擊網絡。把受影響的網絡稱為靜態網絡或者受害網絡。

串擾不僅僅出現在信號路徑,在返回路徑上也可能出現。從動態網絡上耦合到靜態網絡上的電壓與靜態網絡上原有的電壓完全無關。如果靜態線上本身的電壓為3.3V,從動態線耦合過來的噪聲是150mV,那么靜態線上的電壓總合是3.45V。

如果有兩條動態線都在干擾同一條靜態線,那么靜態線上的噪聲是兩條動態線噪聲總合。

靜態線上的噪聲和其他信號一樣,在靜態線上能感受到特性阻抗的變換。噪聲在靜態線阻抗變化點,也會發生反射和失真。因此串擾的影響不僅僅體現在噪聲信號幅度上,也會體現在噪聲信號的失真。

2串擾的噪聲源

當信號沿著傳輸線傳播時,信號路徑和返回路徑之間都會有電場和磁場產生,由此帶來電力線和磁力線。它充斥在信號路徑和返回路徑之間的空間中。把這些延伸出去的場稱為邊緣場。距離信號路徑和返回路徑越遠的地方,邊緣場越少。

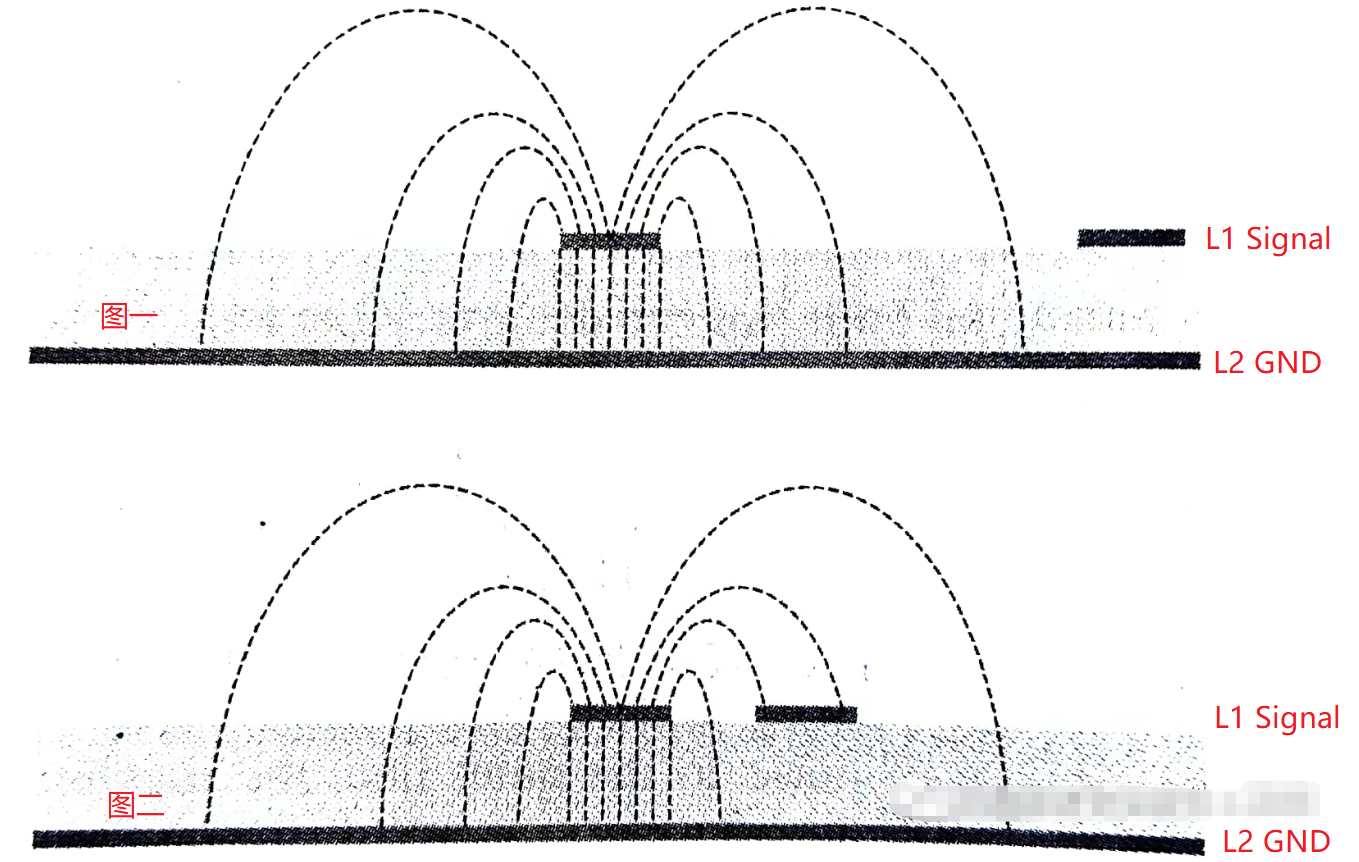

如下圖的圖一,右邊的靜態線遠離中間的動態線,不在動態線的邊緣場范圍內,基本不受動態線干擾。下圖的圖二,右邊的靜態線靠近動態線,受到動態線干擾。

當動態線上信號的電壓和電流發生變化時,變化的電流會造成變化的電場和磁場。由此在靜態線上產生電流和電壓噪聲。

邊緣場是串擾的根本原因。減小串擾的主要辦法就是增加動態線和靜態線之間的距離,使它們之間的邊緣場影響最小。一個PCB上,任何兩個網絡之間總會有邊緣場產生的容性耦合和感性耦合,稱為互容和互感。增大網絡之間的距離,就會減小互容和互感。

3近端串擾和遠端串擾

信號從源端輸出,經過動態傳輸線到達負載端。在靜態傳輸線上可以看到串擾過來的噪聲。而且在靜態傳輸線的兩端看到的噪聲不同。把靠近源端的靜態線端稱為“近端”,把遠離源端的靜態線稱為“遠端”。近端是信號傳輸方向的相反方向,遠端是信號傳輸前進的方向。

不考慮反射等影響,僅僅只是看串擾的波形。

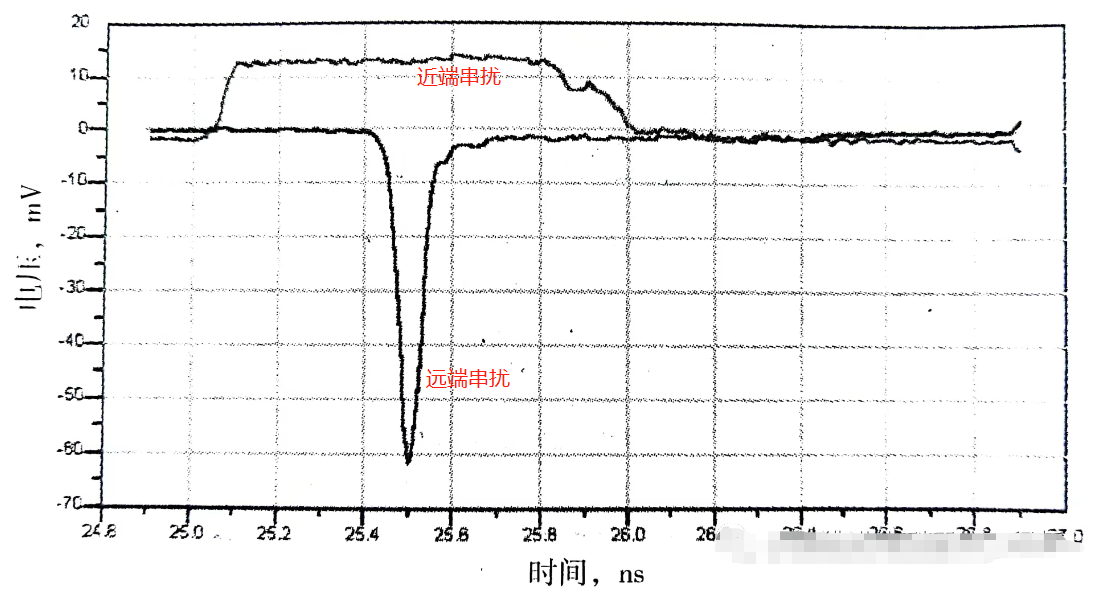

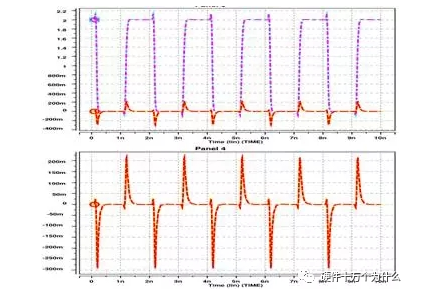

近端噪聲波形:快速上升到固定值,并且保持一定時間,然后再下降。保持時間等于動態線和靜態線耦合長度帶來的時延的兩倍。如果傳輸線的端接發生變化,近端噪聲值也會發生變化。

遠端噪聲波形:它在信號傳輸一段時間之后才會觀察到。它持續的時間很短,看起來是一個脈沖。脈沖寬度大約等于信號上升時間。

通過增大動態線和靜態線之間的距離,可以減小近端噪聲和遠端噪聲。另外減小耦合長度、使信號上升時間變緩慢,也可以降低遠端噪聲。

4描述串擾的兩種方法

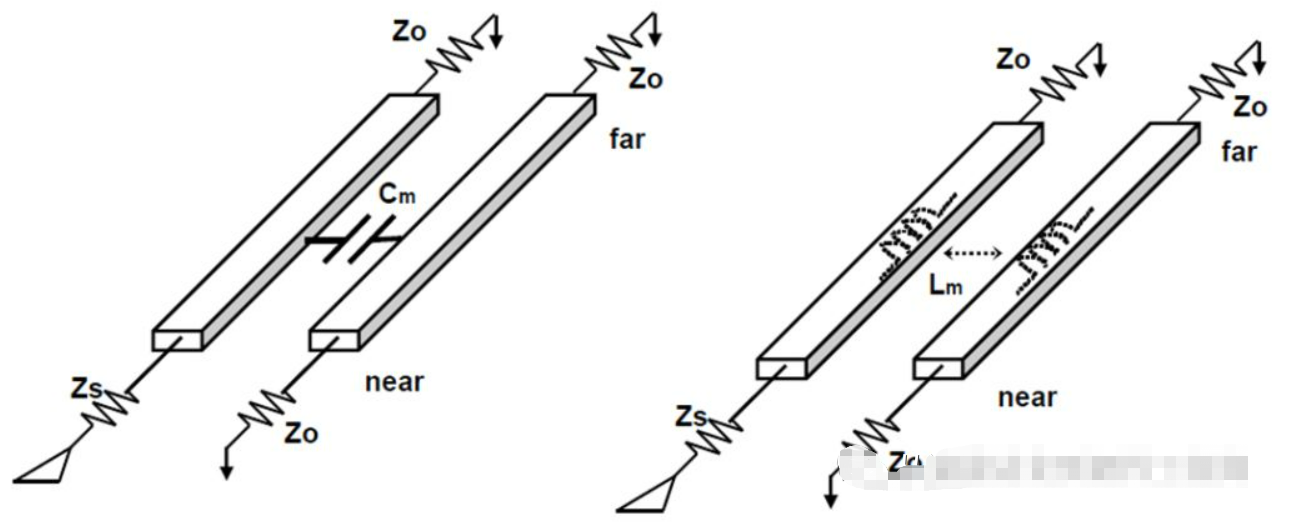

方法一:將動態線和靜態線看做一對差分線。用奇模阻抗、偶模阻抗、奇模時延、偶模時延,這四組參數來描述傳輸線的耦合和串擾。

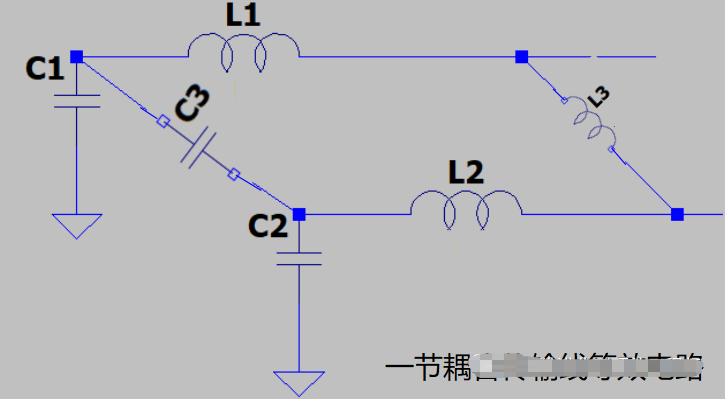

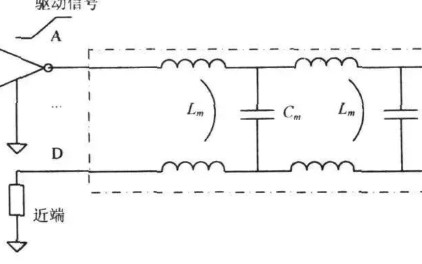

方法二:用n節LC模型來描述傳輸線的耦合和串擾。下圖是其中一節的LC模型。用n節組合起來得到整個動態線和靜態線的模型。LC模型的節數越多,近似程度越高。

針對每一節LC模型,單條傳輸線用單位長度電容CL(C1、C2)和單位長度回路電感Li(L1、L2)描述。兩條線之間的耦合用單位長度互容Cm(C3)和單位長度互感Lm(L3)描述。

當有兩條以上的傳輸線時,每條傳輸線之間都有寄生參數存在,此模型需要擴展,會變得更復雜。

5傳輸線之間寄生電容

5.1

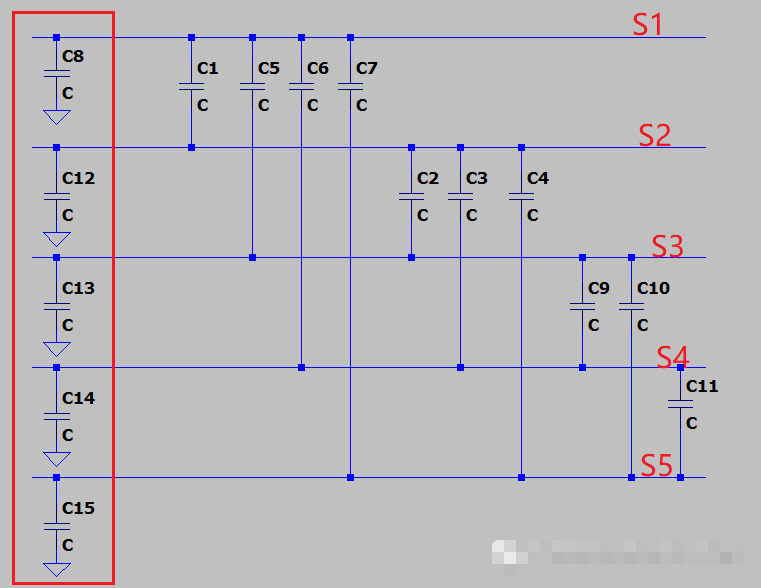

下圖是以多條傳輸線為例,分析5條傳輸線(S1~S5)之間的寄生電容值。因為對于高速信號的dV/dt,寄生電容大小決定了導線之間的容性耦合電流大小(噪聲電流)。

在本例中,5條線都是50Ω微帶線,每條傳輸線寬度W是5mil,傳輸線和傳輸線之間的距離也是5mil,即兩傳輸線中心之間的距離是2W。這些信號的返回路徑都是GND。

當出現多于兩條傳輸線的情況時,每條傳輸線之間都有寄生電容存在,只不過大小不同。紅色方框中的電容表示每條傳輸線和參考平面之間的寄生電容。其他電容是各個傳輸線之間的寄生電容。例如C1是S1和S2之間的寄生電容,C4是S2和S5之間的寄生電容。

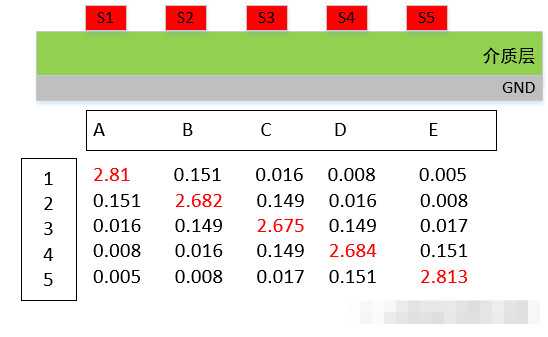

下圖信號線下方的數字表示每條傳輸線和參考平面之間的單位長度寄生電容、以及傳輸線和傳輸線之間的單位長度寄生電容,單位是pF/in。例如A1=2.81pF/in,是S1和參考平面之間的單位長度寄生電容。B1=0.151pF/in,是S1和S2之間的單位長度寄生電容。C1=0.016pF/in,是S1和S3之間的單位長度寄生電容,依次類推。

通過以上的數據可以看到,①傳輸線和參考平面之間的耦合度要比傳輸線和傳輸線之間的耦合度更緊密。②相鄰傳輸線之間的耦合度比相隔傳輸線之間的耦合度要緊密。例如S1和S2之間耦合電容接近是S1和S3之間耦合電容的10倍。這也是為什么高速信號PCB設計時,要求傳輸線和傳輸線之間至少保持3W間距的原因。

5.2

需要注意的是,對一條傳輸線而言,它和參考平面之間的寄生電容會受到它和相鄰傳輸線距離的影響。例如當拉進S1和S2的距離時,S1對參考平面的寄生電容會減小一些,因為有一部分本來進入參考平面的電力線將分流到S2上去。

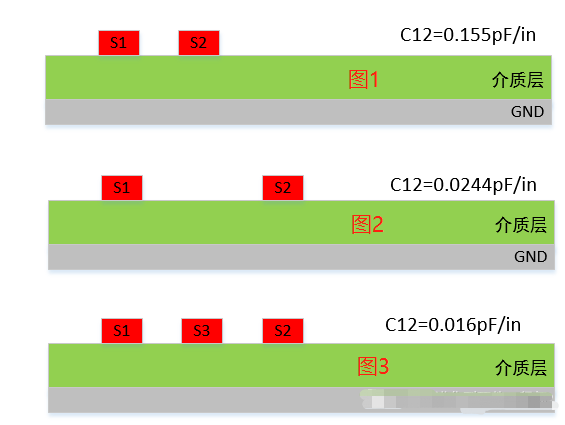

另一方面在兩條傳輸線之間插入第三條傳輸線,第三條傳輸線將分擔一些電力線,降低之前兩條傳輸線之間的耦合度。這也是我們在做PCB設計時,用GND線隔離敏感信號的原因。如下圖是2條傳輸線S1和S2,它們線寬是5mil。圖1線間距是5mil(邊到邊)。圖2線間距是15mil(邊到邊)。圖3是增加一條傳輸線S3,各線之間間距是5mil(邊到邊)。C12是S1和S2之間的單位長度寄生電容值。可以看到拉大S1和S1的距離會明顯降低寄生電容,插入一條新的傳輸線(通常是GND),寄生電容會進一步降低。

-

耦合

+關注

關注

13文章

584瀏覽量

100984 -

信號完整性

+關注

關注

68文章

1417瀏覽量

95635 -

寄生電容

+關注

關注

1文章

294瀏覽量

19332 -

傳輸線

+關注

關注

0文章

377瀏覽量

24132 -

串擾

+關注

關注

4文章

189瀏覽量

26995

發布評論請先 登錄

相關推薦

常見信號完整性的問題之PCB設計串擾的原因與Altium Designer中的串擾消除技術

信號完整性之串擾(一)

信號完整性之串擾(一)

評論