foreach i $sdf_views { write_sdf -view $i -interconn noport -recompute_parallel_arcs ./${sdf_dir}/${pf::design_name}_${i}.sdf.gz }

不同于PT,Tempus會默認寫出setuphold的負值。

1.2PT寫出SDF

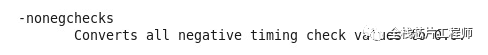

注意,PT默認生成2.1版SDF。分享一個案例,某項目腳本沒按照上面格式(參見知識星球)寫,然后寫出的SDF 3.0會將SDF里面的setup、hold的負數全部變成0,其命令如下:

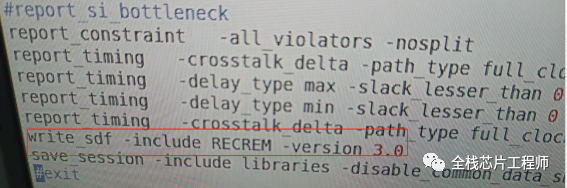

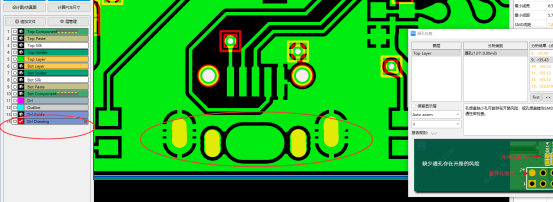

造成的結果對比:下面左上圖片setuphold有負數,而右下圖片hold全變成0。

實戰ISP圖像算法效果

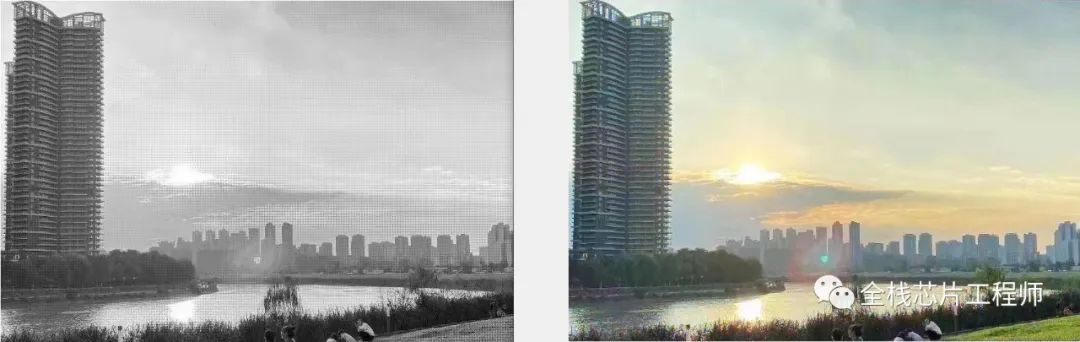

知識星球發起MCU項目啟動,大家一起參與MCU項目規格啟動討論,我把設計、驗證、DFT、后端的知識點全部羅列出來,大家一起來完善。

審核編輯:劉清

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

mcu

+關注

關注

146文章

17324瀏覽量

352658 -

ISP

+關注

關注

6文章

478瀏覽量

52017 -

DFT

+關注

關注

2文章

231瀏覽量

22841 -

Tempus

+關注

關注

0文章

4瀏覽量

6941

原文標題:分享芯片出SDF文件的一個“坑”

文章出處:【微信號:全棧芯片工程師,微信公眾號:全棧芯片工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Fatal: SDF files require Altera primitive library

求教,我在用modelsim-altera進行時序仿真時老是遇到錯誤:** Fatal: SDF files require Altera primitive library。我用

發表于 01-15 00:16

ISE 生成的sdf文件和在綜合前的約束有關系么?

對于一個rtl設計,ISE place & route 之后會生成sdf文件,那么,如果在綜合之前對 rtl設計,添加一定的約束,所生成

發表于 02-09 15:19

運行后實現時序仿真后重新生成sdf文件

您好,我正在使用Virtex7 FPGA運行Vivado 2017.2。在合成并實現我的設計之后,我導航到我的sdf文件并將LUT的延遲值從以下(INTERCONNECT nand2_inst

發表于 11-07 11:30

使用Modelsim SE 10.0b模擬后置和路徑模型找不到SDF文件

我想使用Modelsim SE 10.0b來模擬后置和路徑模型。后置和路徑模型由ISE 13.1生成。但我找不到SDF文件。你能告訴我如何找到SDF文件嗎?或者13.1中有另

發表于 02-13 07:11

SDF是什么?有何應用

型號:SDF-4.0SDF-5.0SDF-6.0SDF-6.3SDF-7.1SDF-8.0SDF-9.0SDF-10.0SDF-11.0SDF-11.5SDF-12.0SDF-12.5SDF-13.0■SDF是一種特殊的對旋局部

發表于 09-02 09:09

STM32入坑教程(一)點亮一個LED燈

STM32入門教程(一)點亮一個LED燈隨表聊聊配置流程一.初始化引腳二.主函數中實現邏輯備注隨表聊聊作為所有入坑單片機的同學來說,第

發表于 12-24 19:34

?9次下載

PCB設計避坑指南

可靠性降低 (3)Altium設計的文件槽孔放錯層 (4)芯片因太靠近PCB邊緣而容易損壞 (5)差分端口線太細導致485電路不工作 (6)焊盤重疊 ...... 這些坑也太多了吧! 今天我們就來聊聊

解析SDF的Header Section信息與Cell Entries信息

SDF文件是在VCS/NC-Verilog后仿真運行時將STD/IO/Macro門級verilog中specify的延遲信息替換為QRC/Star-RC抽取的實際物理延時信息。

詳解芯片SDF文件 MCU芯片全流程設計

SDF文件是在VCS/NC-Verilog后仿真運行時將STD/IO/Macro門級verilog中specify的延遲信息替換為QRC/Star-RC抽取的實際物理延時信息。

發表于 05-08 10:30

?1.2w次閱讀

芯片后仿之SDF 3.0解析

SDF文件是在VCS/NC-Verilog后仿真運行時將STD/IO/Macro門級verilog中specify的延遲信息替換為QRC/Star-RC抽取的實際物理延時信息,所以如果SDF文

分享芯片出SDF文件的一個“坑”

分享芯片出SDF文件的一個“坑”

評論