在數(shù)字電路中,數(shù)據(jù)的正確性非常重要。 為了保證數(shù)據(jù)的正確性,在傳輸數(shù)據(jù)時(shí)需要添加一些冗余信息,以便在接收端進(jìn)行校驗(yàn)。 其中一種常用的校驗(yàn)方式是奇偶校驗(yàn)(Parity Check)。 本文將介紹奇偶校驗(yàn)的基本原理及實(shí)現(xiàn)方法,并給出FPGA實(shí)現(xiàn)的代碼示例。

一、奇偶校驗(yàn)原理

奇偶校驗(yàn)是一種基本的數(shù)據(jù)校驗(yàn)方式,其原理是在數(shù)據(jù)的尾部添加一個(gè)位,使得該位和數(shù)據(jù)中所有1的個(gè)數(shù)之和為奇數(shù)或偶數(shù)。 由于校驗(yàn)位的加入,使得數(shù)據(jù)傳輸中一旦數(shù)據(jù)錯(cuò)誤就能夠被檢測出來,從而保證了數(shù)據(jù)的正確性。

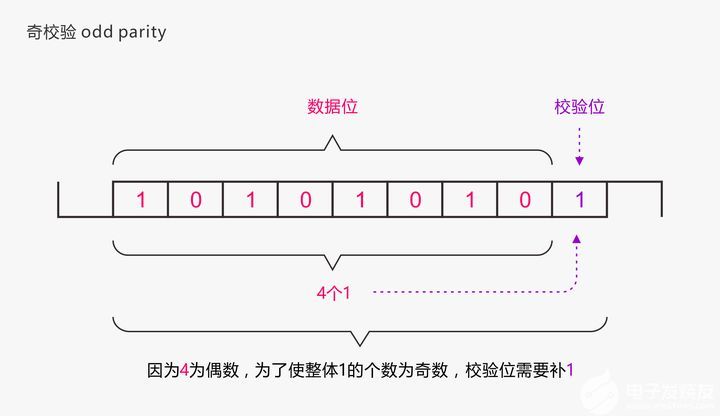

奇偶校驗(yàn)可以采用兩種方式:奇校驗(yàn)和偶校驗(yàn)。

奇校驗(yàn)::全部數(shù)據(jù)和該校驗(yàn)位中“1”的總數(shù)為奇數(shù),則表示數(shù)據(jù)無誤,否則數(shù)據(jù)錯(cuò)誤

偶校驗(yàn):全部數(shù)據(jù)和該校驗(yàn)位中“1”的總數(shù)為偶數(shù),則表示數(shù)據(jù)無誤,否則數(shù)據(jù)錯(cuò)誤

奇偶校驗(yàn)的優(yōu)點(diǎn)是簡單、快速,不需要大量計(jì)算。 但是奇偶校驗(yàn)只能檢測出錯(cuò)誤,不能糾正錯(cuò)誤,因此在實(shí)際應(yīng)用中很少單獨(dú)使用,通常與其它更加強(qiáng)大的校驗(yàn)方式結(jié)合起來使用。

以輸出一組16bit數(shù)據(jù)為“1100_0011_1101_0100”為例,這組數(shù)據(jù)中有8個(gè)“1”。

如果使用奇校驗(yàn),則校驗(yàn)位為1,傳輸數(shù)據(jù)實(shí)際為16bit數(shù)據(jù)+1bit奇校驗(yàn)位,即“1100_0011_1101_0100_1”。

如果使用偶校驗(yàn),則校驗(yàn)位為0,傳輸數(shù)據(jù)實(shí)際為16bit數(shù)據(jù)+1bit偶校驗(yàn)位,即“1100_0011_1101_0100_0”。

二、FPGA奇偶校驗(yàn)設(shè)計(jì)

1、多位輸入,分別用每位做:與、或、異或

module test(

input [3:0] in,

output out_and,

output out_or,

output out_xor

);

//方法一

assign out_and = in[0] & in[1] & in[2] & in[3];

assign out_or = in[0] | in[1] | in[2] | in[3];

assign out_xor = in[0] ^ in[1] ^ in[2] ^ in[3];

//方法二

assign out_and = ∈

assign out_or = |in;

assign out_xor = ^in;

endmodule

2、奇偶校驗(yàn)測試

奇偶校驗(yàn)只要求出其中一個(gè),另一個(gè)取反即得到了。

module parity_check(

input [7:0] data_in,

input sel,

output check

);

wire even;// 偶校驗(yàn)

wire odd;// 奇校驗(yàn)

assign even = ^data_in;

assign odd = ~even;

assign check = (sel)?odd : even;

endmodule

測試激勵(lì)

module sim(

);

reg clk;

reg [7:0] data_in;

parity_check u_parity_check (

.data_in(data_in),

.sel(1'b0)

);

initial begin

data_in = 0;

#10 data_in = 8'b1011_1000;

#10 data_in = 8'b1011_0000;

#10 data_in = 8'b1111_1000;

#10 data_in = 8'b1011_1100;

#10 data_in = 8'b1011_1010;

#10 data_in = 8'b1111_1010;

#10 data_in = 8'b1011_1001;

#10 data_in = 8'b1011_1101;

#10 data_in = 8'b1011_1011;

#10 $finish;

end

endmodule

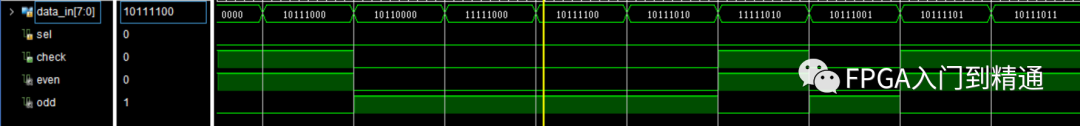

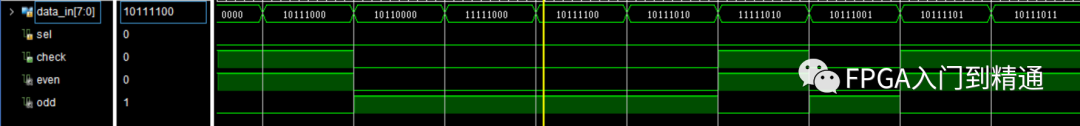

仿真測試結(jié)果圖:

從圖中可以看出,仿真測試結(jié)果與預(yù)期一致。

三、總結(jié)

奇偶校驗(yàn)算法很簡單,實(shí)現(xiàn)起來也很容易,本文提供了一個(gè)比較簡單的方法實(shí)現(xiàn),大家可以參考下。

-

FPGA

+關(guān)注

關(guān)注

1630文章

21796瀏覽量

605998 -

仿真

+關(guān)注

關(guān)注

50文章

4124瀏覽量

133991 -

數(shù)字電路

+關(guān)注

關(guān)注

193文章

1629瀏覽量

80822 -

代碼

+關(guān)注

關(guān)注

30文章

4825瀏覽量

69046 -

奇偶校驗(yàn)

+關(guān)注

關(guān)注

0文章

15瀏覽量

8232

發(fā)布評論請先 登錄

相關(guān)推薦

串口調(diào)試助手的奇偶校驗(yàn)測試方法

奇偶校驗(yàn)碼

奇偶校驗(yàn)器,奇偶校驗(yàn)器是什么意思

奇偶校驗(yàn)碼,奇偶校驗(yàn)碼原理是什么?

奇偶校驗(yàn)器_奇偶校驗(yàn)設(shè)計(jì)程序

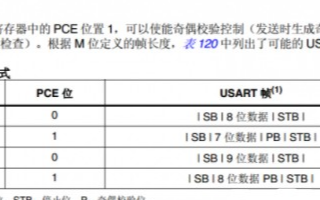

stm32串口奇偶校驗(yàn)

stm32 usart奇偶校驗(yàn)如何配置

奇偶校驗(yàn)的優(yōu)缺點(diǎn)及奇偶校驗(yàn)代碼實(shí)現(xiàn)

增強(qiáng)FIFO模式下的奇偶校驗(yàn)

介紹FPGA奇偶校驗(yàn)的基本原理及實(shí)現(xiàn)方法

奇偶校驗(yàn)器的設(shè)計(jì)方法和特點(diǎn)

FPGA奇偶校驗(yàn)的基本原理及實(shí)現(xiàn)方法

FPGA奇偶校驗(yàn)的基本原理及實(shí)現(xiàn)方法

評論