在Vivado TCL命令窗口中可以通過調用write_edif命令將用戶自定義模塊封裝成.edf網表文件(類似ISE里的.ngc文件),但按照官方給出的參考用法生成的網表文件對自定義模塊有種種限制,即待封裝的模塊不能含有Xilinx IP(少部分IP可以包含,如RAM IP、FIFO IP等),如DSP IP、MIG IP等,否則在編譯時將報錯,提示有未定義的黑盒。

那么如何將包含XIlinx IP的用戶模塊封裝成網表文件,下面將給出詳細步驟

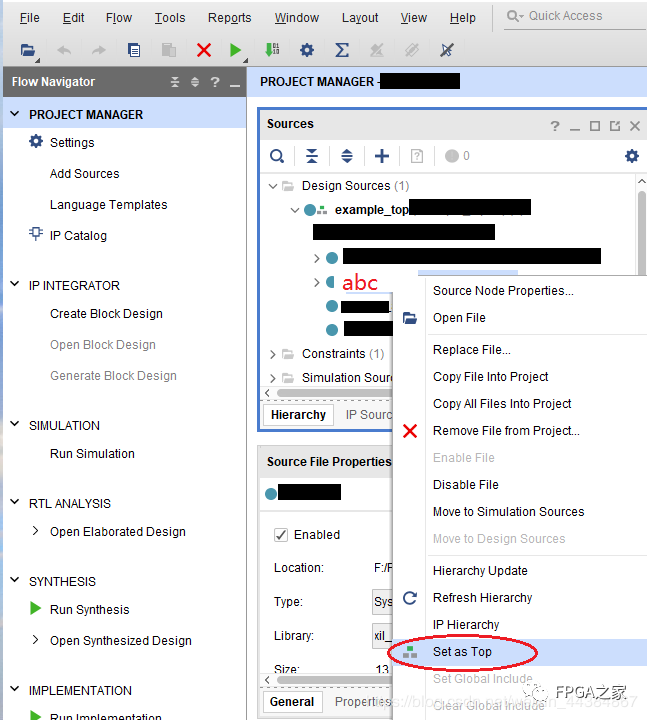

1. 將待封裝模塊設置為top層

如下圖所示,待封裝模塊為abc,則選中abc后右鍵,選擇“Set as Top”,

2. I/O Buffers設置

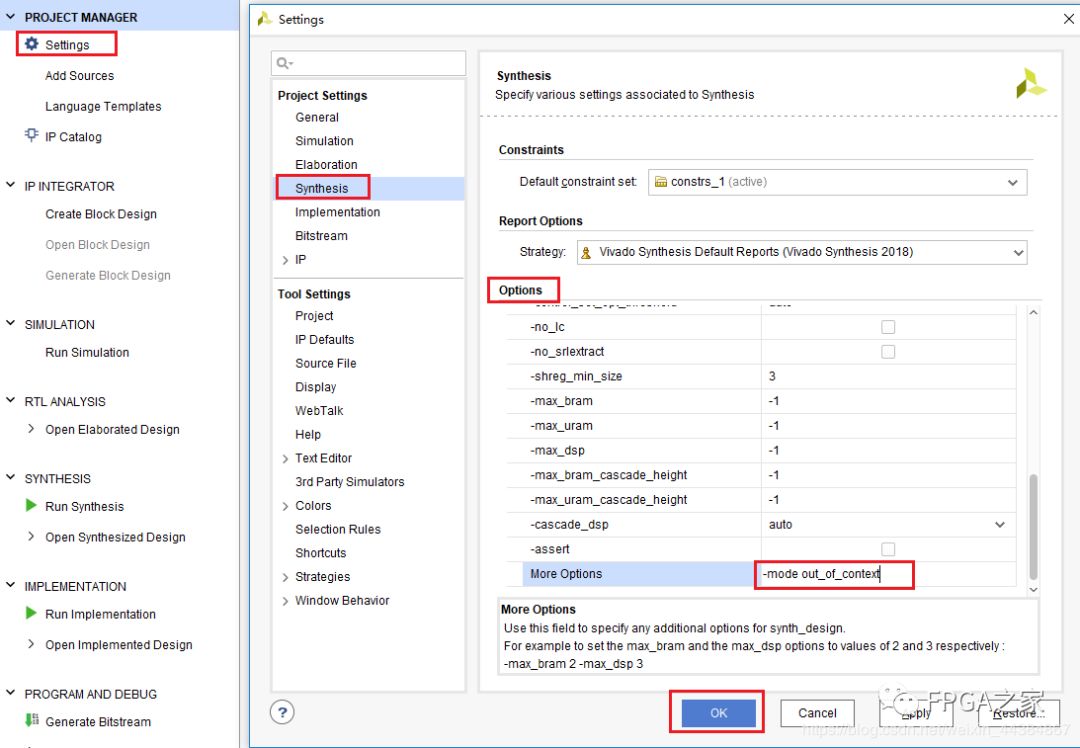

設置Settings–>綜合 synthesis–>選項options下拉至最后一項:More Options,將其值設置為:

-mode out_of_context

-mode out_of_context表示在該級不插入任何I/O BUFFERs,該選項類似ISE里在相應設置處不勾選I/O BUFFERs。

另外還可以在選項options中找到“-flatten_hierarchy”,將層級結構設置為“full”,

層級結構則可設置“-flatten_hierarchy”選項為“full”:“全”該選項指示工具把層級全面變平,只剩下頂層,保護IP的層級結構不被其他用戶清楚查看。

3. 綜合

運行綜合synthesis,完成綜合后,打開綜合設計open synthesized design

4. 生成僅包含IO端口信息的empty module

打開綜合設計open synthesized design后,在TCL命令窗口執行如下命令:

2017.4之前版本:

write_verilog -mode port F:/FPGA/abc_stub.v

2018.1之后版本:

write_verilog -mode synth_stub F:/FPGA/abc_stub.v

其中F:/FPGA/替換為要存放的路徑,如未指明路徑,則將存放到工程文件所在路徑下。

5. 生成edf文件

重頭戲來了,分兩條:

若不含Xilinx IP則可通過如下命令生成edf文件:

write_edif F:/FPGA/abc.edf

若含Xilinx IP則需通過如下命令生成edf文件:

write_edif -security_mode all F:/FPGA/abc.edf

6. 新工程中網表文件調用

將上述生成的abc_stub.v和abc.edf添加到新工程中即可。

7. 帶Xilinx IP的另外一種網表封裝方式(不推薦)

上述步驟3后,在tcl命令窗口中執行如下命令:

write_verilog -force abc_stub.v

-

封裝

+關注

關注

127文章

7991瀏覽量

143396 -

Xilinx

+關注

關注

71文章

2171瀏覽量

122120 -

編譯

+關注

關注

0文章

661瀏覽量

33040

原文標題:使用Vivado將包含Xilinx IP的用戶模塊封裝成網表文件(也適用不包含Xilinx IP的用戶模塊)

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

xilinx EDF已經綜合過的網表文件怎樣添加到Vivado工程中?

xilinx vivado 怎么封裝包含一個ip核的自定義ip?

怎么將HDL源文件添加到Xilinx IP?

基于Vivado將verilog代碼封裝成IP的步驟

Xilinx CORE生成器IP列表名稱及說明詳解

如何將IP模塊整合到System Generator for DSP中

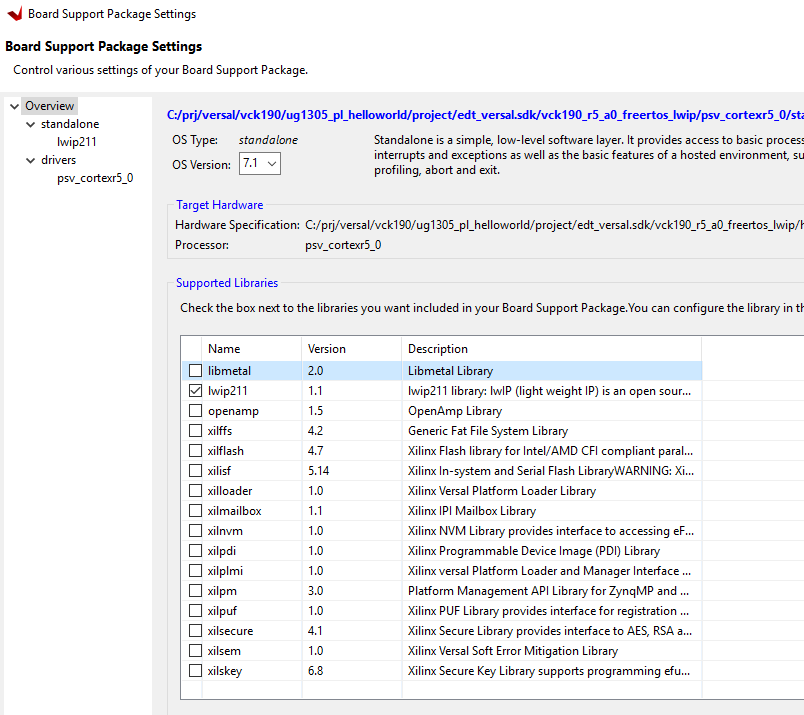

Xilinx如何配置BSP工程包含的的公共模塊

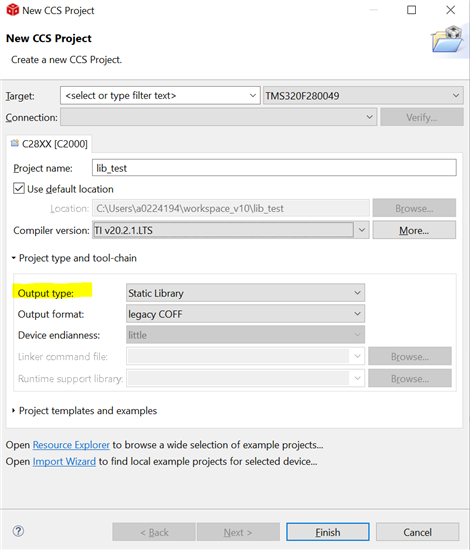

如何將函數封裝成庫使用的方法介紹

關于如何將函數封裝成庫使用的方法介紹

如何將包含XIlinx IP的用戶模塊封裝成網表文件

如何將包含XIlinx IP的用戶模塊封裝成網表文件

評論