編 者 按

當在SpinalHDL中調用別人的RTL代碼時,需要采用BlackBox進行封裝。對于大多數場景,想必小伙伴們都已輕車熟路。今天著重來看下當RTL代碼的接口中存在數組形式的接口時如何處理。

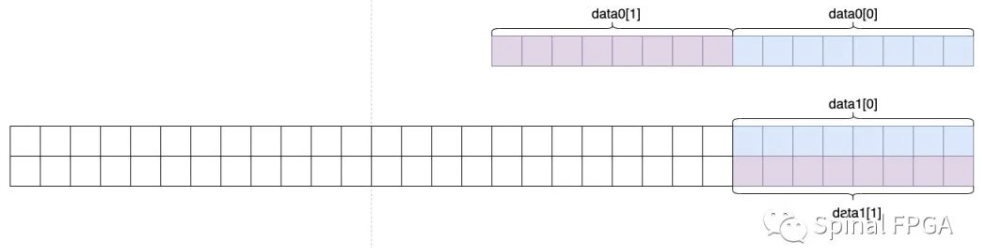

合并數組和非合并數組 在開始之前先了解兩個概念:合并數組與非合并數組。在SystemVerilog中,關于可綜合的數組存在兩種形式:

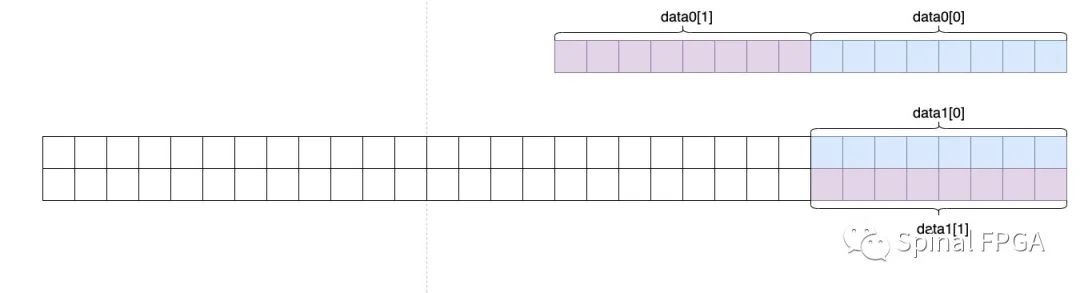

wire [1:0][7:0] data0; //合并數組 wire [7:0] data1[1:0]; //非合并數組 ? 在仿真方面,合并數組是緊密排列的,而非合并數組則是按照內存對齊的形式進行排列(電路綜合中則無需考慮):

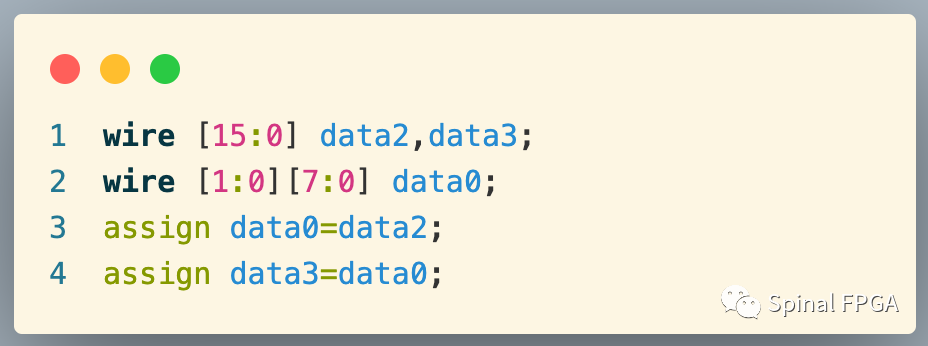

相應的,合并數組則可以作為一個整體進行賦值,而非合并數組則不可以:

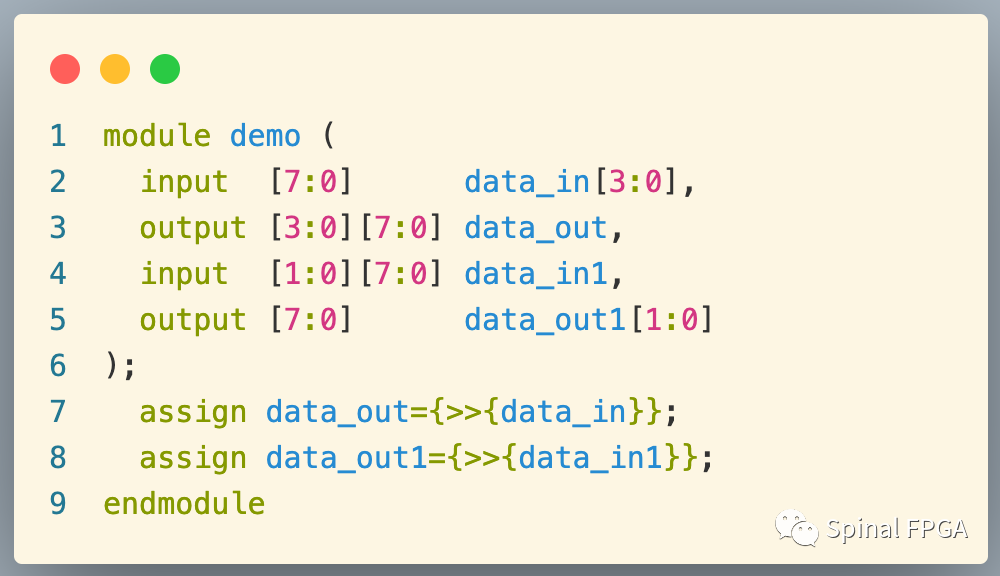

而合并數組與非合并數組,則可以通過SystemVerilog中所提供的流操作符進行相互轉換處理(是可以綜合的):

? ?

? ?

》BlackBox封裝

在了解了上面的背景知識之后,再來看如何這種數組類場景如何封裝至BlackBox。兩條規則:

1、BlackBox封裝針對數組類接口僅能支持合并數組類型。

2、當接口中存在非合并數組接口時則需手動封裝一層通過流操作符將非合并數組轉換為合并數組。

基于上面的規則,可以進行數組接口的BlackBox封裝。

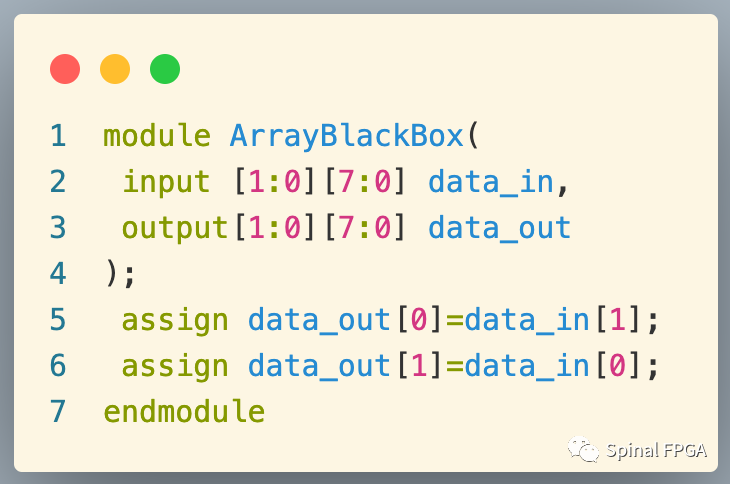

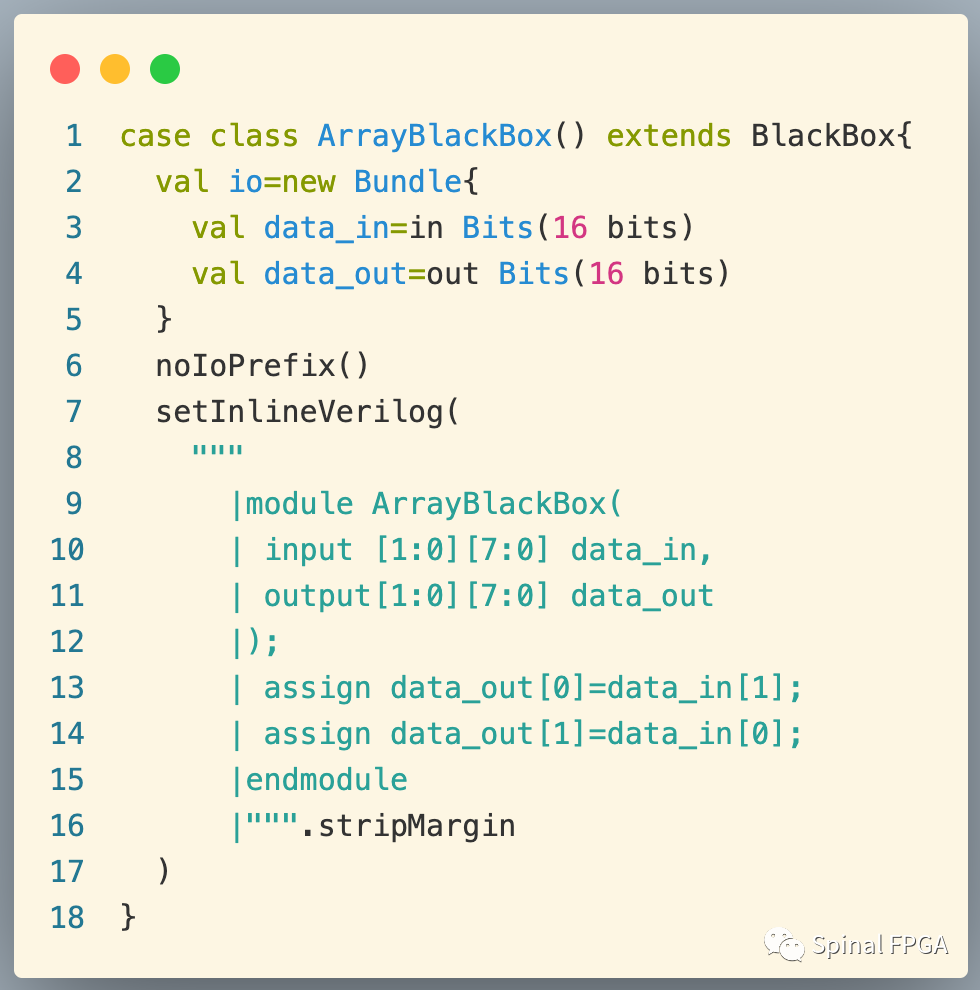

看下面的RTL代碼示例:

該模塊輸入,輸出均為一個合并數組,實現功能為兩個元素的數據交換。我們在進行封裝BlackBox時可采用下面的封裝形式:

這里我們在BlackBox中定義接口時將合并數組data_in,data_out均定義為Bits類型,寬度為合并數組中所有元素的位寬總和(2*8).

(這里面的setInlineVerilog也可不寫,主要是懶得再創建一個SV文件了。關于這部分功能可參見《彩——看blackBox的inline功能》)

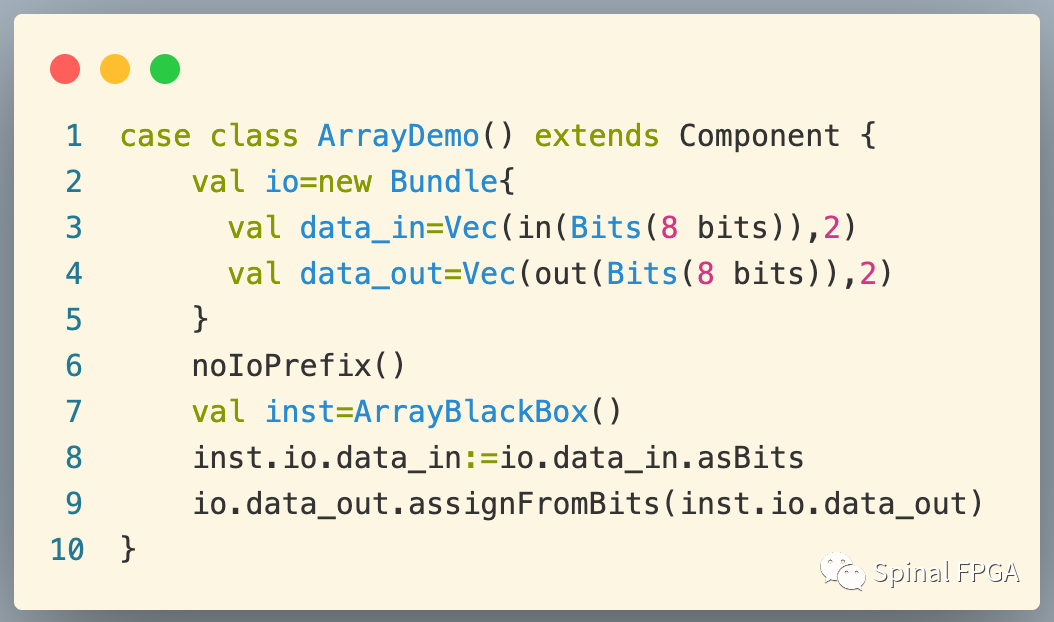

在進行調用時就可以和其他調用沒有區別了:

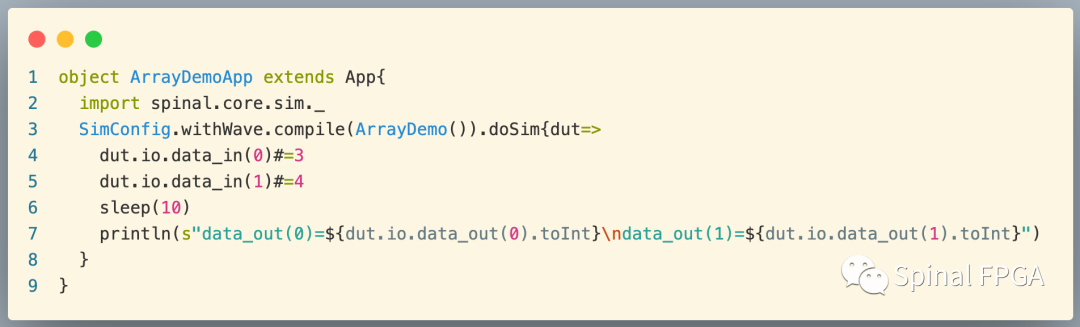

進行仿真:

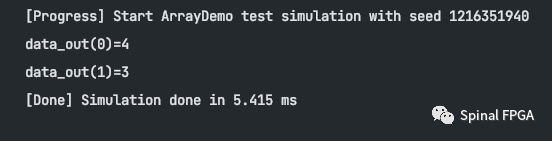

結果非常符合預期:

審核編輯:湯梓紅

-

接口

+關注

關注

33文章

8694瀏覽量

151928 -

封裝

+關注

關注

127文章

7997瀏覽量

143413 -

RTL

+關注

關注

1文章

385瀏覽量

59952 -

代碼

+關注

關注

30文章

4828瀏覽量

69057 -

數組

+關注

關注

1文章

417瀏覽量

26028

原文標題:驚!原來SpinalHDL中BlackBox封裝數組接口如此簡單

文章出處:【微信號:Spinal FPGA,微信公眾號:Spinal FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

在SpinalHDL里實現優雅的添加待跟蹤波形信號

在SpinalHDL的設計中集成現有RTL設計(IP)的渠道——BlackBox

關于SpinalHDL中的驗證覆蓋率收集簡單說明

聊一聊SpinalHDL 1.6.1引入的blackbox inline功能

聊聊SpinalHDL中的FIFO

SpinalHDL是如何讓仿真跑起來的

記錄一個在使用BlackBox中parameter踩到的坑

SpinalHDL BlackBox時鐘與復位

當RTL代碼的接口中存在數組形式的接口時如何處理?

Verilog代碼封裝后門訪問

原來SpinalHDL中BlackBox封裝數組接口如此簡單

原來SpinalHDL中BlackBox封裝數組接口如此簡單

評論