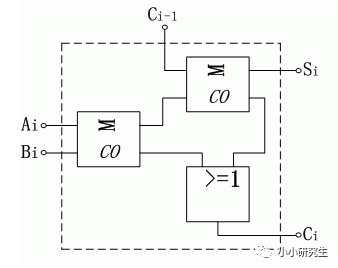

全加器可看作兩個半加器和一個或門組成。

首先半加器是A+B構成了{C,S}。由于全加器多了一個低位的進位,就是將{C,S}再加上Ci-1。此時再使用一個半加器將S與Ci-1相加,結果的低位就是全加器的低位Si。全加器的高位Ci來自于兩個半加器的高位,如果有一個高位為1,結果就為1。

設計規劃

本例中將采用3個按鍵作為輸入in1,in2和進位信號cin,并采用兩個LED燈作為信號輸出count和sum。根據上一節中全加器真值表,可以畫出波形圖:

編寫代碼

module full_adder

(

input wire in1 ,

input wire in2 ,

input wire cin ,

output wire sum ,

output wire cout

);

//wire define

wire h0_sum ;

wire h0_cout;

wire h1_cout;

//------------------------half_adder_inst0------------------------

half_adder half_adder_inst0

(

.in1 (in1 ),

.in2 (in2 ),

.sum (h0_sum ),

.cout (h0_cout)

);

//------------------------half_adder_inst1------------------------

half_adder half_adder_inst1

(

.in1 (h0_sum ),

.in2 (cin ),

.sum (sum ),

.cout (h1_cout)

);

assign cout = h0_cout|h1_cout;

endmodule

還記得FPGA從入門到精通(一)中的移位寄存器的實例化練習嗎?以module模塊名(輸入,輸出)開頭,以endmodule結尾。

上一節中已經封裝好了half_adder函數,內部的邏輯就不用再次寫了,只需要將外部端口和full_adder的端口對應好就可以直接調用。這就是verilog的方便之處,否則完成這個程序,需要將半加器的代碼寫兩次。

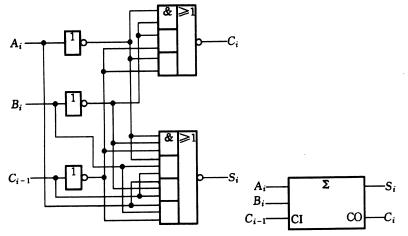

再上面的全加器結構圖中可以看到端口的對應,其中除了全加器的5個端口外,還需要引入三根連線。需要定義wire變量h0_count,h1_count和h0_sum。

下面完成兩次實例化,上一節中的半加器有in1,in2,cout,sum四個端口,第一個半加器分別對應著全加器的輸入端口in1,in2,h0_count,h0_sum,第二個半加器分別對應著上一個半加器的結果的低位h0_sum和低位進位cin,h1_count1,全加器的結果的低位sum。全加器的結果的高位count是h0_count和h1_count的或。

現在將.v文件綜合一定會報錯,因為還沒有將half_adder模塊添加進來。所以調用時找不到半加器的函數。因此需要將half_adder.v復制到文件夾中并添加到Files中:

看RTL視圖,兩個half_adder模塊是可以展開的:

編寫testbench

`timescale 1ns/1ns

module tb_full_adder();

reg in1;

reg in2;

reg cin;

wire sum ;

wire cout;

initial begin

in1 <= 1'b0;

in2 <= 1'b0;

cin <= 1'b0;

end

always #10 in1 <= {$random} % 2;

always #10 in2 <= {$random} % 2;

always #10 cin <= {$random} % 2;

//------------------------------------------------------------

initial begin

$timeformat(-9, 0, "ns", 6);

$monitor("@time %t:in1=%b in2=%b cin=%b sum=%b cout=%b",$time,in1,in2,cin,sum,cout);

end

//------------------------------------------------------------

//---------------full_adder_inst------------------

full_adder full_adder_inst(

.in1 (in1),

.in2 (in2),

.cin (cin),

.sum (sum),

.cout (cout)

);

endmodule

這里testbench依然是先聲明變量,其中輸入是reg類型,輸出是wire類型。初始化令變量都為0,延時10ns給輸入隨機賦值0或1,然后實例化將tb_full_adder模塊和full_adder模塊端口進行連接,就可以觀察波形。

需要注意的是!!!在本例中引入了打印模塊,可以直觀看到隨機輸入對應輸出的真值表。

$timeformat(units_number, precision_number, suffix_string, minimum_field_wdith);

timefomat的語法:

第一個參數units_number表示打印的時間值的單位,取0 到-15 之間的整數值:0 表示秒,-3 表示毫秒,-6 表示微秒,-9 表示納秒, -12 表示皮秒, -15 表示飛秒

第二個參數precision_number表示打印時間值時,小數點后保留的位數。

第三個參數suffix_string在時間值后面打印時間單位。其默認值為空字符串,如果用ns作為單位可以打印ns。

第四個參數MinFieldWidth 是時間值與單位字符串的最小長度,不足這個長度,則在字符串之前補空格。其默認值為20。

monitor的語法:

$monitor (“format_string”, parameter1, parameter2, … );

當在monitor調用時對多個變量進行監控,當monitor監控的變量中任何一個發生變化時,將會打印出當前仿真時刻的值;如果$monitor監控的所有變量在某一時刻均不改變,將不會打印任何信息。本例中會打印出時間和5個端口值。

對比波形

當端口多了之后,看波形相對不直觀了,這里可以通過觀察我們剛才打印的數據進行判斷。通過View-transcript可以觀察transcript窗口:

表格的方式相對直觀多了,且輸出和預期一致。

分配管腳

全編譯后分配引腳,這里的按鍵和LED燈管腳我們已經非常熟悉了。在location這一欄分配引腳,不要和fitterlocation弄混了。

現在cin,in1,in2對應S0,S1,S2,cout對應LED0,sum對應LED1。那么cin,in1,in2按下去表示為0,點亮的LED表示對應為輸出為低電平。都不按下去時,應該都熄滅,按下去一個時,LED0亮,按下兩個時,LED1亮,按下三個時,兩個LED同時亮。

全編譯后上板驗證

一個都不按下時,都不亮

按下一個時,LED0亮

按下兩個時,LED1亮

全部按下時,兩個都亮

組合邏輯電路的實例就結束了,后面是簡單的時序邏輯電路實例。

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605991 -

led燈

+關注

關注

22文章

1592瀏覽量

108407 -

移位寄存器

+關注

關注

3文章

259瀏覽量

22342 -

全加器

+關注

關注

10文章

62瀏覽量

28562 -

半加器

+關注

關注

1文章

29瀏覽量

8824

發布評論請先 登錄

相關推薦

Altium如何創建層次化的原理圖形式

什么是8位全加器和8為帶超前進位的全加器?

一種基于單電子晶體管的全加器電路設計

監控系統設備構成的分層次結構詳析

全加器是什么?全加器和半加器的區別?

全加器的真值表

層次化設計構成全加器

層次化設計構成全加器

評論