瑞薩電子的MCU產(chǎn)品RX72M是一款適用于工業(yè)網(wǎng)絡(luò)解決方案的高性能32位微控制器,在應(yīng)用時(shí)需搭配外部的以太網(wǎng)PHY芯片。本次我們介紹RX72M和PHY芯片連接時(shí)的注意事項(xiàng)。

一

所需引腳定義

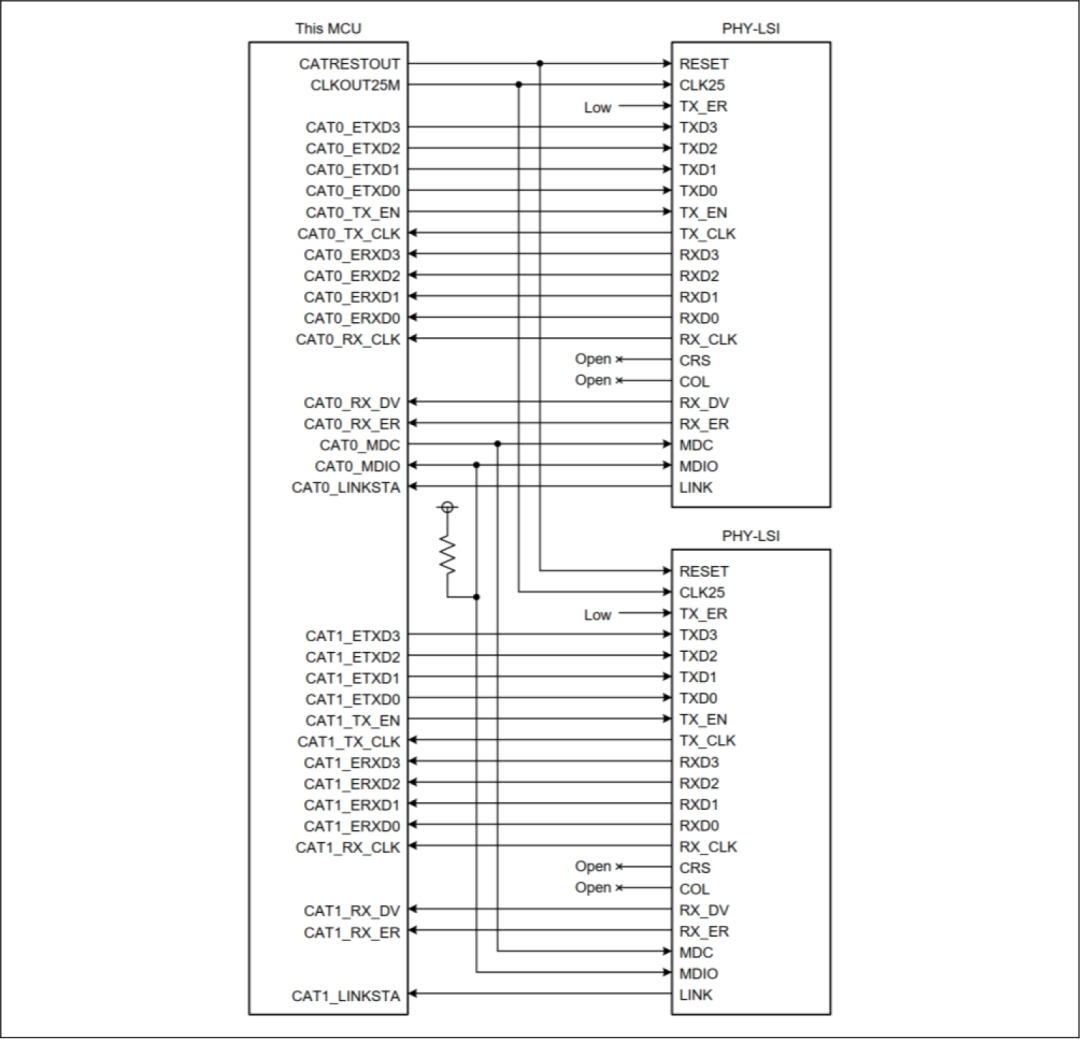

首先,RX72M和PHY芯片整體的連接關(guān)系如下圖(RX72M Hardware Manual中Example of Connection with the PHY-LSI)所示:

圖1 RX72M和PHY-LSI連接示例

由于RX72M具備兩個(gè)ESC端口,因此需要連接兩顆PHY芯片。

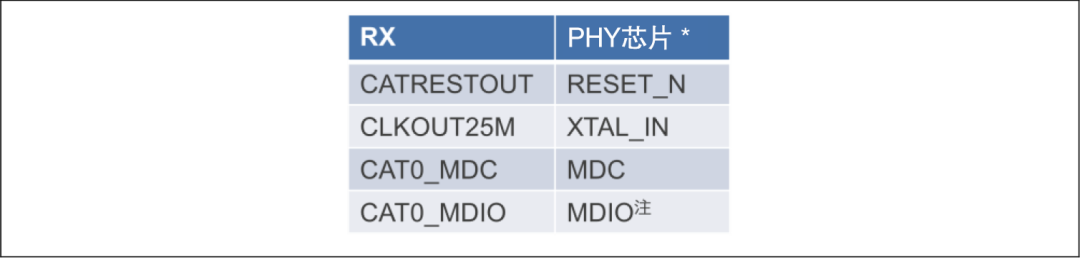

對于每個(gè)PHY芯片,和RX72M連接時(shí)用到的引腳如下:

圖2 每個(gè)PHY芯片和RX72M引腳的連接

注:*的值為0或1。

兩個(gè)PHY芯片共同連接到RX72M的引腳如下:

圖3 兩個(gè)PHY芯片和RX72M連接時(shí)共用的引腳

注:MDIO引腳需增加4.7K上拉電阻。

二

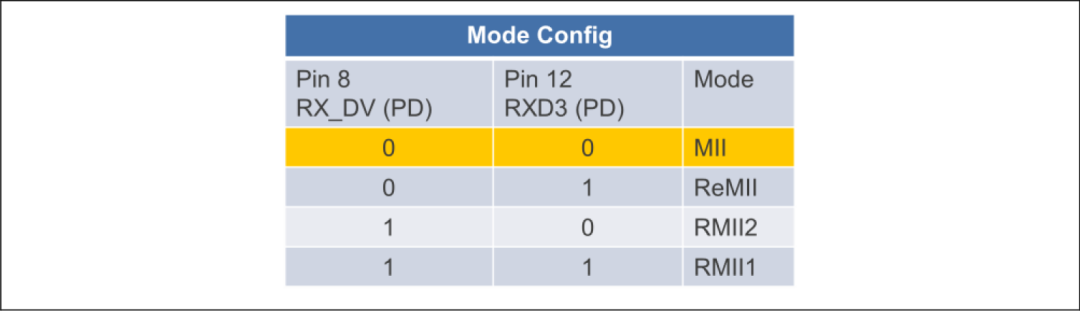

PHY接口模式選擇

每個(gè)PHY芯片的Power on strapping要求不盡相同,由于RX72M ESC僅支持MII模式,因此引腳配置請參考MII對應(yīng)的要求(下表中黃色高亮的部分):

圖4 PHY芯片Power on strapping - Mode Config

三

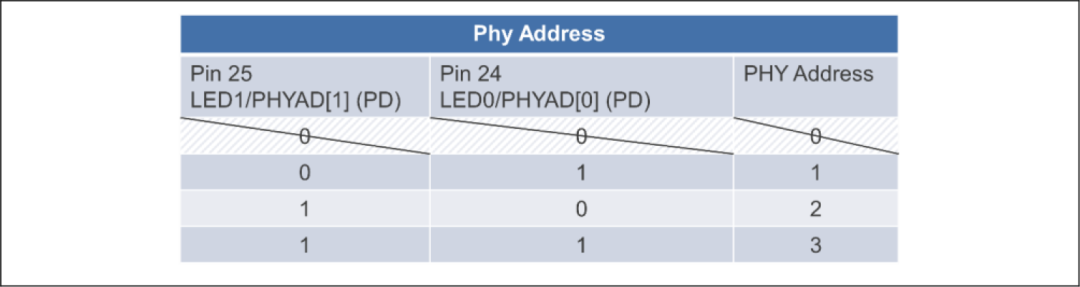

PHY地址配置

對于MCU和PHY芯片通信來說,PHY芯片地址是非常重要的參數(shù)。由于RX72M具備兩個(gè)ESC端口,因此需要通過地址對兩顆PHY芯片進(jìn)行區(qū)分。此情況下,00b地址不可用。請從下表中的3種可選項(xiàng)中選取任意兩個(gè)。

圖5 PHY芯片Power on strapping – Phy Address

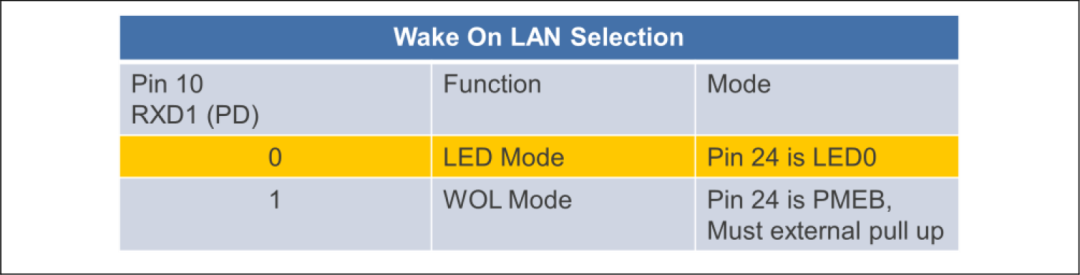

由于需要利用兩顆LED分別指示PHY芯片的Link和Activity狀態(tài),因此將Pin 10 RXD1設(shè)定為LED Mode,如下圖所示:

圖6 PHY芯片 Power on strapping – Wake On LAN Selection

四

系統(tǒng)設(shè)計(jì)流程

有了前面的基礎(chǔ)信息,我們可以按照以下的步驟進(jìn)行系統(tǒng)設(shè)計(jì)。

01

選取板上兩顆PHY芯片的Phy Address,由此決定LED/PHYADD0和LED1/PHYADD1的初始電平。

02

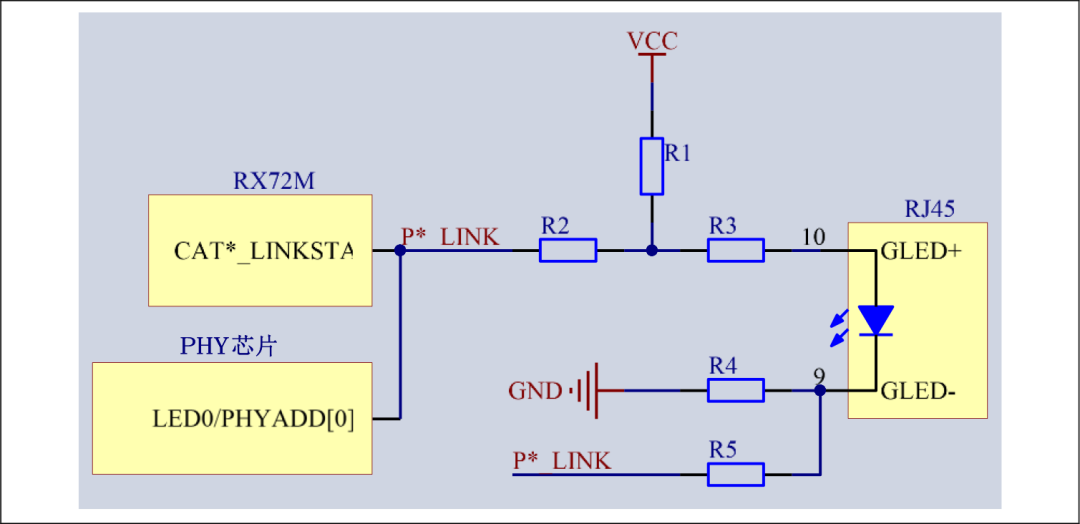

依據(jù)Phy Address決定LED的有效驅(qū)動(dòng)電平,設(shè)計(jì)RJ45接口電路。下圖是RJ45的參考設(shè)計(jì),保留了充分的冗余設(shè)計(jì),可適配不同Phy Address選項(xiàng)。

圖7 RJ45部分參考設(shè)計(jì)

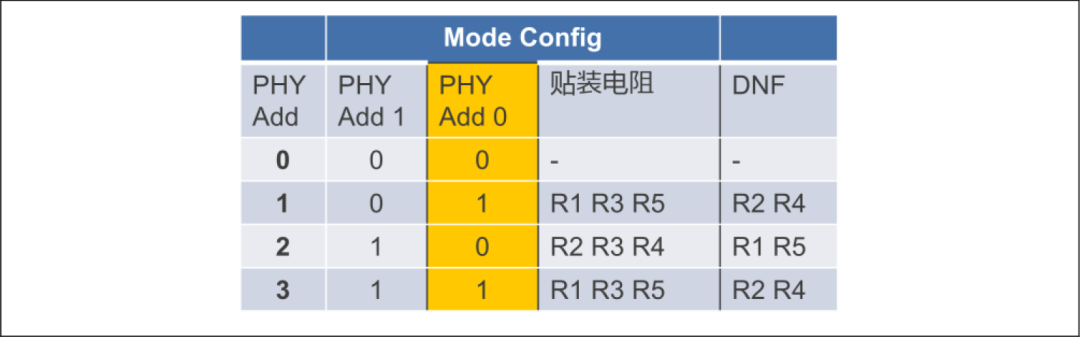

03

以LED0(Green)表示Link Status,LED1(Yellow)表示Activity Status為例,不同的Phy Address選項(xiàng)下,對應(yīng)了不同的電阻配置,參考下表中的說明調(diào)整RJ45中電阻的焊接/不焊接配置。

圖8 Phy Address和電阻設(shè)定對照表

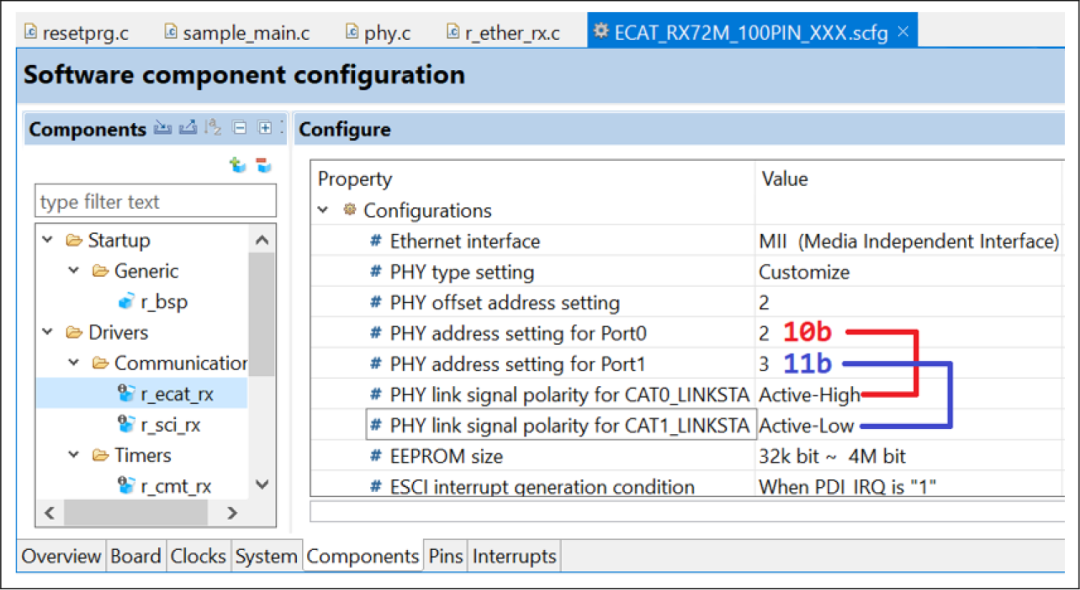

04

對照硬件設(shè)計(jì),需要在RX72M Project的Smart Configurator中進(jìn)行Phy Address和Link Signal Polarity設(shè)定,下圖以Phy Address分別為2和3時(shí)的設(shè)定值。注意,Phy Address的低位(bit 0)決定了Link Signal Active Level。具體地說,如果bit 0為0,則表示上電時(shí)該引腳電平已為低,則PHY芯片Link起來時(shí),該引腳電平會變高,因此Link Signal Active Level應(yīng)設(shè)定為Active-High。bit 0為1時(shí)則剛好相反。

圖9 PHY Address和Link Signal Polarity設(shè)定方式

五

軟件引腳初始化

最后,需要在RX72M代碼(r_ecat_setting_rx72m.c中函數(shù)esc_init())中增加對PHY芯片初始化的配置,使得PHY芯片按照設(shè)定的模式工作。

左右滑動(dòng)查看完整內(nèi)容

//configuration for phy0

write_phyreg((ECAT_CFG_CH0_PHY_ADDRESS - ECAT_CFG_PHY_OFFSET_ADDRESS), 0x1e, 0x40C0); // EXT 40C0

write_phyreg((ECAT_CFG_CH0_PHY_ADDRESS - ECAT_CFG_PHY_OFFSET_ADDRESS), 0x1f, 0x0030);

write_phyreg((ECAT_CFG_CH0_PHY_ADDRESS - ECAT_CFG_PHY_OFFSET_ADDRESS), 0x1e, 0x40C0);

write_phyreg((ECAT_CFG_CH0_PHY_ADDRESS - ECAT_CFG_PHY_OFFSET_ADDRESS), 0x1e, 0x40C3); // EXT 40C3

write_phyreg((ECAT_CFG_CH0_PHY_ADDRESS - ECAT_CFG_PHY_OFFSET_ADDRESS), 0x1f, 0x0320);

write_phyreg((ECAT_CFG_CH0_PHY_ADDRESS - ECAT_CFG_PHY_OFFSET_ADDRESS), 0x1e, 0x40C3);

//configuration for phy1

write_phyreg((ECAT_CFG_CH1_PHY_ADDRESS - ECAT_CFG_PHY_OFFSET_ADDRESS), 0x1e, 0x40C0); // EXT 40C0

write_phyreg((ECAT_CFG_CH1_PHY_ADDRESS - ECAT_CFG_PHY_OFFSET_ADDRESS), 0x1f, 0x0030);

write_phyreg((ECAT_CFG_CH1_PHY_ADDRESS - ECAT_CFG_PHY_OFFSET_ADDRESS), 0x1e, 0x40C0);

write_phyreg((ECAT_CFG_CH1_PHY_ADDRESS - ECAT_CFG_PHY_OFFSET_ADDRESS), 0x1e, 0x40C3); // EXT 40C3

write_phyreg((ECAT_CFG_CH1_PHY_ADDRESS - ECAT_CFG_PHY_OFFSET_ADDRESS), 0x1f, 0x0320);

write_phyreg((ECAT_CFG_CH1_PHY_ADDRESS - ECAT_CFG_PHY_OFFSET_ADDRESS), 0x1e, 0x40C3);

-

mcu

+關(guān)注

關(guān)注

146文章

17317瀏覽量

352643 -

瑞薩

+關(guān)注

關(guān)注

35文章

22310瀏覽量

86746

原文標(biāo)題:RX72M和PHY芯片連接時(shí)的注意事項(xiàng)

文章出處:【微信號:瑞薩MCU小百科,微信公眾號:瑞薩MCU小百科】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

M12連接器安裝指南:詳細(xì)步驟與注意事項(xiàng)

固態(tài)繼電器的使用注意事項(xiàng) 固態(tài)繼電器如何連接

脈沖式充電器的使用注意事項(xiàng)

繞線電感定制的注意事項(xiàng)

LiFePO4設(shè)計(jì)注意事項(xiàng)

TAS5825M的EMC設(shè)計(jì)注意事項(xiàng)

PWM芯片引腳連接的一般步驟和注意事項(xiàng)

24芯M16接口加工注意事項(xiàng)

現(xiàn)場總線的使用方法與注意事項(xiàng)

4芯M16母頭生產(chǎn)注意事項(xiàng)

FMD LINK 使用注意事項(xiàng)

M8連接器5芯關(guān)鍵要點(diǎn)與注意事項(xiàng)有哪些

家用路由器的使用技巧和注意事項(xiàng)**

瑞薩MCU RX72M在EtherCAT應(yīng)用開發(fā)案例

RX72M和PHY芯片連接時(shí)的注意事項(xiàng)

RX72M和PHY芯片連接時(shí)的注意事項(xiàng)

評論