處理器架構的復雜性不斷增加,整體性能擴展有限,因此需要特定領域的架構來確保廣泛的性能擴展。– 這是RISC-V開始獲得動力的時候。RISC-V在數據中心加速器,移動和無線,物聯網等各個領域引起了廣泛關注。的可擴展性。許多行業領導者開始采用RISC-V,因為它的開源可用性縮短了上市時間和成本效益,同時擴大了整體性能,并為創新和自動化留出了空間。

TileLink是一種開放標準的芯片級互連,設計用于RISC-V處理器。它還支持其他國際審計準則。

TileLink 是一種易于實現的緩存一致性總線協議,可在片上系統 (SoC) 中用于連接加速器、通用多處理器、協處理器、DMA 引擎以及簡單或復雜的設計。

想知道TileLink有什么商店嗎?

快速可擴展的互連,提供低延遲和高吞吐量

物理尋址的共享內存子系統,可通過可擴展、分層組合的點對點網絡實現

在系統中同時使用的緩存或非緩存主節點的多層緩存一致性訪問

TileLink的主要功能:

專為可驗證的死鎖自由而設計(適用于任何符合標準的 SoC)

通過支持并發操作的無序完成來提高吞吐量

漸進一致性級別復雜性

基于地址空間的屬性

物理上獨立的通道

TileLink 遵循有向無環圖 (DAG) 拓撲,其中代理是頂點,鏈路是從主接口定向到輔助接口的邊。每個鏈路由一組2個強制通道(通道A和D)和3個可選通道(TL-C所需的通道B,C和E)組成。為了確保死鎖自由,TileLink 指定了要嚴格遵循的通道之間的優先級:

A << B << C << D << E 是通道 A、B、C、D 和 E 的優先級遞增順序。

請求始終由主請求通道啟動,然后等待輔助響應通道的響應。

三個一致性級別

TileLink可以支持基于TL-UL,TL-UH&TL-C的3個一致性級別TL,GET,Atomic,Hint,Acquire,Probe和Release等操作。

TileLink 實現有效-就緒握手,但保留有效和就緒斷言-取消斷言,彼此獨立,允許主服務器丟棄輔助服務器尚未接受的任何消息。TileLink 支持無序、FIFO 順序、延遲和并發響應,但不支持交錯。

由于 DAG 確保 TileLink 對每個請求的響應,因此 TileLink 中禁止超時。但是,到舊版總線網橋的 TileLink 應實現超時,以適應第一個轉發進度規則。如果來自舊總線的響應沒有及時到達,則必須丟棄請求并插入TileLink錯誤響應。

審核編輯:郭婷

-

處理器

+關注

關注

68文章

19408瀏覽量

231186 -

總線

+關注

關注

10文章

2903瀏覽量

88396 -

RISC-V

+關注

關注

45文章

2323瀏覽量

46592

發布評論請先 登錄

相關推薦

stm32標準庫外部中斷解讀

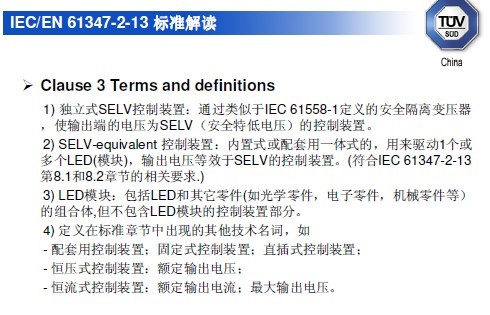

歐盟最新家電標準 EN/IEC 55014解讀

直播預告丨OpenHarmony標準系統多媒體子系統之音頻解讀

直播預告丨OpenHarmony標準系統多媒體子系統之視頻解讀

全面解讀環保標準之ROHS

全面解讀環保標準之GreenGuard

Matter技術標準中文解讀,快速讀懂核心標準、設備類型庫和應用功能集

解讀新的TileLink標準

解讀新的TileLink標準

評論