Verdi是一個功能強大的debug工具,可以配合不同的仿真軟件進行debug,很多企業常用的就是VCS+Verdi或或者Xcelium(xrun)+Verdi的方式進行代碼的仿真與檢查,Verdi使用情形主要是IC驗證工程師(Debug),IC設計工程師(Review)。總之,Verdi很重要,作為一名ICer要是不會用Verdi,確實說不過去。

一、Verdi環境配置

(一)公司 - 一般拿來直接用

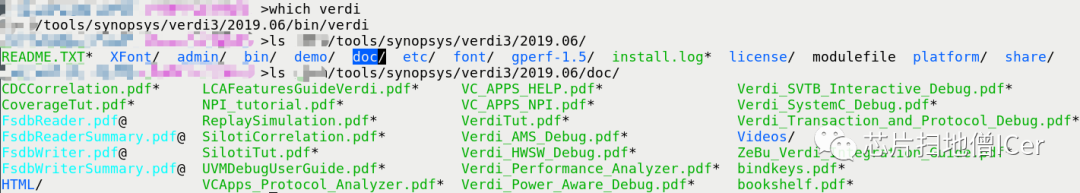

1. 在芯片設計公司中,九成公司應該都配備了Verdi,一般都會放在公司服務器目錄的Tools目錄下,我們可以通過which命令查看任何公司購買的EDA Tools所在路徑,查看各種版本/對應文檔/配置等:

2. 有些時候,我們需要切換Verdi版本,來滿足不同項目或其他需求,在.cshrc中配置 或 直接module load 對應Verdi版本,最后module list查看是否load成功。

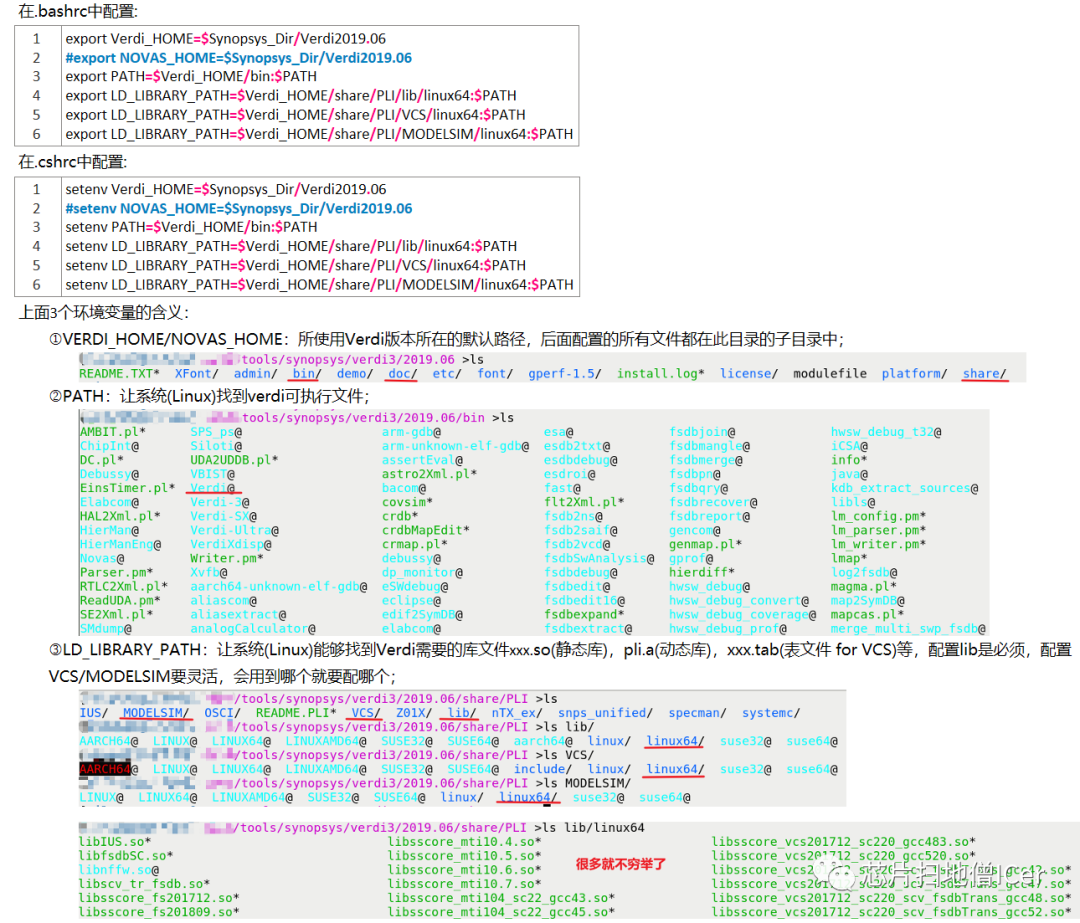

(二)其他 - 需自己摸索配置再用 (考慮排版+代碼風格,直接上圖) ? ?

? ?

二、配置波形文件“三方法”“八奇技”

FSDB(FastSignal Database)是Verdi支持的文件格式,用于保存仿真產生的信號波形。 據Verdi文檔說明,FSDB比標準的VCD格式節省磁盤空間,處理速度更快。

(一)常用“三方法”:

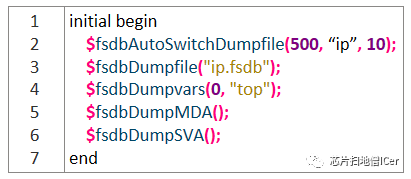

1. (最常用) 一般是在testbench(驗證環境,簡稱tb)中的top.sv文件里,創建個initial塊結合$fsdbDumpxxx()命令來配置:

提醒:使用這種方法,vcs編譯前需要添加-debug_access選項。

2. (不常用) VCS添加編譯選項"+vcs+fsdbon":

這樣指定仿真過程生成.fsdb格式的波形,默認則保存成名為novas.fsdb的波形文件;

注

意的是,仿真過程會將整個design給dump下來,同時會自動添加 -debug_access 選項。

另外,配置過程中若出錯,首先檢查一下LD_LIBRARY_PATH是否配置對,目錄下有沒有Verdi需要的庫文件xxx.so(靜態庫),pli.a(動態庫),xxx.tab(表文件 for VCS)等,一般都是這里沒配對導致沒生成波形而報錯;

提醒:vcs+fsdbon和tb中用$fsdbdumpvar()選一種方式即可;

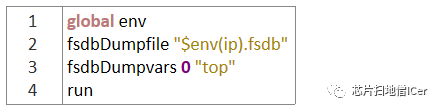

3. (不常用) 使用UCLI命令: UCLI:Unified Command Line Interface

UCLI其實就是vcs的命令交互模式,需要在編譯時加入參數 (-ucli) 以開啟ucli,否則ucli交互時只能使用簡單的'run'、'dump'、'quit'命令。

啟動方式例如:./simv -ucli

該方法與方法1基本一樣,均是使用fsdbDumpvars/fsdbDumpfile等命令,不同之處在于使用的方式和便捷程度,與方法1相比,該方法可以在不重新編譯的情況下,通過修改.ucli.cmd文件中的命令,來指定需要dump波形的模塊和層級,從而節省編譯帶來的資源消耗。

得注意的是,使用fsdbDumpvars/fsdbDumpfile等命令時,不需要像方法1使用時,前方使用符號: $。

執行仿真的過程中,通過./simv -ucli -i.ucli.cmd方式給入,.ucli.cmd(名字隨便取,但格式不能變)中存放命令舉例如下:

提醒:使用這種方法,vcs編譯前需要添加-debug_access選項。

(二)常用命令“八奇技”(結合例子看容易理解):

1. $fsdbDumpon - 打開 FSDB dumping;

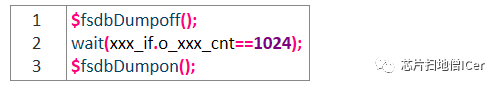

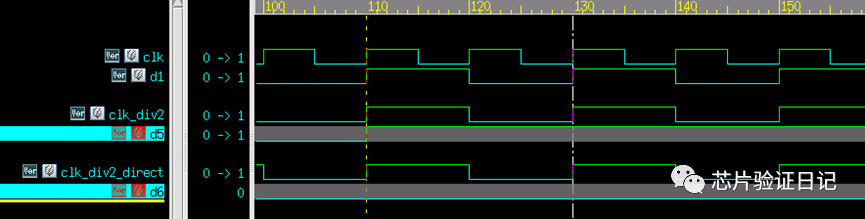

2. $fsdbDumpoff - 關閉 FSDB dumping; 上述兩個命令,一般搭配wait()函數使用,更加靈活,eg:

表示之前未dump波形,直到等到o_xxx_cnt==1024時,才開始dump波形;

3. $fsdbDumpfile("fsdb_name", limit_size) - 指定dump文件;

| fsdb_name | - 表示指定的fsdb文件名,如"ip.fsdb" |

| limit_size | - 表示dump波形的最大size(多少MB)- 可不配置 |

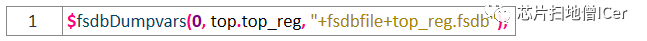

4. $fsdbDumpvars(depth,instance, "option=") - dump指定模塊的信號; 這個命令可以多次使用,但一般不使用多次,使用多次目的是:想用來dump不同instance的波形,想達到相同目的其實有更加靈活的方法 ——“建立dump_scope.list + $fsdbDumpvarsToFile()” (后面會介紹);

| depth | - 0 表示dump instance以下所有層級的信號(常用) - 1 表示只dump instance這一層的信號 |

| instance | -指定dump的hierarchy,如 dut.top.xxx |

| option | - dump時可以選擇的一些選項:- 可不配置 |

| "+mda" | - 表示dump memory或者MDA(多維數據)的數據; |

| "+packedmda" | - 表示dump 壓縮的memory數據; |

| "+functions" | - 表示dump function和task里的信號; |

| "+all" | -表示dump all; |

| "+Reg_Only" | - 表示只dump reg類型的數據; |

| "+strength" | - 表示開啟強力dump開關; |

| "+struct" | - 表示dump struct數據(默認開); |

| "+power" | - 表示dump power相關信號的數據(默認開); |

| "+fsdbfile" |

- 表示直接dump指定的hierarchy的fsdb文件名字,eg:  |

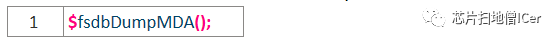

5. $fsdbDumpMDA(depth, instance,"options") - dump指定模塊中的多維數組,內部參數含義同上; eg_1:如果想更方便,可直接什么參數都不配,即默認都dump

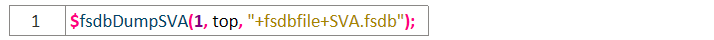

6. $fsdbDumpSVA(depth, instance, "option") - dump指定模塊中的assertion,內部參數含義同上; eg_1:將該instance (top)下所有assert全部dump到SVA.fsdb中

eg_2:如果想更方便,可直接什么參數都不配,即默認都dump

7.$fsdbAutoSwitchDumpfile(file_size,"fsdb_name",number_of_files,"log_file_name", "+fsdb+no_overwrite") - 波形過大/資源緊張情況,靈活使用拆分Dump波形很有用

| file_size | 波形文件大小限制,單位為MB,最小為10M,若值小于10MB則默認10MB; |

| "fsdb_name" | 波形文件的名字,在實際加載波形時,文件名為fsdb_name_000.fsdb, fsdb_name_001.fsdb …; |

| number_of_files | 最多可以加載多少個fsdb_size這么大的波形文件,如果寫為0,則默認沒有限制; |

| "log_file_name" | 指定log文件的名字,log文件中會記錄每段波形的起始和中止時間; - 可不配置 |

| "+fsdb+no_overwrite" | 當number_of_files限制的個數達到時停止dump波形,反之,一旦超出限制,會從頭dump,這樣會一定程度上覆蓋掉起初的波形文件;- 可不配置 |

eg_1:單個波形文件為500MB,最大可以加載10個這么大的文件,每段波形的起始和中止時間記錄在fsdb.log中,并具備防overwrite的限制;

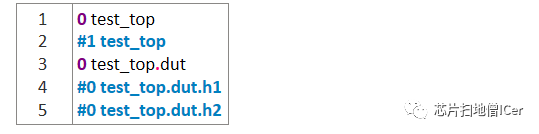

8. $fsdbDumpvarsToFile("./dump_scope.list"); - 將需要dump的hierarchy以及depth放到一個文件里吃進來,波形過大/資源緊張情況,靈活使用選取必要波形Debug; ./ - 表示當前路徑,也就是dump_scope.list要與top.sv在同一路徑,當然也可以靈活改變路徑; eg_1:dump_scope.list (0/1代表深度,用法通上述函數一致;#用于注釋)

審核編輯:劉清

-

IC設計

+關注

關注

38文章

1302瀏覽量

104287 -

EDA工具

+關注

關注

4文章

268瀏覽量

31937 -

VCS

+關注

關注

0文章

80瀏覽量

9647

原文標題:Verdi環境配置、生成波形的“三方法”和“八奇技”

文章出處:【微信號:處芯積律,微信公眾號:處芯積律】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

請教VCS和verdi怎么聯合使用

VCS仿真卡住,為什么無法生成verdi波形文件呢?

怎么修改verdi軟件波形背景顏色?

Verdi使用技巧 連續有效信號量測方法

vcs和verdi的調試及聯合仿真案例

如何通過自動化腳本實現Questasim和Verdi的聯合仿真

Verdi環境配置、生成波形的方法

Verdi環境配置、生成波形的方法

評論