1、 概述

隨著超大規(guī)模集成電路的發(fā)展,芯片工作電壓越來(lái)越低,而工作速度越來(lái)越快,功耗越來(lái)越大。芯片內(nèi)部成千上萬(wàn)個(gè)晶體管組成的門(mén)電路、組合邏輯、寄存器以及其他邏輯功能電路,芯片外部電源引腳提供給內(nèi)部晶體管一個(gè)公共的工供電節(jié)點(diǎn),因此內(nèi)部晶體管狀態(tài)的轉(zhuǎn)換會(huì)引起電源噪聲在芯片內(nèi)部的傳遞,從而影響芯片的正常工作。除了對(duì)芯片本身工作狀態(tài)產(chǎn)生影響外,電源噪聲會(huì)影響晶振、鎖相環(huán)的抖動(dòng)特性等,產(chǎn)生其他電磁干擾的問(wèn)題。

2、 噪聲來(lái)源

第一,穩(wěn)壓穩(wěn)壓電源芯片本身的輸出并不是恒定的,會(huì)有一定的波紋。 這是由穩(wěn)壓芯片自身決定的,一旦選好了穩(wěn)壓電源芯片,對(duì)這部分噪聲我們只能接受,無(wú)法控制。穩(wěn)壓電源大體分為線(xiàn)性電源和開(kāi)關(guān)電源兩種。線(xiàn)性電源(LDO)通常具有很好的輸出紋波特性,電源本身輸出噪聲低,供電穩(wěn)定,但是輸出功率不大,轉(zhuǎn)換效率低。開(kāi)關(guān)電源(DC-DC)可以輸出很大的電流,轉(zhuǎn)換效率高,但是通常輸出紋波較大。

第二,穩(wěn)壓電源無(wú)法實(shí)時(shí)響應(yīng)負(fù)載對(duì)于電流需求的快速變化。 穩(wěn)壓電源芯片通過(guò)感知其輸出電壓的變化,調(diào)整其輸出電流,從而把輸出電壓調(diào)整回額定輸出值。多數(shù)常用的穩(wěn)壓源調(diào)整電壓的時(shí)間在毫秒到微秒量級(jí)。因此,對(duì)于負(fù)載電流變化頻率在直流到幾百KHz之間時(shí),穩(wěn)壓源可以很好的做出調(diào)整,保持輸出電壓的穩(wěn)定。當(dāng)負(fù)載瞬態(tài)電流變化頻率超出這一范圍時(shí),穩(wěn)壓源的電壓輸出會(huì)出現(xiàn)跌落,從而產(chǎn)生電源噪聲。現(xiàn)在,微處理器的內(nèi)核及外設(shè)的時(shí)鐘頻率已經(jīng)超過(guò)了600兆赫茲,內(nèi)部晶體管電平轉(zhuǎn)換時(shí)間下降到800皮秒以下。這要求電源分配系統(tǒng)必須在直流到1GHz范圍內(nèi)都能快速響應(yīng)負(fù)載電流的變化,但現(xiàn)有穩(wěn)壓電源芯片不可能滿(mǎn)足這一苛刻要求。我們只能用其他方法補(bǔ)償穩(wěn)壓源這一不足,比如電源去耦方法。

第三,負(fù)載瞬態(tài)電流在電源路徑阻抗和地路徑阻抗上產(chǎn)生的壓降。 PCB板上任何電氣路徑不可避免的會(huì)存在阻抗,不論是完整的電源平面還是電源引線(xiàn)。對(duì)于多層板,通常提供一個(gè)完整的電源平面和地平面,穩(wěn)壓電源輸出首先接入電源平面,供電電流流經(jīng)電源平面,到達(dá)負(fù)載電源引腳。地路徑和電源路徑類(lèi)似,只不過(guò)電流路徑變成了地平面。完整平面的阻抗很低,但確實(shí)存在。如果不使用平面而使用引線(xiàn),那么路徑上的阻抗會(huì)更高。另外,引腳及焊盤(pán)本身也會(huì)有寄生電感存在,瞬態(tài)電流流經(jīng)此路徑必然產(chǎn)生壓降,因此負(fù)載芯片電源引腳處的電壓會(huì)隨著瞬態(tài)電流的變化而波動(dòng),這就是阻抗產(chǎn)生的電源噪聲。在電源路徑表現(xiàn)為負(fù)載芯片電源引腳處的電壓軌道塌陷,在地路徑表現(xiàn)為負(fù)載芯片地引腳處的電位和參考地電位不同。

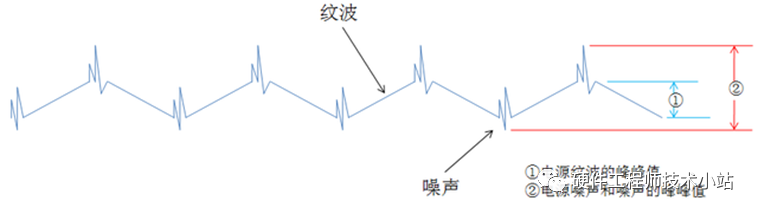

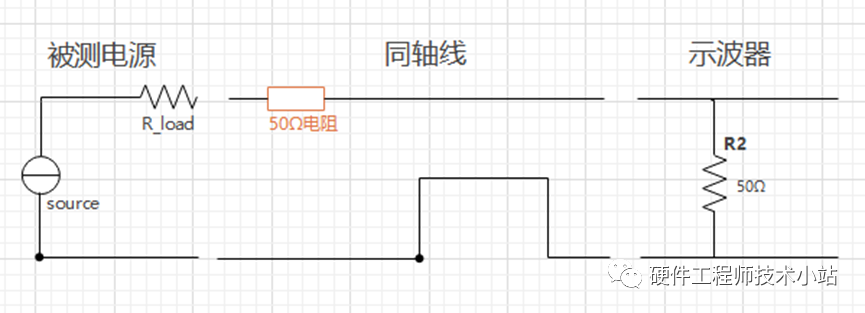

電源紋波和電源噪聲是一個(gè)比較容易混淆的概念,如下圖所示,藍(lán)色標(biāo)注為

電源紋波,紅色標(biāo)注為電源噪聲。電源紋波的頻率為開(kāi)關(guān)頻率的基波和諧波,而

噪聲的頻率成分高于紋波,是由板上芯片高速I(mǎi)/O的開(kāi)關(guān)切換產(chǎn)生的瞬態(tài)電流、

供電網(wǎng)絡(luò)的寄生電感、電源平面和地平面之間的電磁輻射等諸多因素產(chǎn)生的。因

此,在電源IC輸出側(cè)測(cè)量電源紋波,而在SINK端(耗電芯片端)測(cè)量的是電源噪聲。

圖:紋波和噪聲的區(qū)別

3、基本概念

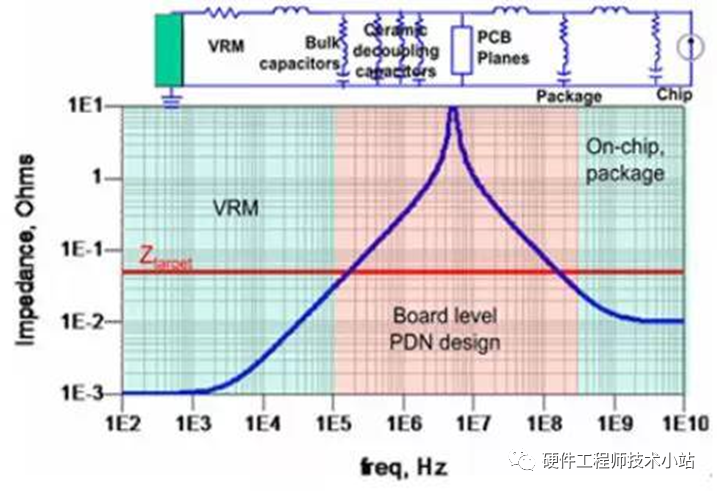

什么是PDN?

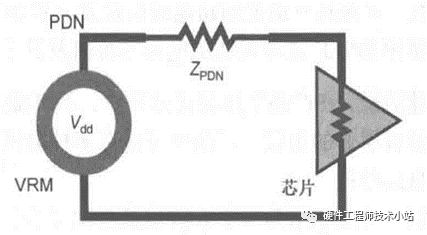

電源分配網(wǎng)絡(luò)又稱(chēng)為電源配送網(wǎng)絡(luò),包含了從穩(wěn)壓電源(VRM)到芯片的焊盤(pán),再到返回電流路徑上的所有互連。PDN系統(tǒng)主要有以下幾部分組成:VRM(電源芯片或電源模塊)、PCB上的電容、PCB上的電源和地平面、芯片封裝內(nèi)的電容、封裝內(nèi)的電源和地網(wǎng)絡(luò)、Die上的電容。對(duì)于PCB板級(jí)設(shè)計(jì)來(lái)說(shuō),盡管不可能得到芯片內(nèi)PDN系統(tǒng)詳細(xì)信息,但是并不意味著它不起作用,如何將PCB和芯片內(nèi)的PDN系統(tǒng)進(jìn)行聯(lián)合設(shè)計(jì)也是難點(diǎn)之一。

圖:電源分配系統(tǒng)的構(gòu)成

電源分配系統(tǒng)在現(xiàn)代電路占有越來(lái)越重要的作用,一方面,芯片的開(kāi)關(guān)速度不斷提高,高頻瞬態(tài)電流的需求越來(lái)越大。另一方面,芯片的功能不斷增加,功能越來(lái)越強(qiáng)大,芯片的功耗也隨之增加。在高頻瞬態(tài)電流需求的情況下滿(mǎn)足PDN系統(tǒng)的噪聲要求,對(duì)設(shè)計(jì)提出了很大的挑戰(zhàn),PDN系統(tǒng)的作用主要包含兩個(gè)方面:

1) 為負(fù)載提供干凈的供電電流。

2) 為信號(hào)提供低噪聲的參考路徑(返回路徑)

芯片最關(guān)心的是其焊盤(pán)上的電壓,假設(shè)從VRM到芯片沒(méi)有電流流動(dòng),那么在這路徑上不會(huì)有電壓降,芯片得到的電壓接近于VRM輸出電壓。如果芯片消耗的是一個(gè)恒定直流電流,那么由于PDN系統(tǒng)中的串聯(lián)電阻存在,該直流電流將在電源分配網(wǎng)絡(luò)互連上產(chǎn)生壓降,通常稱(chēng)為 IR壓降 。當(dāng)芯片上的電流發(fā)生波動(dòng),電源分配網(wǎng)絡(luò)上的壓降也會(huì)隨之波動(dòng),從而使芯片焊盤(pán)上的電壓也產(chǎn)生波動(dòng)。

實(shí)際除了串聯(lián)電阻造成的電阻性阻抗,PDN互連中還包括了感性阻抗和容性阻抗,從片上焊盤(pán)看過(guò)去的電源分配網(wǎng)絡(luò)阻抗,通常是一個(gè)和頻率相關(guān)的阻抗,記為Z(f)

圖:從VRM到芯片,由于PDN的阻抗造成的壓降

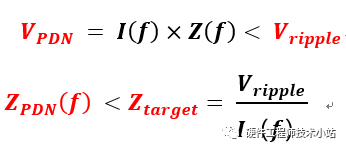

當(dāng)具有一定頻譜寬度的波動(dòng)電流I(f)通過(guò)電源分配網(wǎng)絡(luò)的復(fù)阻抗時(shí)。電源分配網(wǎng)絡(luò)上將會(huì)產(chǎn)生電壓降:

V(f)表示電壓,是隨頻率f變化的函數(shù),I(f)表示芯片消耗電流的頻譜,Z(f)表示由芯片焊盤(pán)看到的電源分配網(wǎng)絡(luò)阻抗曲線(xiàn)。

這一壓降表示VRM輸出的恒定電壓芯片是得不到的,在進(jìn)入芯片前已被改變。芯片焊盤(pán)上的電壓變化必須小于某一電壓噪聲誤差,比如要求為額定電壓的5%。這就要求電源分配網(wǎng)絡(luò)阻抗必須低于某一阻抗值,即目標(biāo)阻抗:

VPDN表示電源分配網(wǎng)絡(luò)上實(shí)際的噪聲壓降(V);

Vripple表示芯片允許的電壓噪聲誤差(V);

I(f)表示芯片消耗電流的頻譜(A);

Z PDN (f)表示由芯片看過(guò)去的電源分配網(wǎng)絡(luò)阻抗曲線(xiàn)(Ω);

Ztarget表示電源分配網(wǎng)絡(luò)所允許的最大阻抗(Ω)

因此電源分配網(wǎng)絡(luò)上的軌道塌陷或電壓噪聲的根本原因在于,流過(guò)電源分配網(wǎng)絡(luò)阻抗的芯片電流導(dǎo)致互連上出現(xiàn)了電壓降。要保持芯片供電電壓穩(wěn)定,就需要保持電源分配網(wǎng)絡(luò)阻抗低于目標(biāo)阻抗,這就電源分配網(wǎng)絡(luò)設(shè)計(jì)中最根本的指導(dǎo)原則

如何理解去耦電容?

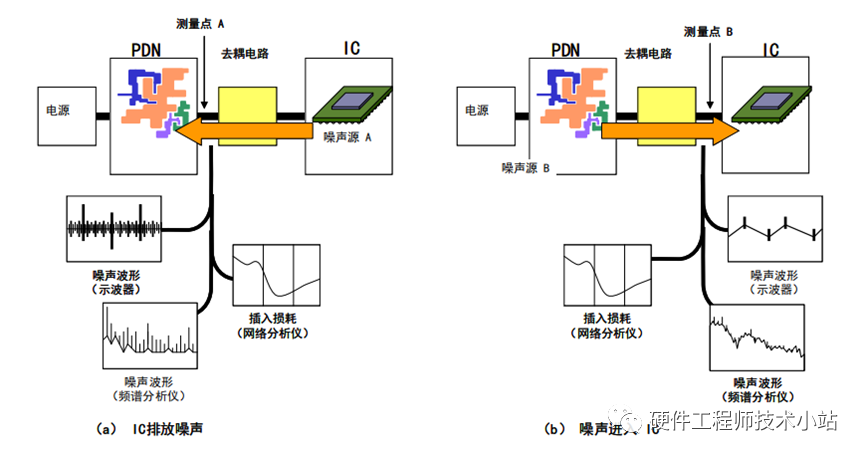

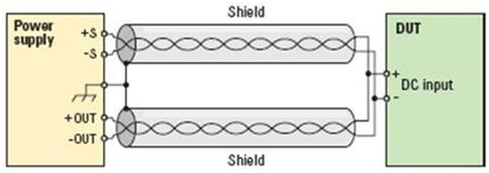

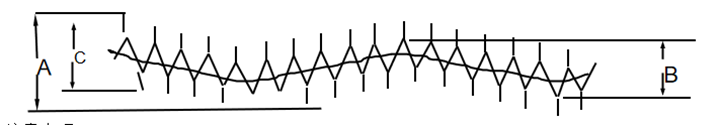

為了使負(fù)載芯片的供電滿(mǎn)足要求,通常會(huì)在芯片的周?chē)煤芏嚯娙葸B接到電源平面上,這些電容稱(chēng)為去耦電容。 去耦電路主要有三種功能:①抑制噪聲,②暫時(shí)供應(yīng)電流,③形成信號(hào)返回通道。 在這三種功能中,第一種功能抑制噪聲是針對(duì) IC 電源泄漏的噪聲進(jìn)行過(guò)濾,并且切斷從外部進(jìn)入 IC 的噪聲。當(dāng)懷疑噪聲從 IC 泄漏時(shí),在 PDN(測(cè)量點(diǎn) A)側(cè)進(jìn)行測(cè)量,當(dāng)懷疑噪聲從外源進(jìn)入 IC 時(shí),在 IC電源端子(測(cè)量點(diǎn) B)側(cè)進(jìn)行測(cè)量。

去耦電容之所以能夠減小電源噪聲,可以從多個(gè)角度進(jìn)行解釋?zhuān)旅鎻膬?chǔ)能和阻抗的兩個(gè)角度進(jìn)行說(shuō)明去耦電容減小電源噪聲的原理

1、 從儲(chǔ)能的角度來(lái)理解

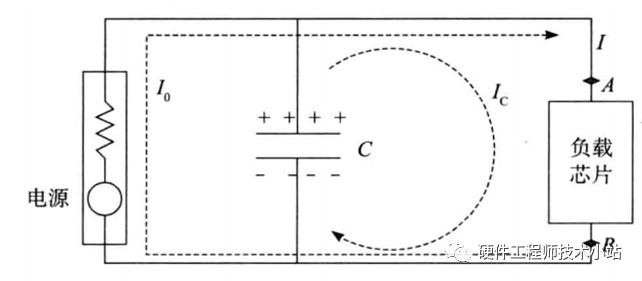

帶有去耦電容的供電系統(tǒng)可以等效為下圖所示的簡(jiǎn)化結(jié)構(gòu)。我們把電源系統(tǒng)分成電源模塊和去耦電容兩部分,圖中電容代表了所有外加去耦電容的組合,電源模塊和去耦電容聯(lián)合起來(lái)共同為AB兩點(diǎn)之間的負(fù)載芯片供電。

圖 去耦電容儲(chǔ)能等效電路

當(dāng)負(fù)載電流保持不變,穩(wěn)態(tài)情況下,負(fù)載芯片處的電壓是恒定的,因而電容兩端電壓也是恒定的,與負(fù)載兩端電壓一致,流經(jīng)電容的電流 IC為0,負(fù)載電流由電源模塊提供,即圖中的IO此時(shí)電容兩端存在電壓,因此電容上存儲(chǔ)了相當(dāng)數(shù)量的電荷,其電荷數(shù)量和電容量有關(guān)。

當(dāng)負(fù)載電流發(fā)生瞬間變化時(shí),由于負(fù)載芯片內(nèi)部晶體管電平轉(zhuǎn)換速度極快,必須在極短的時(shí)間內(nèi)為負(fù)載芯片提供足夠的電流。但是穩(wěn)壓電源無(wú)法很快響應(yīng)負(fù)載電流的變化,電流I不會(huì)馬上變化滿(mǎn)足負(fù)載瞬態(tài)電流的要求,因此負(fù)載芯片感受到的電壓會(huì)降低。去耦電容也同時(shí)感受到電壓變化,對(duì)于電容來(lái)說(shuō)電壓變化必然產(chǎn)生電流,此時(shí)電容對(duì)負(fù)載放電,電流IC不再為0,要為負(fù)載芯片提供電流。根據(jù)電容上電壓和電流之間的關(guān)系∶

理想情況下,只要電容量C足夠大,放電并為負(fù)載提供瞬態(tài)電流只會(huì)引起電容兩端很小的電壓變化,這樣就保證了負(fù)載芯片電壓的變化在容許的范圍內(nèi)。這里,相當(dāng)于電容預(yù)先存儲(chǔ)了一部分電能,在負(fù)載需要的時(shí)候釋放出來(lái),即電容是儲(chǔ)能元件。儲(chǔ)能電容的存在使負(fù)載消耗的能量得到快速補(bǔ)充,因此保證了負(fù)載兩端電壓不至于有太大變化,此時(shí)電容擔(dān)負(fù)的是局部電源的角色。

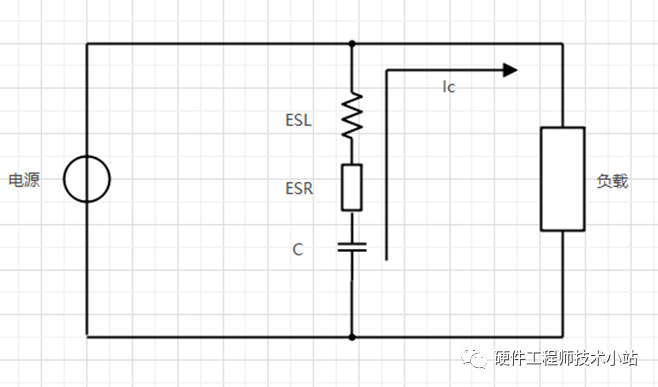

從儲(chǔ)能角度理解電容容易造成一種錯(cuò)覺(jué),認(rèn)為電容越大越好。而且容易誤導(dǎo)大家認(rèn)為儲(chǔ)能作用發(fā)生在低頻段,不容易向高頻擴(kuò)展。實(shí)際上,去耦電容工作在全頻段。我們把一個(gè)去耦電容中的一個(gè)拿出來(lái)進(jìn)行分析,實(shí)際電容的電路模型如下所示,由三部分組成:C+ESR+ESL

假設(shè)在低頻段,由于低頻信號(hào)在電感上產(chǎn)生的感抗可以忽略,所以低頻段電容的ESL可以近似為0,當(dāng)負(fù)載瞬間需要大電流的時(shí)候,電容通過(guò)ESR給負(fù)載供電,實(shí)時(shí)性很高,只是ESR消耗了一部分電量。由于頻率比較低,所以放電時(shí)間(頻率的倒數(shù))比較長(zhǎng),所以需要電容的容量大一些來(lái)滿(mǎn)足長(zhǎng)時(shí)間放電。

假設(shè)我們將頻率提高到MHz級(jí)別,那么當(dāng)負(fù)載瞬時(shí)變化的時(shí)候,ESL形成的感抗不容忽視,這個(gè)感抗會(huì)形成反向電動(dòng)勢(shì)阻止電容給負(fù)載充電,負(fù)載上獲得的電流瞬態(tài)性能比較差,盡管電容容量很大,但由于ESL較大(一般電容的容量越大,電容本身的ESL也就越大),此時(shí)的大容量?jī)?chǔ)能發(fā)揮不了作用。實(shí)際上,頻率較高,電容給負(fù)載供電的時(shí)間縮短(頻率的倒數(shù)),也不需要電容有那么大的容量。對(duì)于高頻,關(guān)鍵的因素是ESL,要降低電容的ESL,選擇小封裝的小電容,ESL顯著降低,這就是為什么我們高頻選擇小電容的原因,另外走線(xiàn)長(zhǎng)度引入的電感也會(huì)折算到ESL參數(shù)里,所以小電容一定要靠近pin。

2、 從阻抗的角度來(lái)理解

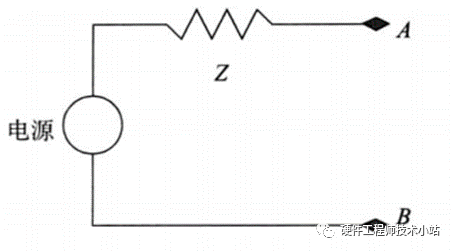

從阻抗的角度理解電容退耦,可以給我們?cè)O(shè)計(jì)電源分配系統(tǒng)帶來(lái)極大的方便。實(shí)際上,電源分配系統(tǒng)設(shè)計(jì)的最根本的原則就是使阻抗最小。最有效的設(shè)計(jì)方法就是在這個(gè)原則指導(dǎo)下產(chǎn)生的。根據(jù)上圖我們?nèi)サ糌?fù)載芯片,僅觀察供電系統(tǒng)本身,如下圖所示。從 AB兩點(diǎn)向左看過(guò)去,穩(wěn)壓電源以及去耦電容組合在一起,可以看成是一個(gè)復(fù)合的電源系統(tǒng)。對(duì)這個(gè)復(fù)合電源系統(tǒng)的要求是;不論 AB 兩點(diǎn)間負(fù)載的瞬態(tài)電流如何變化,都能保證 AB 兩點(diǎn)間的電壓保持穩(wěn)定,即 AB兩點(diǎn)間電壓變化很小。

我們可以用一個(gè)等效電源模型表示上面這個(gè)復(fù)合的電源系統(tǒng):

對(duì)于這個(gè)電路可寫(xiě)出如下等式∶△V= Z·△I

我們的最終設(shè)計(jì)目標(biāo)是,不論 AB兩點(diǎn)間負(fù)載瞬態(tài)電流如何變化,都要保持 AB 兩點(diǎn)間電壓變化范圍很小,根據(jù)上式,這要求電源系統(tǒng)的阻抗 Z要足夠小。電源系統(tǒng)中去耦電容和電源模塊是并聯(lián)關(guān)系,對(duì)于變化的瞬態(tài)電流,由于具有交流特性,去耦電容表現(xiàn)出低阻抗的特性(通交流,阻直流)。從端口看進(jìn)去對(duì)交流成分表現(xiàn)出的阻抗很低。因此從等效的角度出發(fā),可以說(shuō)去耦電容降低了復(fù)合電源系統(tǒng)的阻抗。電源PDN做的就是如何在各個(gè)頻率段下阻抗盡可能小。理論上,并聯(lián)無(wú)數(shù)個(gè)電容,電源內(nèi)阻總可以無(wú)限接近于0,從而電源無(wú)限接近于恒壓源或恒流源。

總結(jié):

綜上而言,PCB電容都不是理想電容,而是存在寄生效應(yīng)的(ESL、ESR);

PCB電容的阻抗特性在自諧振頻率點(diǎn)阻抗最小,低于自諧振頻率阻抗呈容性,高于自諧振頻率呈感性;

通常容值越小,電容的自諧振頻率越高,可用于更高的頻率去耦。因?yàn)橐种聘哳l噪聲,小電容的回路電感要控制很小,所以需要放置到離電源地管腳很近的位置并合理扇出,多個(gè)小電容并聯(lián)可以降低回路電感;

不同容值的自諧振頻率點(diǎn)不同,不同容值的去耦電容并聯(lián)可以取得更大范圍內(nèi)的頻率去耦,在工程上通常用不同數(shù)量級(jí)容值的電容搭配進(jìn)行設(shè)計(jì)去耦方案。

-

寄存器

+關(guān)注

關(guān)注

31文章

5363瀏覽量

121164 -

微處理器

+關(guān)注

關(guān)注

11文章

2274瀏覽量

82776 -

晶體管

+關(guān)注

關(guān)注

77文章

9746瀏覽量

138899 -

寄生電感

+關(guān)注

關(guān)注

1文章

156瀏覽量

14631 -

電源芯片

+關(guān)注

關(guān)注

43文章

1100瀏覽量

77271

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

如何降低測(cè)試中的噪聲

電源紋波和噪聲的測(cè)試測(cè)量和分析

基于FPGA的軟硬件協(xié)同測(cè)試設(shè)計(jì)影響因素分析與設(shè)計(jì)實(shí)現(xiàn)

關(guān)于相位噪聲測(cè)試技術(shù)的介紹和應(yīng)用

【硬件篇之電源紋波噪聲測(cè)試】

硬件測(cè)試-噪聲的測(cè)試分析(2)

硬件測(cè)試-噪聲的測(cè)試分析(3)

干貨分享 | 1/f噪聲測(cè)試方案詳解(附直播回顧)

如何測(cè)試電源紋波和噪聲?納米軟件電源模塊測(cè)試系統(tǒng)如何助力測(cè)試?

新能源汽車(chē)出風(fēng)口噪聲測(cè)試案例

PRBTEK分享常用的電源紋波噪聲測(cè)試方法

硬件測(cè)試-噪聲的測(cè)試分析(1)

硬件測(cè)試-噪聲的測(cè)試分析(1)

評(píng)論