在過去的幾年里,數(shù)據(jù)領(lǐng)域陸續(xù)出現(xiàn)重大技術(shù)突破,特別是在數(shù)據(jù)傳輸和處理速度方面。AI(人工智能)、IoT(物聯(lián)網(wǎng))、5G 等科技日益成熟且應(yīng)用廣泛,其中PCI Express(PCIe)技術(shù)在這些產(chǎn)業(yè)中扮演著重要的角色。PCIe 5.0的出現(xiàn)引起數(shù)據(jù)領(lǐng)域的高度關(guān)注,因?yàn)樗谛阅芎退俣确矫鎺碇卮蟾倪M(jìn)。伴隨著最新的PCB模擬技術(shù),PCIe 5.0可以徹底改變我們對數(shù)據(jù)處理的認(rèn)知和使用方式。

究竟什么是PCIe?

PCIe 是?種高速串行計(jì)算機(jī)擴(kuò)展總線標(biāo)準(zhǔn),作為計(jì)算機(jī)系統(tǒng)不同組件之間的數(shù)據(jù)傳輸,例如CPU與GPU或其它加速處理器之間傳輸數(shù)據(jù)都依賴這條PCIe 主要干道。以目前開發(fā)主流的PCIe 5.0 為例,其傳輸速度可達(dá)32 GT/s,是PCIe 4.0的兩倍。由于在16個(gè)通道的配置中能夠傳輸128GB/s(每秒千兆字節(jié)),PCIe 5.0不僅可以提供高速、可靠的數(shù)據(jù)傳輸通道,同時(shí)還具備了靈活的擴(kuò)展性以滿足大量信息的處理需求,包括人工智能、機(jī)器學(xué)習(xí)和信息分析。

延伸閱讀:服務(wù)器市場洞察,最為產(chǎn)業(yè)期待的下一個(gè)十年

PCIe 5.0的核心優(yōu)勢

1.增強(qiáng)的速度和性能相較于PCIe 4.0,PCIe 5.0最顯著的優(yōu)勢是增強(qiáng)的速度和性能。2倍速度的提升將轉(zhuǎn)化為更快的數(shù)據(jù)傳輸率,減少延遲,并提高整體系統(tǒng)性能。

2.更加擴(kuò)大的帶寬PCIe 5.0具有更高的帶寬,可以實(shí)現(xiàn)更高的數(shù)據(jù)吞吐量。讓它成為需要實(shí)時(shí)處理大量數(shù)據(jù)的理想選擇,如:數(shù)據(jù)中心、高性能計(jì)算或電競游戲等。

3.向下兼容PCIe 5.0能夠向下兼容PCIe 4.0和PCIe 3.0,意味著它可以與既有接口的設(shè)備一起運(yùn)作。確保用戶可以升級他們的系統(tǒng),而不必更換所有的組件。

PCIe 5.0之PCB設(shè)計(jì)及挑戰(zhàn)

負(fù)責(zé)制定PCI Express的PCI-SIG組織(Peripheral Component Interconnect Special Interest Group),于2017年便啟動了PCIe 5.0規(guī)格制定的工作,并于2019年發(fā)布了該項(xiàng)標(biāo)準(zhǔn)。

PCIe 5.0的通道損耗設(shè)計(jì)在16GHz的頻率點(diǎn)應(yīng)小于36 dB,在顧及通道損耗規(guī)范及訊號質(zhì)量的同時(shí),PCB的成本管控也必須一并考慮,搭配合適的PCB材料與銅箔等級,可有效地降低開發(fā)成本,并在訊號完整性與成本之間取得平衡點(diǎn)。

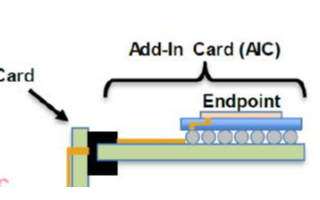

以典型只有一個(gè)連接通道的PCIe5為例,扣除掉前端CPU Chip約9 dB損耗、后端的PCIe標(biāo)準(zhǔn)卡(Add-in card)約9.5 dB損耗及保留10%設(shè)計(jì)余量約3.6 dB,其PCB板端能運(yùn)用的損耗值只剩約13.9 dB。一般服務(wù)器主板的PCIe走線長度約落在8inch(203.2mm)左右,若采用標(biāo)準(zhǔn)的PCB板材及銅箔,其PCB損耗約在18.5 dB,遠(yuǎn)遠(yuǎn)大于設(shè)計(jì)規(guī)范,因此需要搭配更高階的PCB板材及銅箔,成本也將增加,因此準(zhǔn)確的掌握高階PCB板材的損耗將有助于成本的優(yōu)化。

什么是PCB電性模擬?

PCB電性模擬是指透過軟件來模擬和分析印刷電路板(PCB)行為的過程。透過多種軟件可以模擬出電路板的電性表現(xiàn)結(jié)果,在進(jìn)入生產(chǎn)之前先找出潛在問題,進(jìn)一步解決問題、優(yōu)化設(shè)計(jì)。例如,模擬電路板對不同電壓、電流和頻率的反應(yīng)。通過模擬PCB的行為,工程師可以發(fā)現(xiàn)問題并改善電路板的性能及可靠度。

PCB材料損耗驗(yàn)證與檢測

PCIe 5.0電性損耗量測

綜觀整個(gè)業(yè)界,PCB電性損耗驗(yàn)證具有多種不同方式,過往的主流驗(yàn)證方法是采用SET2DIL (Single-Ended TDR to Differential insertion loss) 或SPP (Short Pulse Propagation)二者,但是這兩種方法,受到鉆孔(Via)和鉆孔殘斷(Via Stub)的寄生電容與電感的影響,在高頻時(shí)容易導(dǎo)致量測不準(zhǔn)確。于是Intel 開發(fā)了Delta-L分析手法,省去繁雜的校正步驟并扣除前述的寄生效應(yīng) (Parasitic Effect),并偕同治具供貨商開發(fā)專屬的探針頭,建立一套標(biāo)準(zhǔn)的PCB材料損耗 (Loss Per Inch) 量測手法。USI已建立此量測流程,此舉將有助于在高速傳輸接口設(shè)計(jì)領(lǐng)域中,確保產(chǎn)品質(zhì)量與最終產(chǎn)品的檢測。

USI環(huán)旭電子憑借在云端及存儲設(shè)備擁有多年的設(shè)計(jì)經(jīng)驗(yàn),PCB設(shè)計(jì)期間提供完整的設(shè)計(jì)服務(wù)及電性模擬服務(wù),利用3D電磁場模擬軟件進(jìn)行PCB阻抗優(yōu)化,可降低多重反射對訊號的影響,同時(shí)也運(yùn)用時(shí)域電路分析工具,有效解決干擾、衰減、串音等相關(guān)問題,確保終端的訊號可符合PCI-SIG的標(biāo)準(zhǔn)規(guī)范。

延伸閱讀:鎖定邊緣運(yùn)算領(lǐng)域,搶攻 AI 商機(jī)

PCB高速訊號設(shè)計(jì)檢查與模擬

由USI環(huán)旭電子自主開發(fā)的自動化設(shè)計(jì)模擬系統(tǒng)(Front-End Design Simulation) ,已成功應(yīng)用在各大芯片廠商(Intel、AMD、Qualcomm、MTK…等)的設(shè)計(jì)規(guī)范(Design Guideline), 主要用于確保電源設(shè)計(jì)的完整性。此外,也開發(fā)自動檢查PCB布線Design Rule,除了有效取代人工繁瑣的檢查及大大縮短開發(fā)時(shí)程之外,自動化檢查帶來快速且優(yōu)良的PCB布線質(zhì)量。例如:多數(shù)服務(wù)器的訊號線有2000~5000條,難以人眼確認(rèn)布線質(zhì)量,經(jīng)過自動化的檢查,更能加以確保并提升PCB布線質(zhì)量。

PCIe現(xiàn)在即是未來

PCIe的重點(diǎn)向來都聚焦在提高帶寬和數(shù)據(jù)傳輸速度。PCI-SIG 在2021的開發(fā)者大會正式發(fā)布PCI 6.0的規(guī)范,調(diào)變技術(shù)由NRZ (Non-Return-to-Zero) 改為PAM4 (Pulse Amplitude Modulation),傳輸速率可到達(dá)64GT/s。此外,PCIe 6.0還引入一些新功能,如PAM4編碼,它可以實(shí)現(xiàn)四級信令以提高數(shù)據(jù)傳輸速率,以及低延遲的前向糾錯(cuò)(FEC), 可以同步改善錯(cuò)誤檢測和糾正,以實(shí)現(xiàn)更快和更可靠的數(shù)據(jù)傳輸。來年(2022) 隨即著手制定PCIe 7.0 標(biāo)準(zhǔn),讓傳輸速率又再度翻倍至128GT/s的高性能。

另一個(gè)趨勢是PCIe在汽車和工業(yè)系統(tǒng)等新應(yīng)用中的使用越來越多。這些系統(tǒng)需要高速數(shù)據(jù)傳輸和實(shí)時(shí)處理,使PCIe成為其通信和控制系統(tǒng)的理想選擇。PCIe 5.0和PCB模擬技術(shù)的結(jié)合可以為下一代技術(shù)提供更高的性能和更快的數(shù)據(jù)處理速度。

設(shè)計(jì)師可以利用這些技術(shù)來減少設(shè)計(jì)缺陷,提高系統(tǒng)性能,并在更短的時(shí)間內(nèi)將新產(chǎn)品推向市場。雖說 PCIe 5.0要大規(guī)模投入到消費(fèi)市場還需要一段時(shí)間,但USI 會持續(xù)精進(jìn)高速接口相關(guān)技術(shù)的設(shè)計(jì)及優(yōu)化以提供高競爭力的產(chǎn)品來滿足客戶的需求。

FAQs1.PCIe 5.0和PCIe 4.0之間有什么區(qū)別?

與PCIe 4.0相比,PCIe 5.0提供2倍的傳輸速度以及更擴(kuò)大的帶寬。這使得PCIe 5.0更適合于處理海量數(shù)據(jù)和實(shí)時(shí)應(yīng)用。

2.PCB模擬技術(shù)能夠幫助什么?

利用PCB模擬技術(shù),你可以更好地了解設(shè)計(jì)中的潛在問題,并在實(shí)際生產(chǎn)前對其進(jìn)行優(yōu)化。這有助于提高系統(tǒng)性能,降低成本,并節(jié)省時(shí)間。

3.PCB損耗驗(yàn)證是必要的嗎?

是的,藉由測量PCB的電性損耗結(jié)果,可以評估信號在PCB線路中的衰減情況,確定是否需要采取進(jìn)一步的設(shè)計(jì)優(yōu)化措施,如改變PCB材料、線路布局或采用增強(qiáng)信號傳輸技術(shù)等。當(dāng)PCIe 5.0 傳輸速度達(dá)到了32 GT/s,損耗量測是重要且必要的步驟。

4.PCB模擬技術(shù)能否檢測出所有的設(shè)計(jì)缺陷?

PCB模擬技術(shù)可以檢測出大多數(shù)設(shè)計(jì)缺陷,但并不是萬無一失。重要的是,要結(jié)合使用模擬和物理測試,以確保你的設(shè)計(jì)在性能和可靠性方面得到優(yōu)化。

5.PCB高速訊號設(shè)計(jì)自動化檢查與模擬與過去差異為何?

一般服務(wù)器多數(shù)使用Intel or AMD平臺,訊號線有2000~5000條,難以人眼確認(rèn)布線品質(zhì)。因此,透過開發(fā)并導(dǎo)入自動化檢查,更能加以提升PCB的布線質(zhì)量。電源完整性模擬必須等PCB設(shè)計(jì)近乎完成才能開始執(zhí)行,而模擬設(shè)定皆需一定人工時(shí)間,因此導(dǎo)入電源完整性模擬自動化,即能在有限時(shí)間內(nèi),達(dá)到優(yōu)化電源設(shè)計(jì)進(jìn)而符合設(shè)計(jì)目標(biāo),確保各芯片組可以正常工作。

編輯:黃飛

-

pcb

+關(guān)注

關(guān)注

4326文章

23160瀏覽量

399951 -

模擬技術(shù)

+關(guān)注

關(guān)注

17文章

469瀏覽量

39824 -

PCIe

+關(guān)注

關(guān)注

15文章

1260瀏覽量

83191

原文標(biāo)題:【PCIe 5.0】深入PCB設(shè)計(jì)及驗(yàn)證 掌握高速傳輸核心

文章出處:【微信號:環(huán)旭電子 USI,微信公眾號:環(huán)旭電子 USI】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

PCIe 5.0設(shè)計(jì)面臨的挑戰(zhàn)以及仿真案例

[討論]PCB設(shè)計(jì)面臨的新挑戰(zhàn)

【漢普觀點(diǎn)】PCB設(shè)計(jì)面臨的挑戰(zhàn)

PCB設(shè)計(jì)之電容

高速PCB設(shè)計(jì)指南之七

PCB設(shè)計(jì)軟件(Sprint Layout) 5.0 漢化版

PCB設(shè)計(jì)實(shí)例之開關(guān)電源

什么是 PCIe 5.0? PCIe 5.0規(guī)范以及挑戰(zhàn)

PCB設(shè)計(jì)面臨的挑戰(zhàn)

什么是PCIe?PCIe有什么用途?PCIe 5.0有何不同?

PCIe 5.0之PCB設(shè)計(jì)及挑戰(zhàn)

PCIe 5.0之PCB設(shè)計(jì)及挑戰(zhàn)

評論