集成電路前道工藝及對應(yīng)設(shè)備主要分八大類,包括光刻(***)、刻蝕(刻蝕機(jī))、薄膜生長(PVD-物理氣相沉積、CVD-化學(xué)氣相沉積等薄膜設(shè)備)、擴(kuò)散(擴(kuò)散爐)、離子注入(離子注入機(jī))、平坦化(CMP設(shè)備)、金屬化(ECD設(shè)備)、濕法工藝(濕法工藝設(shè)備)等。

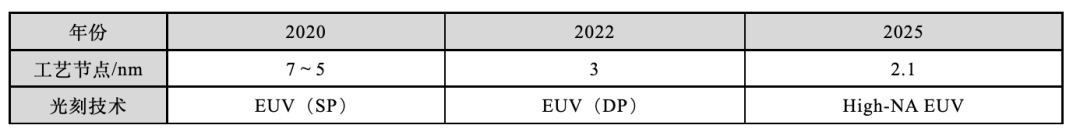

集成電路前道工藝及設(shè)備的標(biāo)志性指標(biāo)為集成電路的特征尺寸,主要沿摩爾定律方向持續(xù)延伸,根據(jù)國際器件與系統(tǒng)技術(shù)路線圖IRDS(2021),集成電路前道關(guān)鍵工藝、器件結(jié)構(gòu)對應(yīng)的設(shè)備加工技術(shù)能力將由當(dāng)前的5 nm、3 nm發(fā)展到2.1 nm、1.5 nm直至等效1 nm、0.7 nm技術(shù)節(jié)點(diǎn),如表1所示。

表1集成電路邏輯器件技術(shù)路線圖[1]

近期(2021-2025):FinFET晶體管結(jié)構(gòu)繼續(xù)延伸,由5 nm直至3 nm、2.1 nm節(jié)點(diǎn)。 為進(jìn)一步提升柵極控制能力,從3 nm節(jié)點(diǎn)開始, LGAA(Lateral gate-all-around,水平圍柵)結(jié)構(gòu)開始引入并逐漸替代FinFET結(jié)構(gòu),相應(yīng)的制造設(shè)備應(yīng)該隨之進(jìn)行技術(shù)迭代,支撐到這個(gè)制造節(jié)點(diǎn)的要求。

中期(2026-2030):晶體管全面進(jìn)入2.1 nm以下節(jié)點(diǎn),根據(jù)IRDS(2021)規(guī)劃,2.1 nm和1.5 nm這兩個(gè)工藝節(jié)點(diǎn)預(yù)計(jì)將分別在2025年和2028年出現(xiàn)。 LGAA晶體管結(jié)構(gòu)可以繼續(xù)支撐這兩個(gè)制造節(jié)點(diǎn)的要求,相關(guān)制造設(shè)備需要根據(jù)工藝特征尺寸縮小的要求做進(jìn)一步提升。

遠(yuǎn)期(2031-2035):晶體管進(jìn)入等效1 nm工藝節(jié)點(diǎn)和等效0.7 nm工藝節(jié)點(diǎn),晶體管的工藝特征尺寸達(dá)到極限,多層垂直堆疊的LGAA晶體管結(jié)構(gòu)將成為下一步發(fā)展方向。 單片三維堆疊工藝及設(shè)備技術(shù)將是這個(gè)階段的主要需求。

主要技術(shù)挑戰(zhàn)

(1)EUV光刻設(shè)備。 光刻技術(shù)直接決定了集成電路的特征尺寸(光刻線寬與***曝光波長成正比,與成像系統(tǒng)數(shù)值孔徑呈反比),是摩爾定律演進(jìn)的核心驅(qū)動力之一。 傳統(tǒng)的193 nm***在經(jīng)歷了“浸沒式技術(shù)”及“多重曝光”兩次重要技術(shù)升級后,已經(jīng)大規(guī)模應(yīng)用在10 nm節(jié)點(diǎn)集成電路制造中。 進(jìn)入7 nm以下節(jié)點(diǎn),雖然193 nm浸沒式光刻+多重曝光從技術(shù)上仍然可以滿足集成電路制造的需求,但工藝復(fù)雜度直線上升,造成了難以解決的良率和成本問題。 因此,采用13.5 nm極紫外光源的EUV***成為7nm及以下集成電路大生產(chǎn)首要選擇,在7 nm節(jié)點(diǎn),EUV光刻工藝步驟是193 nm浸沒式光刻的1/5,光刻次數(shù)是后者的1/3[4]。

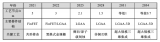

當(dāng)前EUV***已經(jīng)在產(chǎn)線批量應(yīng)用并支持7~5 nm節(jié)點(diǎn)的工藝制程要求。 隨著摩爾定律繼續(xù)延伸,EUV光刻主要是按照兩個(gè)方向演進(jìn):一是由單重曝光(Single Patterning, SP)發(fā)展至雙重曝光(Double Patterning,DP); 另一個(gè)就是提高EUV數(shù)值孔徑(High-NA EUV)。 根據(jù)IRDS光刻技術(shù)發(fā)展路線圖預(yù)測,在3 nm節(jié)點(diǎn)(2022年),集成電路大生產(chǎn)將采用雙重曝光EUV技術(shù); 在2.1 nm節(jié)點(diǎn)(2025年),集成電路大生產(chǎn)將采用高數(shù)值孔徑EUV技術(shù),如表2所示。

當(dāng)前ASML正在研發(fā)第二代EUV***,數(shù)值孔徑將由現(xiàn)在的0.33提升至0.5,同時(shí)不斷提升光源功率,預(yù)計(jì)量產(chǎn)時(shí)間為2024年,將支撐2025年之后集成電路制造的需求。

表2 光刻技術(shù)發(fā)展路線圖

(2)GAA(圍柵晶體管)制備設(shè)備。 GAA(Gate-All-Around)晶體管將是繼FinFET后的下一代晶體管結(jié)構(gòu)。 相對于FinFET的三面柵控結(jié)構(gòu),GAA晶體管溝道為水平或垂直納米線,柵極四面環(huán)繞溝道,柵控能力更強(qiáng),可以有效降低短溝道效應(yīng)[5]。 GAA結(jié)構(gòu)預(yù)計(jì)于2022年3 nm節(jié)點(diǎn)開始導(dǎo)入集成電路大生產(chǎn)線,并于2025年2.1 nm節(jié)點(diǎn)成為主流器件結(jié)構(gòu)。

GAA晶體管結(jié)構(gòu)的引入和特征尺寸的進(jìn)一步微縮,對集成電路制造工藝設(shè)備提出了更高的要求:離子注入機(jī)將更加強(qiáng)調(diào)共形摻雜(Comformal Doping)、薄膜和刻蝕工藝更加強(qiáng)調(diào)原子級的精度控制(ALD-原子層沉積、ALE-原子層刻蝕)、其他設(shè)備(如CMP、ECD、濕法工藝設(shè)備等)也需要做相應(yīng)調(diào)整,以滿足更高精度加工、非銅互聯(lián)材料、 新型HKMG材料等方面的需求。 下面就共形摻雜設(shè)備、原子層刻蝕設(shè)備、原子層沉積設(shè)備做詳細(xì)介紹。

共形摻雜的離子注入設(shè)備:晶體管采用三維結(jié)構(gòu)以后,對共形摻雜(各向同性的摻雜,各個(gè)方向上均勻摻雜)的要求不斷提升。 傳統(tǒng)的離子注入設(shè)備中,離子通過加速電場加速注入晶圓,摻雜的定向性強(qiáng),為滿足三維晶體管共形摻雜工藝的需求,離子注入設(shè)備有以下兩個(gè)發(fā)展方向:(1)進(jìn)一步提升離子注入機(jī)的束線角度、束線形狀和注入劑量的控制能力,如應(yīng)用材料公司的VIISta900 3D系統(tǒng); (2)采用等離子體浸沒式注入設(shè)備[6],在一層貼合晶圓表面結(jié)構(gòu)的等離子體輔助下,實(shí)現(xiàn)各個(gè)方向的均勻摻雜,如應(yīng)用材料公司的VIISta PLAD系統(tǒng)。

原子層沉積(Atomic layer deposition, 縮寫ALD)和原子層刻蝕(Atomic layer etching, 縮寫為ALE)[7]:進(jìn)入納米尺度以后,半導(dǎo)體制造對加工精度要求不斷提高。 以IMEC的堆疊納米線GAA晶體管結(jié)構(gòu)為例,制備過程為:在襯底上沉積多層SiGe/Si超晶格結(jié)構(gòu),完成Fin刻蝕后,通過選擇性刻蝕去除SiGe,釋放Si納米線,然后沉積高K介質(zhì)及金屬柵(置換式金屬柵工藝); 在此過程中,SiGe結(jié)構(gòu)刻蝕和納米線的釋放需要對實(shí)現(xiàn)對多層Si納米線之間SiGe的橫向精確去除,高K介質(zhì)及金屬柵的沉積需要在SiGe去除后的極小空間內(nèi)完成,以上工藝均需通過ALE和ALD設(shè)備實(shí)現(xiàn)。 ALE和ALD技術(shù)可以以一種自我限制且有序的方式在原子尺度逐層去除/沉積材料,賦予人們原子尺度的精細(xì)加工能力。

(3)設(shè)備智能化。 集成電路技術(shù)在賦能信息技術(shù)產(chǎn)業(yè)的同時(shí),新一代信息技術(shù)也在促進(jìn)集成電路產(chǎn)業(yè)的發(fā)展,推動其不斷邁向“智能制造”。 集成電路制造設(shè)備智能程度不斷提升,將逐漸具備晶圓狀態(tài)追溯、先進(jìn)工藝控制(缺陷監(jiān)測、工藝過程控制)、設(shè)備能耗管理、預(yù)測性排產(chǎn)、預(yù)測性維護(hù)和虛擬量測等功能。

要實(shí)現(xiàn)這些,除設(shè)備需要具有相應(yīng)的信息采集及決策執(zhí)行功能外,還需要產(chǎn)線信息系統(tǒng)的配合,單純從設(shè)備的角度,根據(jù)IRDS預(yù)測,設(shè)備將按照表3所示的技術(shù)路線圖發(fā)展,逐步支持智能化功能的實(shí)現(xiàn)。

表3 設(shè)備智能化技術(shù)路線圖[1]

(4)450 mm(18英寸)設(shè)備。 在一次工藝過程中,更大的晶圓尺寸可以生產(chǎn)更多的芯片,可以顯著降低單顆芯片成本。 晶圓尺寸不斷增大是集成電路產(chǎn)業(yè)一直以來的發(fā)展趨勢之一,由最初的100 mm (4英寸)、150 mm(6英寸),一直發(fā)展到今天的300 mm(12英寸,2001年引入,最早用于0.13 μm產(chǎn)線)。

2008年起,450 mm(18英寸)晶圓及其制造設(shè)備的生產(chǎn)被提上日程,初定于2012年組建18英寸試驗(yàn)產(chǎn)線,2015年開始大生產(chǎn)線替代。 目前450 mm (18英寸)大硅片及450 mm(18英寸) 設(shè)備接口標(biāo)準(zhǔn)早已完成,但是由于450 mm(18英寸)設(shè)備研發(fā)及晶圓廠建線耗資巨大,450 mm(18英寸)晶圓設(shè)備的應(yīng)用時(shí)間一再拖期。 根據(jù)最新的IRDS技術(shù)路線圖,450 mm(18英寸)設(shè)備的大生產(chǎn)線替代時(shí)間已經(jīng)延后到了2025年之后。

審核編輯:湯梓紅

-

集成電路

+關(guān)注

關(guān)注

5392文章

11622瀏覽量

363175 -

半導(dǎo)體

+關(guān)注

關(guān)注

334文章

27703瀏覽量

222627 -

工藝

+關(guān)注

關(guān)注

4文章

603瀏覽量

28892 -

光刻機(jī)

+關(guān)注

關(guān)注

31文章

1157瀏覽量

47579 -

刻蝕機(jī)

+關(guān)注

關(guān)注

0文章

52瀏覽量

4257

原文標(biāo)題:半導(dǎo)體工藝裝備現(xiàn)狀及發(fā)展趨勢(上)

文章出處:【微信號:閃德半導(dǎo)體,微信公眾號:閃德半導(dǎo)體】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

半導(dǎo)體工藝與制造裝備技術(shù)發(fā)展趨勢

半導(dǎo)體工藝技術(shù)的發(fā)展趨勢

新興的半導(dǎo)體技術(shù)發(fā)展趨勢

5G創(chuàng)新,半導(dǎo)體在未來的發(fā)展趨勢將會如何?

廣播電視發(fā)展現(xiàn)狀及趨勢

云計(jì)算產(chǎn)業(yè)發(fā)展現(xiàn)狀及趨勢

恒興隆機(jī)電:深圳電主軸行業(yè)市場現(xiàn)狀及發(fā)展趨勢是什么?

國外半導(dǎo)體設(shè)備現(xiàn)狀與發(fā)展趨勢

高清視頻監(jiān)控技術(shù)的現(xiàn)狀及發(fā)展趨勢

張波教授論述功率半導(dǎo)體的現(xiàn)狀及發(fā)展趨勢

半導(dǎo)體工藝裝備現(xiàn)狀及發(fā)展趨勢

半導(dǎo)體工藝裝備現(xiàn)狀及發(fā)展趨勢

半導(dǎo)體工藝裝備現(xiàn)狀及發(fā)展趨勢

評論