要降低DC到DC電路的輻射發(fā)射,可以采取以下幾種方法:

地線和電源線的布局:確保地線和電源線的布局合理,并盡量減少它們之間的距離。使用短而粗的地線和電源線,以減小回路面積和環(huán)路面積,從而降低輻射發(fā)射。

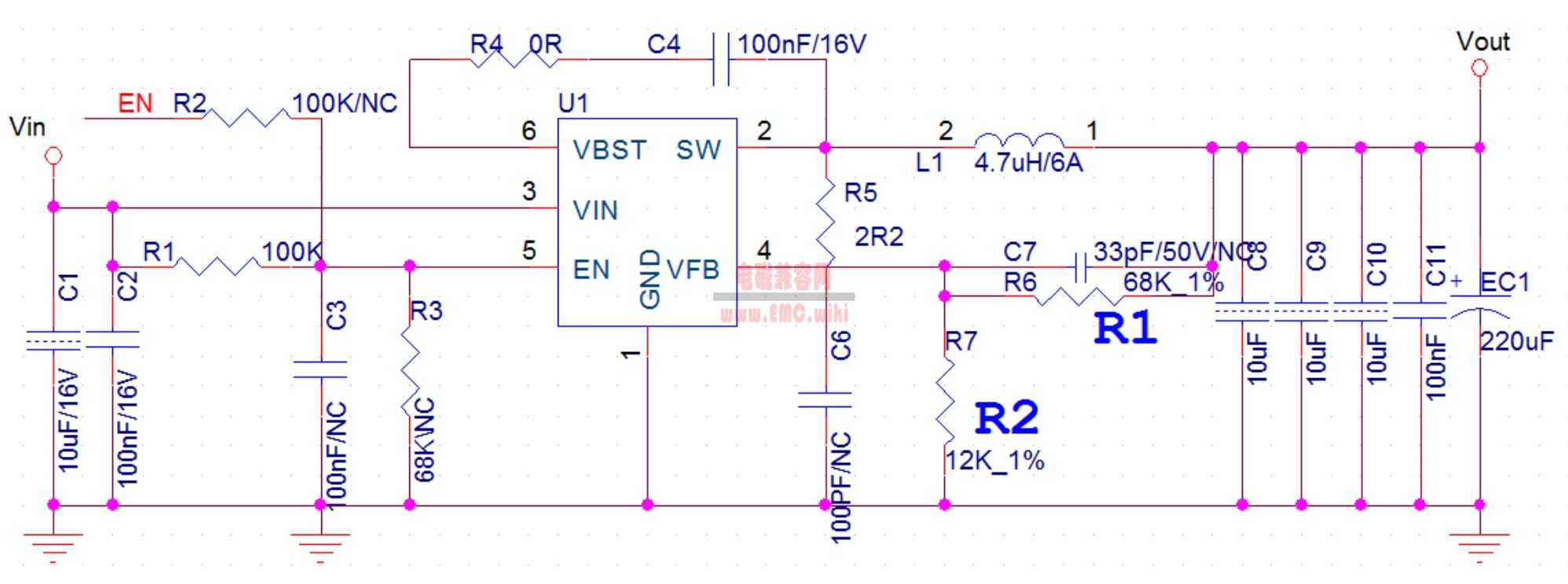

濾波器的使用:在DC到DC電路的輸入和輸出端之間添加合適的濾波器,如電感、電容器和濾波器網(wǎng)絡(luò)。這些濾波器可以降低電路中的高頻噪聲,并減少輻射發(fā)射。

地面平面和屏蔽:在電路板上創(chuàng)建良好的地面平面,盡量減少回路面積。可以使用屏蔽罩或金屬殼體來包圍電路,以減少輻射發(fā)射和抑制外部電磁干擾。

優(yōu)化布線:優(yōu)化電路的布線,盡量減少導線長度和面積。使用短而直接的導線,減小回路面積和環(huán)路面積,從而減少輻射發(fā)射。

使用抑制器件:在電路中使用抑制器件,如電源線抑制器、磁珠、濾波電感器等。這些器件可以幫助抑制高頻噪聲和輻射發(fā)射。

良好的接地設(shè)計:確保電路板的良好接地,減少接地回路的電阻和電感。使用地面平面和短而直接的接地導線,以提供低阻抗接地路徑。

選擇低輻射發(fā)射元件:在設(shè)計電路時選擇低輻射發(fā)射的元件,例如低噪聲開關(guān)電源和低輻射發(fā)射的電容器。

綜合應用上述方法可以有效地降低DC到DC電路的輻射發(fā)射。然而,確保設(shè)計和布局符合相關(guān)的電磁兼容性(EMC)標準也是非常重要的,這樣可以保證電路在實際應用中能夠滿足輻射發(fā)射的限制。建議在設(shè)計中咨詢專業(yè)的電磁兼容性工程師,以獲得更具體的指導和建議。

審核編輯:湯梓紅

-

電路板

+關(guān)注

關(guān)注

140文章

4996瀏覽量

98854 -

輻射發(fā)射

+關(guān)注

關(guān)注

0文章

42瀏覽量

11763 -

DC電路

+關(guān)注

關(guān)注

0文章

6瀏覽量

5968

發(fā)布評論請先 登錄

相關(guān)推薦

用電源變換器工作頻率的抖動降低峰值輻射

LDO和DC/DC,那個更強?

低EMI DC / DC轉(zhuǎn)換器的PCB設(shè)計

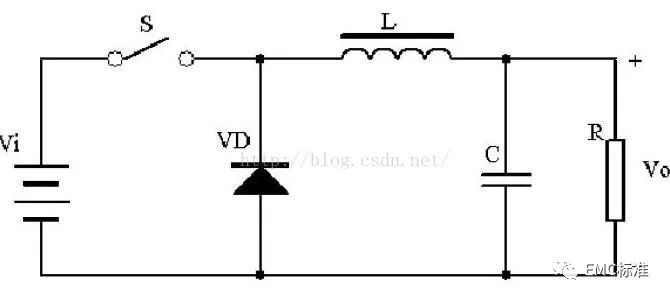

降低dc-dc變換器輸出電壓紋波的電路

輻射發(fā)射對EMI的影響

如果降低USB通信的輻射發(fā)射?

VDMOS器件損傷的DC/DC轉(zhuǎn)換器輻射預兆單元設(shè)計

DC-DC降壓轉(zhuǎn)換器電路布局與設(shè)計和實踐

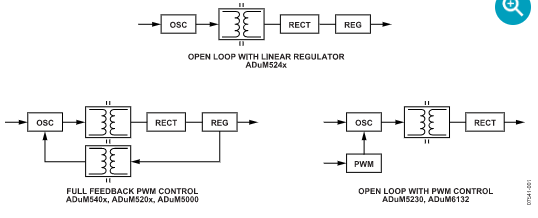

使用iso功率器件控制輻射發(fā)射的建議

最大限度地減少密集PCB布局中多個iso功率器件的輻射發(fā)射

如何降低DC到DC電路的輻射發(fā)射?

如何降低DC到DC電路的輻射發(fā)射?

評論