本文討論從GSM到OC-192及更高版本的高速串行通信的時鐘數據恢復(CRD)。它解釋了如何通過典型鏈接轉換和重新捕獲數據。本文還研究了不同的CDR方案以及參考振蕩器在通信鏈路發射端和接收端的作用。

時鐘數據恢復 (CDR) 在電信、光收發器、數據和存儲區域網絡以及無線產品中的應用比比皆是。隨著設計需要更大的帶寬,以及分配和頻譜帶寬使用量的增加,CDR技術的優勢變得越來越重要。此外,供應商及其產品正在從并行接口遷移到串行接口,用于系統和板級接口。

近年來,CDR技術的使用越來越多,因為需要處理背板上更寬的并行總線寬度,同時管理接收器的時鐘和數據偏斜。此外,路由這些信號可能很困難,因為它們會消耗電路板空間和功耗,并且需要多層布線方案來管理信號和線路端接。使用高位寬數據總線產生的EMI也是一個問題。

由于新通信技術的出現、電信號處理的改進以及需要通過 FR-4 和背板、光學和無線介質發送多千兆位電信號,CDR 非常重要。在傳輸之前將時鐘和數據結合起來的通信技術并不新鮮。時鐘和數據的組合確保時鐘和數據信號始終同時到達。然而,訣竅是接收器上的時鐘和數據分離。這是通過CDR電路實現的。從并行到串行格式獲取數據的產品(反之亦然)稱為串行器/解串器(或簡稱“SerDes”)。這些產品通常具有CDR模塊來反序列化串行數據流。

本文探討了在高速串行通信鏈路應用中成功實現CDR所需的CDR組件。概述了典型的高速串行通信鏈路,介紹了如何通過鏈路轉換和重新捕獲數據。針對一般 CDR 拓撲討論了不同的 CDR 方案。此外,還特別注意參考振蕩器在鏈路發射側和接收端的作用。

高速串行通信中的時鐘和數據恢復

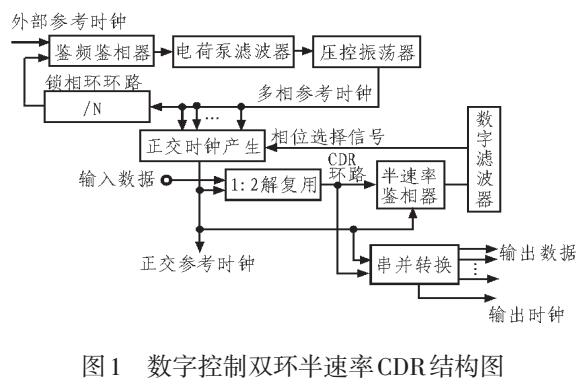

圖1提供了高速串行通信鏈路的基本示意圖。并行數據(位 b1, b2, b3,...bn) 以頻率 f 到達傳輸串行器t.在序列化程序中,數據從并行格式轉換為串行格式。開發串行比特流的最小比特率等于 n x ft,其中 n 是并行數據位的總數。由此產生的頻率(比特率)可以高于ft取決于數據是編碼為滿足誤碼率 (BER) 性能的通道要求,還是在接收端 CDR 提供豐富的轉換內容。 Reed-Solomon前向糾錯(FEC)和8B10B編碼分別是信道編碼或在接收CDR處創建豐富轉換內容的每個示例。 然后,該串行數據準備好傳輸到通道并發送到接收器, 終于到達反序列化器。此基本通信模塊適用于通過光纖、空氣或背板傳輸的數據。

圖1.時鐘和數據恢復是高速串行通信鏈路的基礎。

定時(時鐘)在CDR應用中至關重要。在系統設計過程中,設計人員確定如何將數據從并行格式驅動為串行格式,以便通過通道進行傳輸和接收,同時等待傳輸信號的通道失真。將設計劣化對數據信號的影響降至最低對于保護信噪比和保持誤碼率性能非常重要。例如,在跨背板的數字傳輸方案中,系統的抖動性能非常重要,因為高速電信號會穿越各種長度(FR-4和背板),從而導致信號電平和時變失真方面的信號衰減。

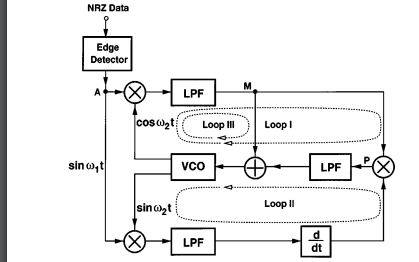

時鐘數據恢復的核心是基于鎖相環(PLL)的電路,在某些情況下可以基于數字。圖2是基本PLL框圖,可用于通信鏈路的串行器或傳輸端,如圖1所示。PLL模塊包括一個鑒頻檢波器(PD)、濾波器(LPF)、壓控振蕩器(VCO)和一個分頻鏈(1/n)。分頻鏈用于為PD提供相當的頻率輸入。通過這種方式,VCO的輸出與非常穩定的基準輸入V相位對齊裁判.該PLL模塊的目的是將參考頻率乘以固定量(n),即VCO的固有頻率。在大多數情況下,V裁判將基于石英,提供高度的穩定性和準確性以及出色的相位噪聲特性。此外,該基準電壓源可以進行溫度補償或電壓補償,具體取決于所需的應用或系統要求。在基于 SONET 的應用程序中,此引用可能滿足特定的層級別(即層級別 3、3E 或 4)。

圖2.時鐘乘法應用由PLL驅動。

在接收端,CDR PLL模塊的外觀略有不同,以滿足檢索時鐘和數據的需求。如圖3所示,組合的時鐘/數據信號通過緩沖器進入PLL模塊,該緩沖器饋送兩條不同的路徑。一條路徑饋送數據決策 (DEC) 模塊,而第二條路徑饋送時鐘恢復模塊。時鐘恢復模塊看起來非常類似于圖2的PLL模塊減去1/n模塊。從VCO恢復的時鐘用作DEC的采樣輸入、相位頻率檢波器的反饋,以及下游的系統時序要求。在圖1中,該恢復時鐘被分頻為并行時鐘頻率,以驅動解串器模塊。

圖3.對基本PLL模塊的修改用于實現CDR電路。

時鐘/數據恢復中的參考振蕩器

圖中所示的參考振蕩器說明了應用于振蕩器輸入的VCO。該電壓控制由LPF級建立。通常,VCO或壓控晶體振蕩器(VCXO)可用作環路振蕩器,如圖3所示。環路振蕩器的主要作用是跟蹤輸入時鐘/數據的頻率偏差。此外,它還將此時鐘提供給 CDR(解串器)下游的其他組件。這是通過LPF的輸出實現的,LPF驅動VCO或VCXO的電壓控制輸入。

在電信、無線和數據通信的CDR應用中,輸入的數據信號加時鐘應具有相對穩定的頻率特性。這假設傳輸時鐘滿足一定的精度和穩定性規格。在接收側,設計排除了最小和最大精度/穩定性。如果發射時鐘頻率預計為規定頻率的±50ppm,則接收時鐘將具有最小±50ppm的頻率調整能力。但是,出于設計目的,請考慮略大于±50ppm的頻率調整能力。這種擴展的頻率調整功能可適應信道的任何額外信號頻率失真或通信中斷。

盡管PLL試圖驅動到靜態狀態,這意味著頻率鎖定已經建立,但在某些情況下,電壓控制輸入可能會以高于預期的速率移動。LPF 帶寬決定了 PLL 可以保持鎖定的最大速率。最終,接收VCO(或VCXO)的作用是跟蹤和再現恢復的時鐘。

在CDR中沒有數據/時鐘輸入的情況下,CDR需要在指定的時間內為任何下游通信要求(即解串器)提供參考信號。

在某些應用中,將使用VCO/VCXO組合。在圖 4 中,VCO/VCXO 至少為通用 CDR 配置帶來了兩個好處。首先,增加VCXO可以快速調節VCO頻率,使其與預期的時鐘/數據信號相匹配。選擇VCXO頻率以匹配預期的時鐘頻率范圍。例如,寬帶VCO可能需要數千個樣本才能鎖定到傳入數據流。VCXO和鎖檢測電路的添加可確保VCO保持一定的工作頻率,并有助于在啟動條件下提供更可預測的鎖定時間。其次,如果時鐘/數據輸入長時間丟失,則添加VCXO很有幫助。在沒有時鐘/數據信號的情況下,系統將參考非常穩定的基于石英的振蕩器(V裁判) 提供保持,直到時鐘/數據信號從信號丟失 (LOS) 中恢復。保持是一種規范,適用于參考時鐘在特定時間段內保持一定精度的能力(例如,4 小時內保持 ±6.24ppm)。

圖4.對基本 CDR 塊的修改可輕松鎖定傳入時鐘/數據流。

結論

各種解決方案適用于時鐘/數據恢復和重定時、串行器和解串器、時鐘發生器和通信應用的TCXO。這些器件允許設計人員開發頻率范圍為 10MHz 至 10GHz 的電路,并支持從 GSM 到 OC-192 及以上的應用。隨著設計對更大帶寬的要求越來越高,CDR 技術是電信、光收發器、數據和存儲區域網絡以及無線應用的理想選擇。

審核編輯:郭婷

-

收發器

+關注

關注

10文章

3454瀏覽量

106243 -

振蕩器

+關注

關注

28文章

3847瀏覽量

139360 -

接收器

+關注

關注

14文章

2479瀏覽量

72213

發布評論請先 登錄

相關推薦

如何利用Altera FPGA中的鎖相環及Logiclock實現高速時鐘恢復電路?

HFTA-07.0:精密參考時鐘使用的時鐘和數據恢復電路-H

基于高速CMOS時鐘的數據恢復電路設計與仿真

時鐘恢復電路的設計資料詳細說明

HFTA-07.0:時鐘和數據恢復電路中的精密參考時鐘應用

HFTA-07.0:時鐘和數據恢復電路中的精密參考時鐘應用

評論