引言

為了提供更優良的靜電完整性,三維(3D)設計(如全圍柵(GAA)場電子晶體管(FET ))預計將在互補金屬氧化物半導體技術中被采用。3D MOS架構為蝕刻應用帶來了一系列挑戰。雖然平面設備更多地依賴于各向異性蝕刻,但是3D設備在不同材料之間具有高選擇性,需要更多的各向異性蝕刻能力。

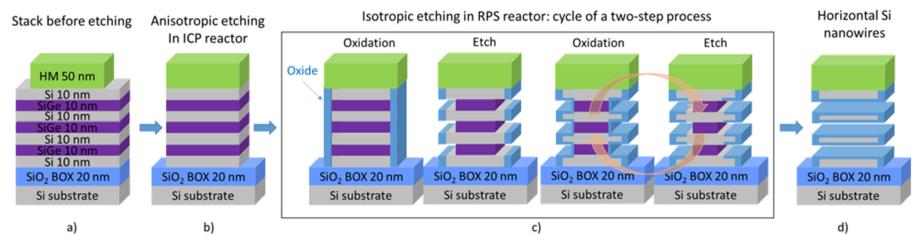

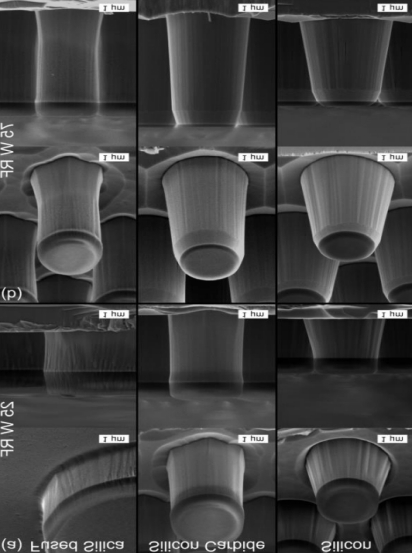

圖1描述了一種制造GAA器件水平堆疊納米線的典型方法。它使用了在絕緣體(SOI)襯底上的硅,并通過外延生長產生一堆Si/SiGe超晶格。這個工藝可能需要通過Si選擇性或SiGe選擇性各向同性蝕刻能力,來分別設計隔離的SiGe或Si納米線。本文更具體地研究了SiGe的選擇性和各向同性蝕刻用以制造Si納米線。

圖1:GAA器件用堆疊硅納米線的制備方法

實驗與討論

疊層的各向異性構圖由幾個等離子體步驟組成:首先使用CF4等離子體工藝打開SiO2 HM,然后使用O2等離子體去除剩余的抗蝕劑,最后,使用HBr/Cl2/He-O2等離子體工藝對各向異性蝕刻Si/SiGe進行多層疊層。在此步驟之后,SiGe層可用于在RPS反應器中進行的各向同性蝕刻。

暴露于NH3/ NF3/O2 RP的Si和SiGe膜的蝕刻動力學表明,在膜被蝕刻之前有一段時間的流逝(圖1)。該延遲對應于遠程等離子體反應的中性粒子吸附在表面,然后與底物發生反應。

硅上的孵化時間(22秒)比硅鍺上的孵化時間(4秒)要長,一旦該延遲過去,SiGe蝕刻速率是138 nm/min的常數。關于硅膜,觀察到約60秒的瞬時蝕刻狀態,在此期間,以約13.3納米/分鐘蝕刻硅,然后在穩定狀態下,硅蝕刻速率減慢至3.9納米/分鐘。

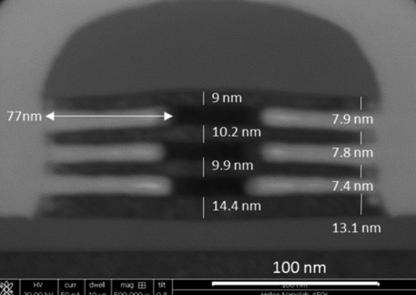

通過四個循環的氧化/蝕刻步驟,經過RP選擇性和各向同性過程后的圖案化Si/SiGe異質結構的掃描透射電子顯微鏡(STEM)圖像顯示了實現高選擇性蝕刻的潛力(圖2)。

圖2:異質結構STEM圖像

結論

英思特提出了使用RPS工藝來實現選擇性蝕刻的新路線。它包括循環表面處理步驟和蝕刻步驟的兩步工藝。這個概念是受到原子層沉積(ALD)領域中已經進行的選擇性沉積的啟發。ALD目前的趨勢是將分子直接化學鍵合到表面,以抑制反應位點,然后阻止ALD前體分子之間的進一步反應。通過選擇性地使存在的材料表面功能化,從而可以獲得選擇性沉積。

江蘇英思特半導體科技有限公司主要從事濕法制程設備,晶圓清潔設備,RCA清洗機,KOH腐殖清洗機等設備的設計、生產和維護。

審核編輯黃宇

-

半導體

+關注

關注

334文章

27703瀏覽量

222621 -

等離子

+關注

關注

2文章

236瀏覽量

30004 -

FET

+關注

關注

3文章

637瀏覽量

63132 -

蝕刻

+關注

關注

9文章

419瀏覽量

15508 -

GAA

+關注

關注

2文章

37瀏覽量

7484

發布評論請先 登錄

相關推薦

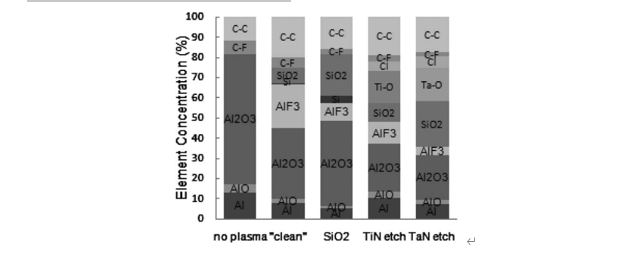

金屬蝕刻殘留物對對等離子體成分和均勻性的影響

等離子體蝕刻和沉積問題的解決方案

PCB多層板等離子體處理技術

PCB電路板等離子體切割機蝕孔工藝技術

PCB板制作工藝中的等離子體加工技術

微波標量反射計可測量大范圍的等離子體密度

低溫等離子體廢氣處理系統

TDK|低溫等離子體技術的應用

等離子體應用

低溫等離子體技術的應用

載體晶圓對蝕刻速率、選擇性、形貌的影響

真空等離子清洗機的制造商正在引入氧和氫等離子體來蝕刻石墨烯

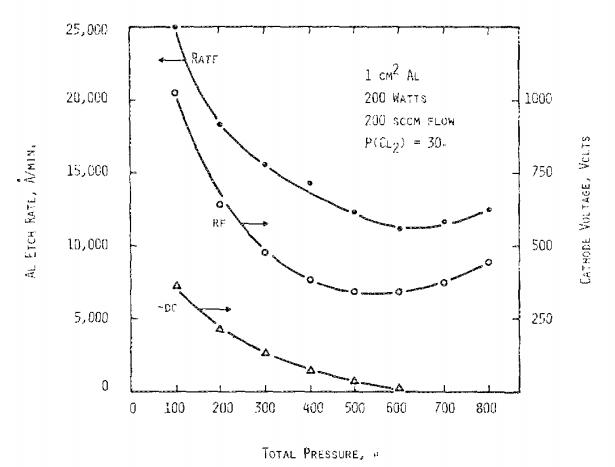

鋁等離子體蝕刻率的限制

遠程等離子體選擇性蝕刻的新途徑

遠程等離子體選擇性蝕刻的新途徑

評論