電荷耦合器件(CCD)是大多數消費類成像系統的首選圖像傳感器。CCD的輸出信號需要一個獨特的、主要是模擬的信號處理鏈。起初,處理是用標準的線性元件實現的:運算放大器、A/D和D/A轉換器、模擬乘法器和模擬開關。隨著時間的流逝,半導體設計和技術的進步使得將它們結合到更完全集成的CCD信號處理方法中成為可能。如今,從CCD的輸出到A/D轉換器的數字輸出,所需的所有信號處理步驟都可以通過單個集成電路完成。ADI公司的CCD成像應用集成解決方案保留了傳統設計的性能,但可大幅節省成本、功耗和尺寸。

處理CCD信號

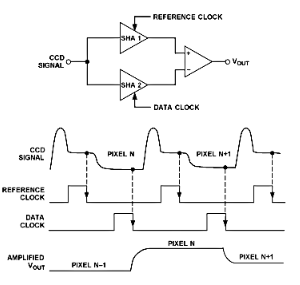

要了解集成信號處理組件必須提供的功能,請考慮圖1所示的典型CCD輸出波形。CCD的輸出級通過檢測電容CS將每個像素(圖像元件)的電荷轉換為電壓。在每個像素周期開始時,CS上的電壓被復位到參考電平,從而導致復位饋通毛刺。每個像素感測的光量由參考電壓電平和數據電壓電平之間的差異來測量。精確恢復和數字化CCD信號需要多種操作,包括相關的雙采樣和直流恢復(箝位)、增益、偏移和A/D轉換。

圖1.CCD輸出級。

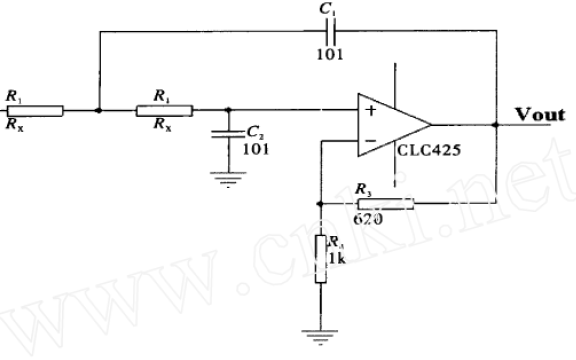

相關雙采樣(CDS)有兩個重要用途:它計算CCD信號的參考電平和數據電平之間的差異,并減少CCD信號中的一些噪聲成分。從概念上講,CDS是一種差分時間放大器:它對輸入信號進行單獨的采樣,并輸出它們之間的差值。圖2顯示了使用兩個采樣保持放大器(SHA)和一個差動放大器(許多可能的拓撲之一)的CDS的簡單實現。

圖2.相關雙重采樣。SHA1 對參考電平進行采樣,對數據電平進行采樣,SHA2 對數據電平進行采樣。差動放大器減去采樣,以測量光強度,從而降低共模噪聲。

通過取CCD信號的兩個樣本并減去它們,將與兩個樣本相關的任何噪聲源都將被移除。不相關的緩慢變化的噪聲源的幅度將減小。圖1所示CCD輸出級引入的噪聲主要包括來自電荷檢測節點的kT/C噪聲,以及來自輸出放大器的1/f和白噪聲。來自復位開關導通電阻的kT/C噪聲在Sense節點上采樣,并一直保持到下一個像素。它將在參考和數據級別期間存在,因此它在一個像素周期內相關,并由 CDS 刪除。CDS還將衰減來自輸出放大器的1/f噪聲,因為CDS的頻率響應會隨著頻率的降低而下降。CDS之前從電源和溫度漂移引入的低頻噪聲也會被CDS衰減。但CDS不會降低CCD引入的寬帶噪聲。

典型的 CCD 信號具有 3 到 9 伏或更高的直流偏移。這種幅度的直流偏移通常與CMOS信號處理IC不兼容,因為大多數掃描儀和高端相機系統使用5 V電源作為信號處理器,而攝錄一體機和數碼相機使用低至2.7伏的電源。使用輸入“直流恢復”箝位的片內交流耦合通過增加一個外部耦合電容即可實現必要的直流電平轉換。

CCD的暗電流導致CCD信號的參考電平和數據電平之間的差異,通常范圍為10至80 mV。如果不加以校正,該失調將減小系統動態范圍,特別是在施加增益后。模擬信號處理校正失調的平均值,保持動態范圍。由于模擬域中大部分失調被移除,數字圖像處理電路可以在像素到像素的基礎上執行精細的失調調整,以校正暗電流變化。

需要可編程增益放大器(PGA)來使CCD信號的最大幅度與A/D轉換器的滿量程電壓相匹配。用于掃描儀和數碼相機應用的不同 CCD 的峰值跨度范圍為 100 mV 至 3 或 4 V。大多數 CMOS A/D 轉換器的滿量程電壓范圍為 1 至 5 V。如果CCD信號僅跨越ADC滿量程范圍的25%,則將損失2位動態范圍。PGA將CCD信號放大到適當的幅度,從而允許使用ADC的全動態范圍。

A/D轉換器將調理后的模擬信號轉換為數字表示,然后由外部應用專用數字電路處理。A/D 轉換器所需的速度和分辨率基于應用程序的像素速率和分辨率。最大動態范圍為55-60 dB的CCD需要10位ADC,而動態范圍為65-70 dB的CCD則需要12位ADC。可能需要額外的分辨率,以便為數字圖像處理留出余量。例如,數字升頻6 dB會使ADC的動態范圍降低一位,因為只能使用模數轉換器輸入電壓范圍的一半。

ADI集成解決方案

ADI公司為掃描儀、數碼相機和攝像機市場提供多種模擬前端(AFE)集成電路;它們包括上述所有信號處理步驟。工藝技術和電路拓撲結構的進步使得這種集成水平可以在不犧牲性能的情況下在代工廠CMOS中實現。不久前,還需要更昂貴、更耗電的BiCMOS或雙極技術。通過將成功的ADC架構與高性能CMOS模擬電路相結合,可以設計出完整的低成本CCD信號處理IC。

|

部件號 |

AD9807 |

AD9816 |

AD9805 |

AD9803 |

AD9802 |

AD9801 |

|

通道數 |

3 | 3 | 3 | 1 | 1 | 1 |

|

分辨率,位 |

12 | 12 | 10 | 10 | 10 | 10 |

|

采樣率,兆赫 |

6 | 6 | 6 | 21 | 18 | 18 |

|

微分非線性,LSB |

最大 0.75 |

最大 1.0 |

最大 0.5 |

0.5 類型 |

0.5 類型 |

0.5 類型 |

|

無失碼 |

保證 |

保證 |

保證 |

保證 |

保證 |

保證 |

|

輸出噪聲,有效值 (LSB) |

0.3 | 0.5 | 0.1 | 0.85 | 0.85 | 0.85 |

|

內部電壓基準 |

是的 |

是的 |

是的 |

是的 |

是的 |

是的 |

|

電源電壓,V |

+5 | +5 | +5 | +3 | +3 | +3 |

|

價格,美元(1000 秒) |

$25 |

$9.50 |

$9.50 |

** |

$5.95 |

$8.50 |

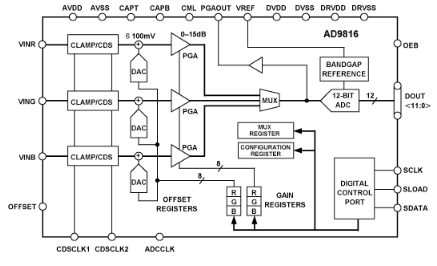

對于掃描器應用,AD9807和AD9805(見表)于1996年底推出。這些器件具有三個用于處理彩色線性 CCD 的輸入通道,具有輸入鉗位、CDS、失調控制、PGA 和一個 12 位或 10 位 ADC。附加的操作模式允許與接觸式圖像傳感器(CIS)直接連接,這是另一種越來越受歡迎的圖像傳感器。該系列的最新產品是AD9816(圖3)。這款第二代產品的功能與AD9807類似,但封裝更小,成本更低。

圖3.AD9816具有3通道同步采樣、單獨的每通道增益和失調調整、內部基準電壓源和6 MHz、12位模數轉換器。板載寄存器使用3線串行接口進行編程。

對于數碼相機(DSC)設計,AD9801于1997年初推出。雖然它具有與AD9807系列相同的基本功能,但它專為面陣CCD陣列而定制。采用單通道18 MHz架構,具有30 dB可編程增益放大器、黑電平箝位環路和10位ADC。輸入范圍更小,以適應區域CCD的較低輸出電壓,可編程增益范圍更寬,以便與使用相機的寬范圍照明條件兼容(掃描儀在更均勻的照明條件下工作)。電池供電所需的功耗較低,因此AD9801采用3 V單電源供電。

AD9802于1997年秋季推出,旨在同時用于DSC和便攜式攝像機設計。如圖4所示,AD9802具有AD9801的特性,還包括一個至10位ADC的多路復用直接輸入。便攜式攝像機應用需要直接ADC輸入,以數字化來自磁帶或外部VCR的模擬視頻信號。目前正在對AD9803進行采樣(在撰寫本文時),增加了一個串行數字接口,用于對內部寄存器進行編程,并具有更高的采樣速率。

圖4.AD9802 CCD信號處理器的功能框圖

性能注意事項

成像應用中特別關注的兩個重要特性是噪聲和非線性。

AFE中的噪聲包括來自所有模擬電路的寬帶噪聲、來自ADC的寬帶噪聲和來自ADC的量化噪聲。獨立的模數轉換器通常指定信噪比(SNR)或信噪失真(SINAD),但這些類型的測量在成像應用中并不完全有用。轉換器SINAD使用正弦波輸入進行測試,包括模擬信號失真、積分和差分非線性(INL和DNL)引起的轉換器失真、量化噪聲和熱噪聲的影響。在某些情況下,為了減少熱噪聲的貢獻,需要平均多個數據記錄。

失真數字在成像應用中并不重要,因為CCD信號本質上不是正弦的,并且ADC的前端僅在波形相對緩慢移動的部分對CCD信號進行采樣。CCD 系統設計人員沒有使用傳統的轉換器 SNR 測量,而是考慮了寬帶噪聲、量化噪聲和 DNL 誤差的影響。寬帶噪聲可以使用“接地輸入直方圖”測試進行測量,在該測試中,器件的輸入接地,并獲取輸出數據的直方圖。直方圖的標準偏差將給出器件的均方根噪聲電平(不包括ADC量化噪聲)。低噪聲AFE的熱噪聲水平可以與其板載ADC的均方根量化噪聲相當或更低。

AFE噪聲很重要,因為它會影響系統的動態范圍。動態范圍是通過比較系統中可以處理的最大信號和可以解析的最小信號電平來確定的。來自CCD和AFE(包括模擬信號處理和A/D轉換器)的噪聲會影響整個系統的噪聲水平。CCD隨機噪聲通常由CCD制造商指定為mV或電子均方根的“本底噪聲”或“隨機噪聲”;CDS將降低kT/C和1/f噪聲貢獻。由于每個像素的暗電流變化引起的固定圖案噪聲在圖像中可能非常令人反感,如果不通過校準技術降低,則應將其包含在噪聲計算中。用于緩沖CCD輸出信號的放大器也會引入噪聲,盡管可以通過放大器選擇和電路技術將其降至最低。AFE的噪聲貢獻可以在產品的數據手冊中找到,也可以使用接地輸入直方圖測試進行測量。ADC的分辨率將決定量化噪聲電平,量化噪聲電平是通過將12LSB的權重除以<>的平方根來計算的。將給定帶寬(稱為信號鏈中的同一點)中的所有噪聲源相加,得出:

該公式可用于近似可實現的動態范圍,以查看所考慮的AFE是否與CCD匹配良好。如果最大的噪聲源是下一個最大噪聲源的三倍,它將占主導地位。了解哪些噪聲源占主導地位將有助于選擇合適的AFE。

AFE的線性度也會影響系統性能。實際ADC的非線性會導致數字化圖像中的偽影。微分非線性(DNL)非常重要,因為人類視覺系統擅長檢測圖像中的邊緣或不連續性。DNL是ADC代碼寬度的變化,不良的DNL會導致相鄰亮度水平的漸變或“階躍”。真正的 10 位系統要求 DNL 在 1 位級別優于 10 LSB(最好是 0.5 LSB),以避免圖像質量下降。DNL 差到足以導致丟失代碼可能會導致數字處理中的圖像偽影。積分非線性(INL)也很重要,但給定量比相當量的DNL更難察覺。人類視覺系統不太擅長區分分布在整個灰度范圍內的漸進非線性。但是,較大的INL可能會導致特定系統的顏色處理算法出錯,從而導致圖像中出現與顏色相關的偽影。

雖然集成方法不具備允許評估每個單獨處理階段的優勢,但可以在特定應用的操作條件下對AFE進行全面評估。AD980x系列的評估板非常方便,簡化了這一設計步驟。

集成路線圖:擴大片上集成范圍以減小尺寸和成本正在成為片上系統開發的一種生活方式。既然標準CMOS工藝可以實現良好的模擬性能,那么將成像系統的部分或全部后端數字處理集成到單個芯片上以滿足特定應用的需求應該是可行的。事實上,ADI公司目前正在生產一款ASIC,以滿足一家大型掃描儀制造商對芯片的需求,該芯片成功地將AFE、數字圖像處理、SRAM、定時生成、CPU和SCSI/EPP接口集成到單個芯片上。在這種復雜程度下,芯片上的電源和接地管理對于最大限度地減少數字噪聲與模擬電路的耦合至關重要。由于需要大驅動器電流,在片上包括SCSI接口的問題的解決方案一直是一個特別具有挑戰性的工作。

審核編輯:郭婷

-

傳感器

+關注

關注

2553文章

51390瀏覽量

756572 -

CCD

+關注

關注

32文章

884瀏覽量

142582 -

運算放大器

+關注

關注

215文章

4969瀏覽量

173563

發布評論請先 登錄

相關推薦

CCD模擬輸出信號處理電路圖

設計實例:心率監測和測量的集成AFE解決方案

基于XRD4460的CCD視頻信號處理電路的設計

CCD信號采集系統的USB接口設計

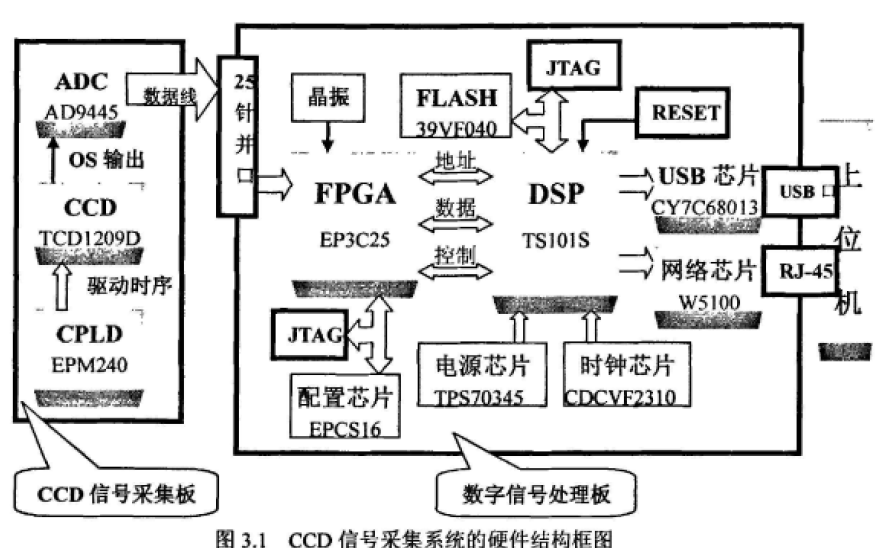

如何使用FPGA和DSP實現高速CCD信號采集處理系統的設計

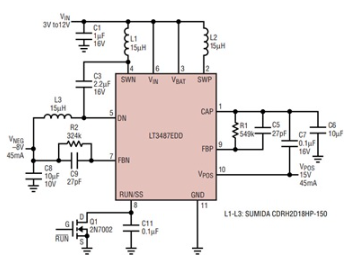

LT3487為CCD應用提供高度集成、高效的偏置電源解決方案

CCD信號處理集成解決方案

CCD信號處理集成解決方案

評論