數(shù)電基礎

板載晶振提供的時鐘信號頻率是固定的,不一定滿足需求,因此需要對基準時鐘進行分頻。要得到更慢的時鐘頻率可以 分頻 ,要得到更快的時鐘頻率可以 倍頻 。我們有兩種方式可以改變頻率,一種是 鎖相環(huán) (PLL,后面章節(jié)會講解),另一種是用 Verilog代碼描述。

用Verilog代碼描述的往往是分頻電路,即 分頻器 。分頻就是輸出信號的頻率是輸入信號的1/n。原理是,輸入信號為計數(shù)脈沖,每n個脈沖輸出就翻轉一次。就可以看作是對輸入信號的“分頻”。十進制的計數(shù)器對應十分頻,如果是二進制的計數(shù)器那就是二分頻,還有四進制、八進制、十六進制等等以此類推。

設計規(guī)劃

實現(xiàn)6分頻,第一種方法是僅實現(xiàn)分頻,第二種方法是降頻:

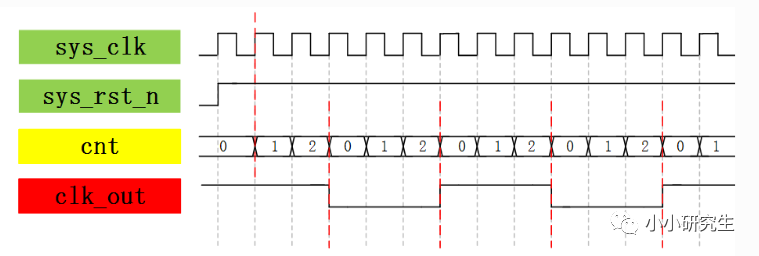

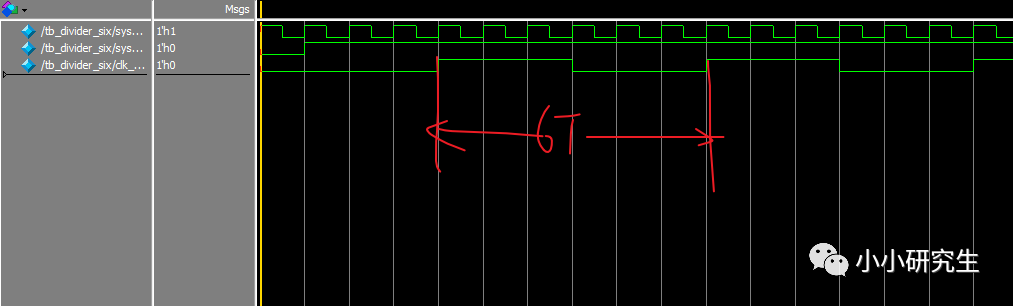

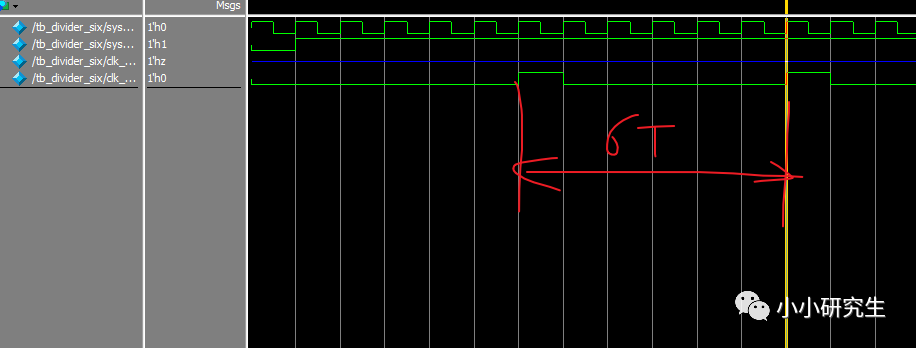

時鐘信號周期為1格,輸出信號周期為6格,因此頻率為原來的1/6,也就是6分頻。

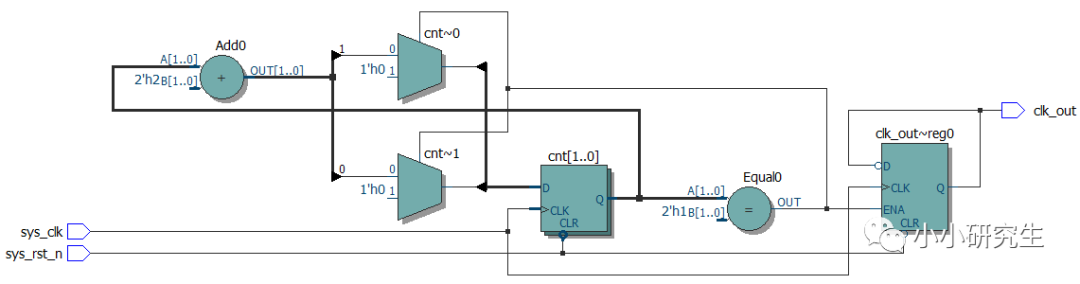

方法一:只需要讓計數(shù)器從0計數(shù)到2,就讓clk_out輸出信號取反。

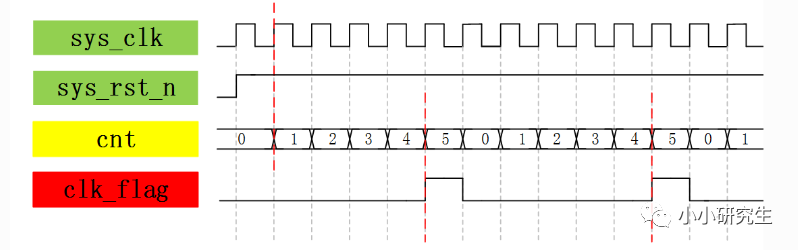

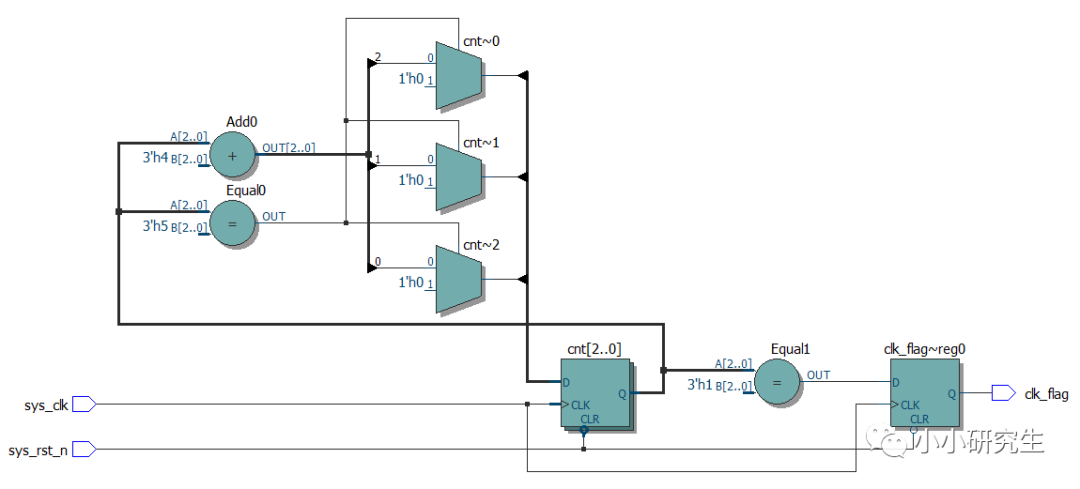

方法二:方法一得到的新時鐘信號和真正的時鐘信號有區(qū)別,在高速系統(tǒng)中 不穩(wěn)定 。因為在FPGA中凡是時鐘信號都要連接到全局時鐘網(wǎng)絡上,它能夠使時鐘信號到達每個寄存器的時間都盡可能相同,以保證更低的時鐘偏斜(Skew)和抖動(Jitter)。用分頻的方式產(chǎn)生的clk_out信號并沒有連接到全局時鐘網(wǎng)絡上,但sys_clk則是由外部晶振直接通過管腳連接到了FPGA的專用時鐘管腳上,自然就會連接到全局時鐘網(wǎng)絡上。因此我們可以產(chǎn)生一個clk_flag標志信號,從0計數(shù)到5,就變高電平,下一個時鐘電平變?yōu)榈碗娖讲⒕S持5個時鐘間隔。和方法1對比,相當于把clk_out的上升沿信號變成了clk_flag的脈沖電平信號。雖然需要多使用一些寄存器資源但是能使系統(tǒng)更加穩(wěn)定。

編寫代碼

module divider_six

(

input wire sys_clk , //系統(tǒng)時鐘50MHz

input wire sys_rst_n ,

output reg clk_out

)

;

reg [1:0] cnt;

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

cnt <= 2'b0;

else if(cnt == 2'd2)

cnt <= 2'b0;

else

cnt <= cnt + 1'b1;

//clk_out:6分頻50%占空比輸出

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

clk_out <= 1'b0;

else if(cnt == 2'd2)

clk_out <= ~clk_out;

endmodule

我們觀察cnt和clk_out的變化條件:計數(shù)器發(fā)生改變的條件有兩個,一個是時鐘上升沿,一個是復位有效(復位下降沿)。計數(shù)器發(fā)生的改變有兩個,要么+1要么清零。清零條件有兩個:復位和溢出。因此第一個always塊中有三個判斷條件:復位和溢出時清零,其他的時候+1。

clk_out的變化條件:時鐘上升沿和復位有效(復位下降沿)。復位時clk_out為低電平,溢出時取反。

module divider_six

(

input wire sys_clk , //系統(tǒng)時鐘50MHz

input wire sys_rst_n ,

output reg clk_flag

);

reg [2:0] cnt;

//cnt:計數(shù)器從0到5循環(huán)計數(shù)

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

cnt <= 3'b0;

else if(cnt == 3'd5)

cnt <= 3'b0;

else

cnt <= cnt + 1'b1;

//clk_flag:脈沖信號指示6分頻

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

clk_flag <= 1'b0;

else if(cnt == 3'd4)

clk_flag <= 1'b1;

else

clk_flag <= 1'b0;

endmodule

和方法1相似,區(qū)別在于輸出的變化不同,從0計數(shù)到4輸出變?yōu)?,否則為0。cnt溢出的條件是計數(shù)到5,輸出的變化是計數(shù)到4。

編寫testbench

`timescale 1ns/1ns

module tb_divider_six();

reg sys_clk;

reg sys_rst_n;

wire clk_out;

//初始化系統(tǒng)時鐘、全局復位

initial begin

sys_clk = 1'b1;

sys_rst_n <= 1'b0;

#20

sys_rst_n <= 1'b1;

end

//sys_clk:模擬系統(tǒng)時鐘,每10ns電平翻轉一次,周期為20ns,頻率為50MHz

always #10 sys_clk = ~sys_clk;

//--------------------divider_sixht_inst--------------------

divider_six divider_six_inst

(

.sys_clk (sys_clk ), //input sys_clk

.sys_rst_n (sys_rst_n ), //input sys_rst_n

.clk_out (clk_out ) //output clk_out

);

endmodule

兩種方法的testbench代碼一樣,除了輸出是clk_out還是clk_flag。

對比波形

如果波形沒有出來,可以在modelsim通過view的transcript查看錯誤。

方法1得到的波形

方法2得到的波形

-

FPGA

+關注

關注

1630文章

21797瀏覽量

606020 -

晶振

+關注

關注

34文章

2899瀏覽量

68315 -

分頻器

+關注

關注

43文章

447瀏覽量

50075 -

Verilog

+關注

關注

28文章

1351瀏覽量

110396 -

時鐘信號

+關注

關注

4文章

453瀏覽量

28666

發(fā)布評論請先 登錄

相關推薦

基于FPGA的通用數(shù)控分頻器設計方案

基于FPGA的任意數(shù)值分頻器的設計

FPGA的分頻器設計

ISE serdes Aurora,init_clk頻率是多少?

基于FPGA 的等占空比任意整數(shù)分頻器的設計

基于CPLD/FPGA的多功能分頻器的設計與實現(xiàn)

什么是分頻器 分頻器介紹

應用于倍頻電路的預置可逆分頻器設計

FPGA實現(xiàn)小數(shù)分頻器

fpga分頻器程序參考程序

用Verilog實現(xiàn)基于FPGA的通用分頻器的設計

FPGA分頻器的設計方法

FPGA學習-分頻器設計

基于FPGA的分頻器設計

基于FPGA的分頻器設計

評論