今年3月,Allegro 和 Sigrity 軟件最新發(fā)布了一系列的產(chǎn)品更新(SPB17.4 QIR4 release)。接下來,我們將陸續(xù)介紹各個產(chǎn)品更新亮點。通過實例講解、視頻演示讓您深入了解AllegroPCB Editor、AllegroSystem Capture、AllegroPackage Designer Plus、SigrityAurora、Sigrity SystemSI、Sigrity SystemPI等產(chǎn)品的新功能及用法,助力您提升設(shè)計質(zhì)量和設(shè)計效率。

Allegro

PCB Editor

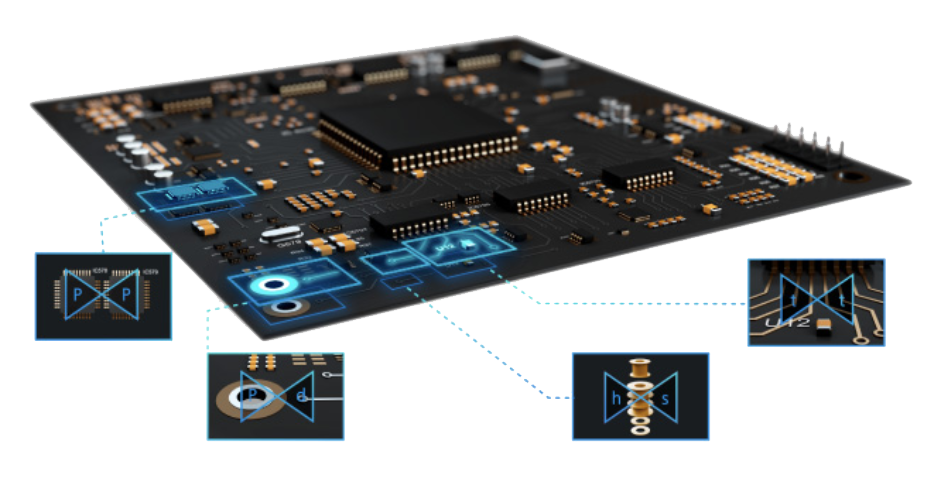

PCB 設(shè)計亮點

動態(tài)背鉆:背鉆信息跟隨設(shè)計,實時更新。設(shè)計調(diào)整后,無需手動更新背鉆信息。

微孔檢查:設(shè)定激光孔相關(guān)的設(shè)計規(guī)則,確保HDI設(shè)計高質(zhì)量交付。

參數(shù)化高速結(jié)構(gòu):

無需繁瑣選擇高速結(jié)構(gòu)要素,輸入?yún)?shù)即可生成所需高速結(jié)構(gòu);

在設(shè)計中,像使用過孔一樣使用高速結(jié)構(gòu)(替換、在Constraint Manager中設(shè)定)。

3D Canvas:讓設(shè)計者看到PCB實體,眼前展示的是組裝完成的PCB。

DFM/DFA設(shè)計:不同區(qū)域設(shè)置不同的DFM/DFA規(guī)則。

Allegro Constraint Compiler:將設(shè)計指南轉(zhuǎn)換為設(shè)計規(guī)則,實現(xiàn)規(guī)則同源,幫助設(shè)計者快速準確復用規(guī)則。

●●●●●●●

Allegro

System Capture

原理圖

設(shè)計亮點

Symbol 設(shè)計更高效:實現(xiàn)跨section的操作;支持文檔類symbol、異構(gòu)部件創(chuàng)建。

原理圖設(shè)計性能:同一層次下的Block順序可調(diào);不同section之間Pin順序可調(diào)。

設(shè)計完整性檢查:基于設(shè)計規(guī)則,可Waive DRC;用戶自定義類別和規(guī)則;可增加DRC注釋。

設(shè)計流程更暢通:Block內(nèi)變量重用;關(guān)聯(lián)Block和變量,以利于Block更新;可生成層次BOM。

PSpice集成:PSpice 仿真模擬設(shè)計;運行 PSpice 高級分析以優(yōu)化電路,估算良率。

AWR-RF集成:用Allegro庫設(shè)計MWO的射頻電路;直接用供應(yīng)商提供的部件進行設(shè)計;RFIP無縫導入PCB制造庫。

●●●●●●●

AllegroPackage

Designer Plus

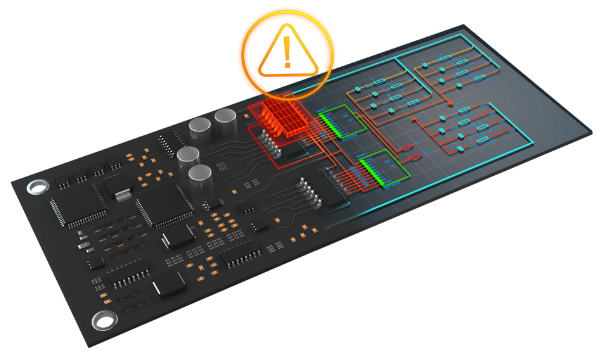

封裝 設(shè)計亮點

焊盤編輯更靈活:多孔焊盤創(chuàng)建、焊盤隔離設(shè)置等功能,幫助用戶更高效地建立想要的焊盤形式。

實時DFM:Package to Package區(qū)域規(guī)則,同名網(wǎng)絡(luò)過孔檢查,更詳細DFM規(guī)則設(shè)置保證設(shè)計滿足制造要求。

參數(shù)化高速結(jié)構(gòu):高速差分結(jié)構(gòu)參數(shù)化創(chuàng)建,全新自動化框選替換操作,提升設(shè)計效率。

硅基供電網(wǎng)絡(luò)參數(shù)化設(shè)計:針對硅基設(shè)計,參數(shù)化創(chuàng)建IC風格電源網(wǎng)絡(luò)、過孔陣列以及電源平面,保證供電和接地充足。

●●●●●●●

Sigrity

Aurora

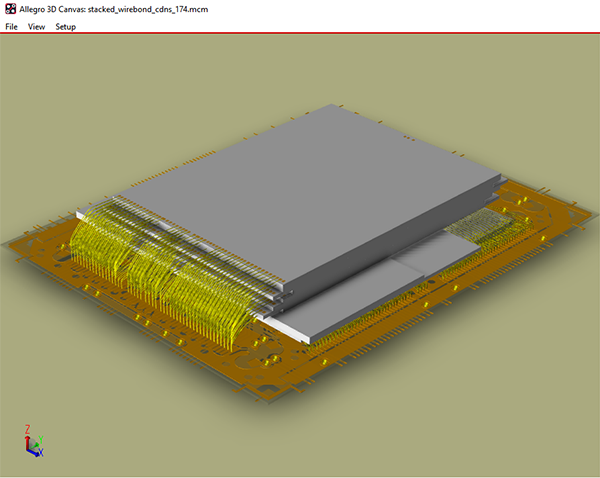

互連建模 仿真亮點

支持對未布線網(wǎng)絡(luò)的拓撲提取及建模:支持布線前按照預拉線曼哈頓長度拓撲提取,并進行信號互連搭建,進行信號完整性仿真分析。

支持Clarity3D Solver和Sigrity PowerSI引擎直接集成:在Aurora環(huán)境中,可以通過選擇需要提取的網(wǎng)絡(luò)調(diào)用Clarity 3D Solver和Sigrity PowerSI引擎進行S參數(shù)的仿真建模。

IR Drop直流電壓降仿真支持自動剪切功能:自動剪切功能,可以加快仿真的速度,針對大型PCB的區(qū)域分析及部分電路仿真提升仿真的速度。

新增生成同軸電纜和雙絞線電纜的模型:生成同軸電纜和雙絞線建模,支持框架及參數(shù)建模和自定義參數(shù)建模的辦法,通過修改編輯支持直接進行信號互連拓撲及信號互連仿真。

●●●●●●●

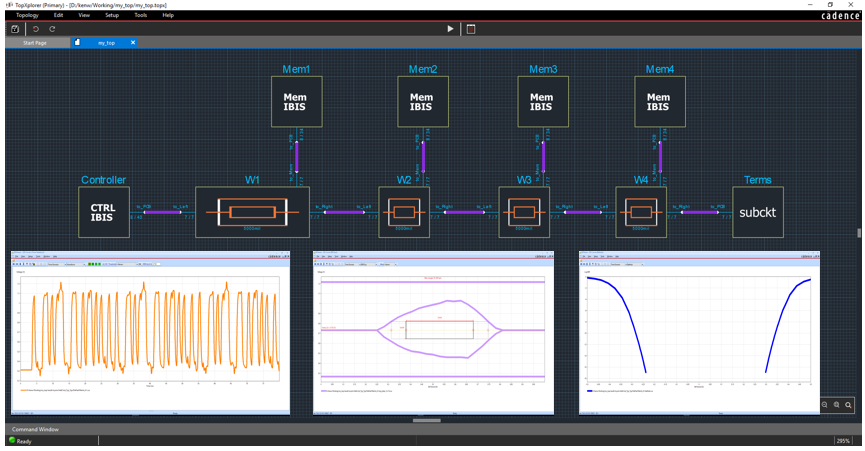

Sigrity

SystemSI

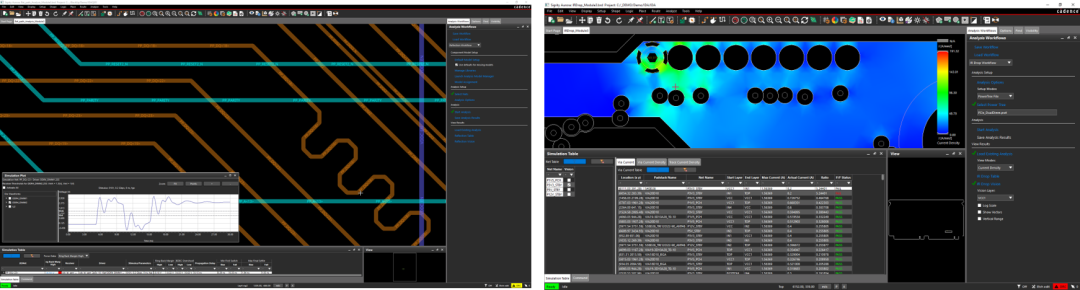

系統(tǒng)信號 仿真亮點

新增支持MIPI-C PHY仿真及標準合規(guī)包檢查:支持MIPI-C仿真與合規(guī)檢查分析,支持信號鏈路拓撲互連及仿真,能自動生成合規(guī)性分析報告,眼圖和誤碼率,抖動結(jié)果。

新增支持GDDR6 接口及JEDEC協(xié)議自動化分析:能夠在仿真接口中直接調(diào)用GDDR6的接口標準,進行仿真結(jié)果的合規(guī)性分析檢查,并支持按照JEDEC協(xié)議自動化分析來輸出合規(guī)性的檢查分析報告。

●●●●●●●

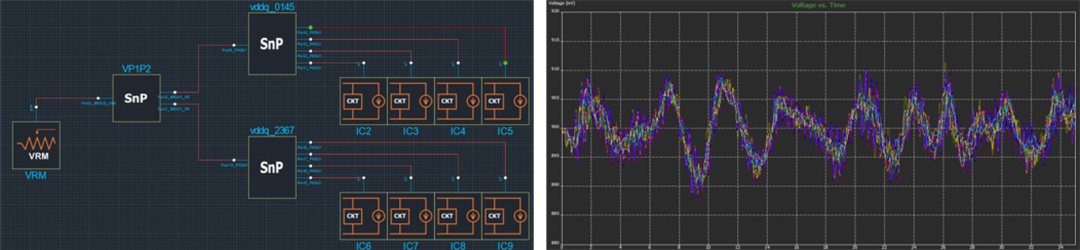

Sigrity

SystemPI

系統(tǒng)電源 仿真亮點

加強支持假設(shè)分析:允許在Sigrity OptimizePIdecap庫中自動尋找合適的元件進行掃描分析,以求出最佳的結(jié)果,支持時域和頻域的范圍內(nèi)掃描結(jié)果優(yōu)化

加強PWL生成功能:支持增強功能,低通,高通,帶通,帶阻濾波器,增加了隨機掃描的噪聲,允許設(shè)置波形的時間及時間步長和停止時間。

-

allegro

+關(guān)注

關(guān)注

42文章

662瀏覽量

145545

發(fā)布評論請先 登錄

相關(guān)推薦

蘋果為iPhone 11系列重新發(fā)布iOS 18.3版本更新

GPU-Z迎來2.62 版本的更新發(fā)布

時隔7年的大版本更新,HDMI 2.2有哪些變化?

Allegro X 23.11 版本更新 I PCB 設(shè)計:梯形布線的分析性能提升

【2K0300先鋒板】【v1.0.241021版本】BSP 更新,歡迎更新使用

Allegro X 23.11 版本更新 I PCB 設(shè)計:與器件關(guān)聯(lián)的動態(tài)禁布區(qū)

Allegro X 23.11 版本更新 I PCB 設(shè)計:圖紙打印和時序調(diào)整

Allegro X 23.11 版本更新 I PCB 設(shè)計:DFA_BOUND 用于 DFA 規(guī)則設(shè)定

求助,如何更新esp-iot-solution中l(wèi)vgl庫的版本?

Allegro X 23.11 版本更新 I 原理圖設(shè)計:變體及 function 的創(chuàng)建與管理

求助,通過VScode構(gòu)建的集成開發(fā)環(huán)境如何更新環(huán)境下的ESP-IDF版本?

chrome插件新版本(v3版本)中的熱更新,即加載更新遠程js的方法探索

Allegro X 23.11 版本更新 - 亮點概要

2024 Allegro X 23.1.1 版本更新——亮點概要

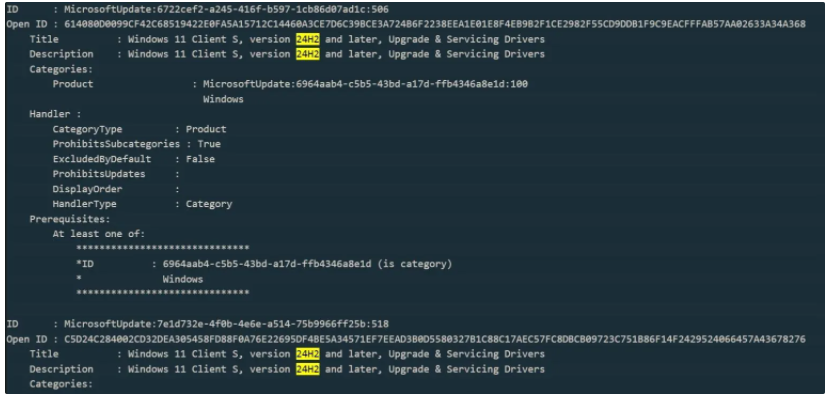

微軟24H2版本已進入測試階段,近期將發(fā)布候選版本更新

版本更新 | 2022 Allegro SPB 17.4 版本更新——亮點概要

版本更新 | 2022 Allegro SPB 17.4 版本更新——亮點概要

評論