引言

Preface

如何快速便捷的完成巨型原型驗證系統的組網,并監測系統的連通性及穩定性?

如何將用戶設計快速布局映射到參與組網的原型驗證系統的每一塊 FPGA?

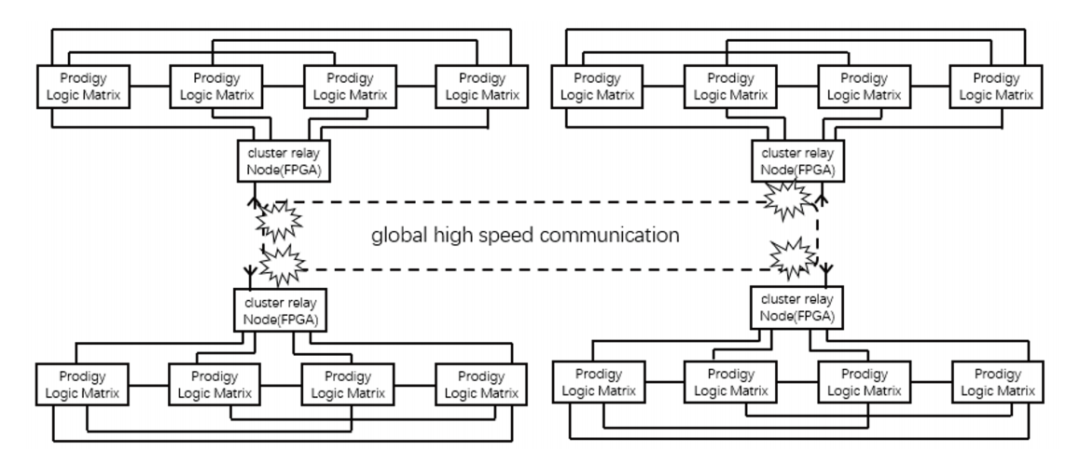

隨著用戶設計規模的日益增大,傳統基于單片 FPGA 或單塊電路板的原型驗證系統已經遠遠不能滿足用戶的設 計驗證需求,設計團隊常需以靈活組網的方式,將數十甚至上百臺原型驗證系統“組裝”為一個完整的巨型原 型驗證系統。鑒于此,以上兩個問題成為了亟需解決的問題。

本次國微思爾芯白皮書《基于組網分割的超大規模設計 FPGA原型驗證解決方案》闡述了S2C對客戶超大型設計的原型驗證,從硬件系統的組建,FPGA 互連組網,外設接口的可擴展性,時鐘及復位等 全局信號同步性處理,到基于 RTL 或 netlist 的設計分割算法,系統級靜態時序分析,增量式設計分割版本迭代的等新挑戰的解決思路。

核心內容

Main Point

基于組網的人工可干預聚類分割

如何快速完成硬件組網并正確將用戶設計分割映射到每一片 FPGA?歡迎下載了解以下內容:

硬件組網資源

組網拓撲定義

基于 RTL 級的聚類分割方案

基于 netlist 級的 TDM 模塊插入

半自動化工具庫

常見標準組網

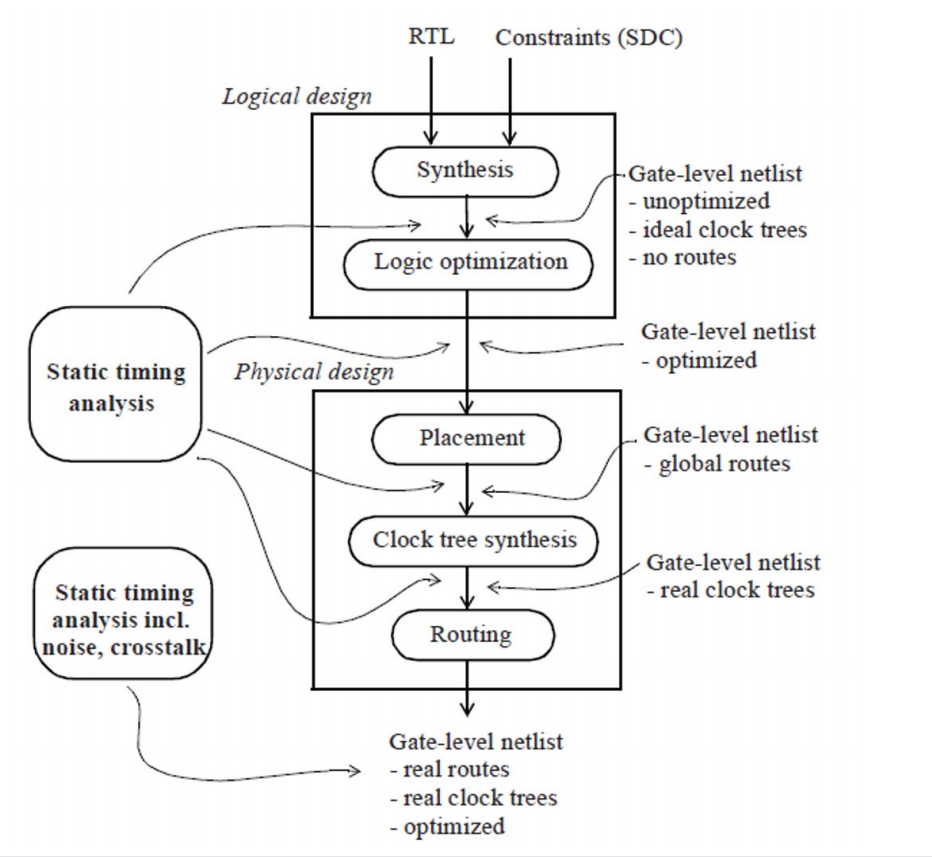

組網聚類分割后的系統靜態時序分析與仿真

如何保證分割后設計運行時的穩定性,并優化設計的運行速度?歡迎下載了解以下內容:

系統級靜態時序分析 SSTA

STA的限制和不足

數字電路設計中的靜態時序分析

-

FPGA

+關注

關注

1630文章

21797瀏覽量

606019

發布評論請先 登錄

相關推薦

微軟發布《GraphRAG實踐應用白皮書》助力開發者

Omdia與華為共發布NPS管理白皮書

Samtec 白皮書 | Flyover?電纜系列下篇

華為發布天線數字化白皮書

Samtec 白皮書 | Flyover?電纜系列中篇

美通社推出《智能科技行業媒體概況》白皮書

IaaS+on+DPU(IoD)+下一代高性能算力底座技術白皮書

移遠通信《5G RedCap技術發展及應用白皮書》重磅發布

大規模 SoC 原型驗證面臨哪些技術挑戰?

白皮書 I 基于組網分割的超大規模設計 FPGA原型驗證解決方案

白皮書 I 基于組網分割的超大規模設計 FPGA原型驗證解決方案

評論