同步動態隨機存儲器(SDRAM)特點:

- 同步:memory工作時需要同步時鐘

- 動態:存儲陣列需要不斷刷新

- 隨機:自由指定地址讀寫數據

- 容量大價格便宜

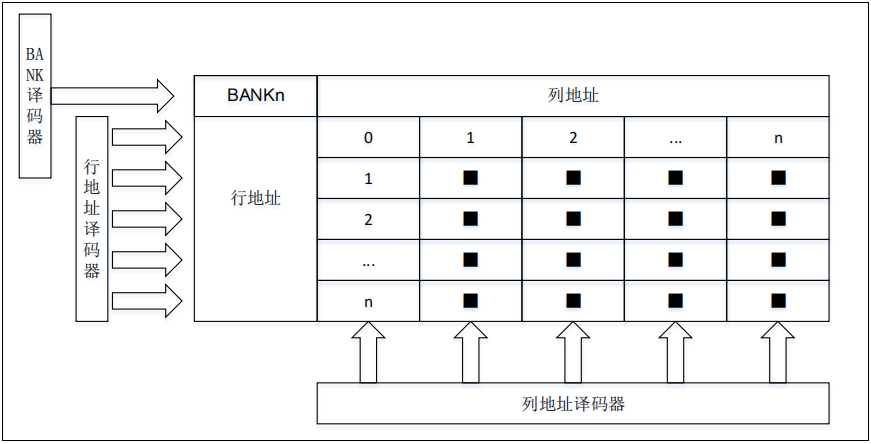

SDRAM存儲結構

SDRAM支持多BANK,通過指定BANK號,行地址,列地址找到目標存儲單元。

圖1 存儲結構

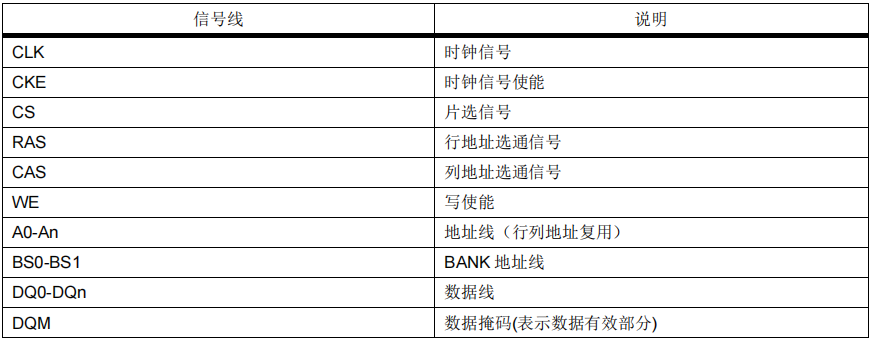

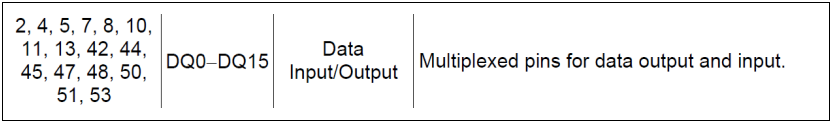

SDRAM信號線

SDRAM內部框圖

如下以W9825G6KH內部框圖舉例:圖2 W9825G6KH框圖

- 1時鐘控制

- 2命令控制

- 3地址控制

- 4存儲陣列,4個BANK

- 5數據

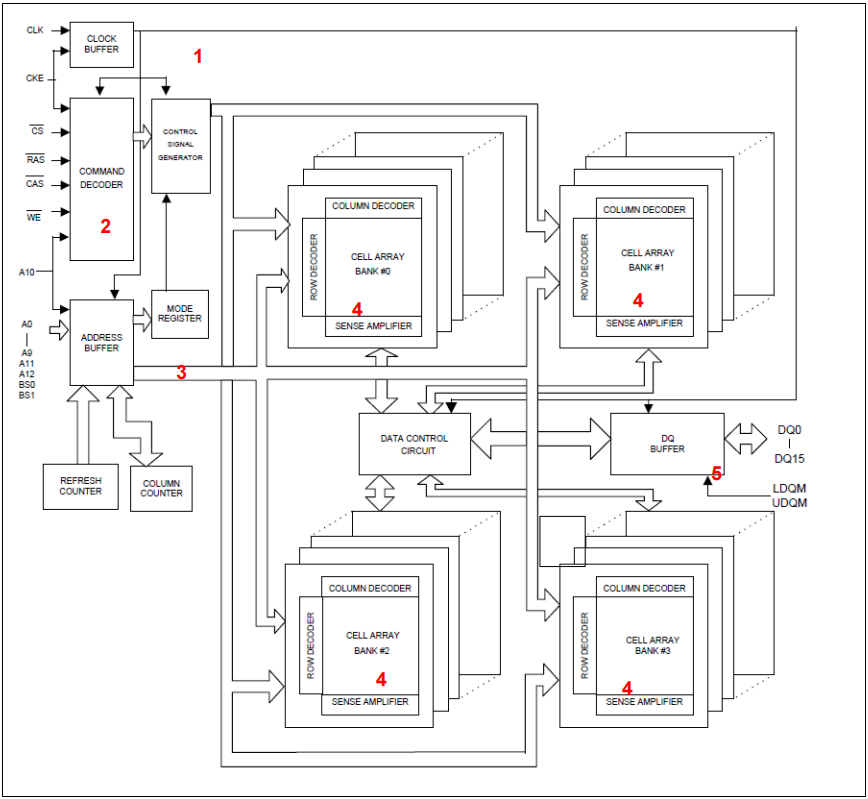

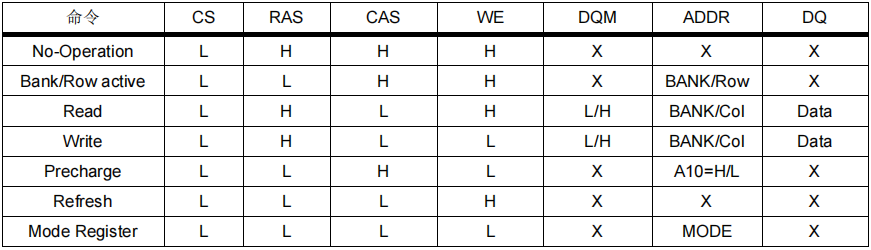

SDRAM常用命令表

SDRAM通過信號線上的不同狀態來產生各種命令。表1 SDRAM命令表 注意:L=Low Level H=High Level X=don't CareA10=H表示Precharge all bank,A10=L表示Precharge選擇的BANK

注意:L=Low Level H=High Level X=don't CareA10=H表示Precharge all bank,A10=L表示Precharge選擇的BANK

- No-Operation表示選中當前設備,當前沒有操作。

- Bank/Row active在對SDRAM進行讀寫時,需要先激活對應的bank和行,該命令用于選擇一個bank的一行進行激活,以便接下來進行讀寫訪問。

- Read激活的行有效之后,對列地址進行尋址,讀出數據。

- Write激活的行有效之后,對列地址進行尋址,寫入數據。

- Precharge預充電命令,在某一行上的讀寫完成之后,關閉現有的行,準備激活新行。

- Refresh刷新命令,SDRAM需要不斷的刷新操作才能保存數據,根據SDRAM設備參數按照固定周期進行刷新。

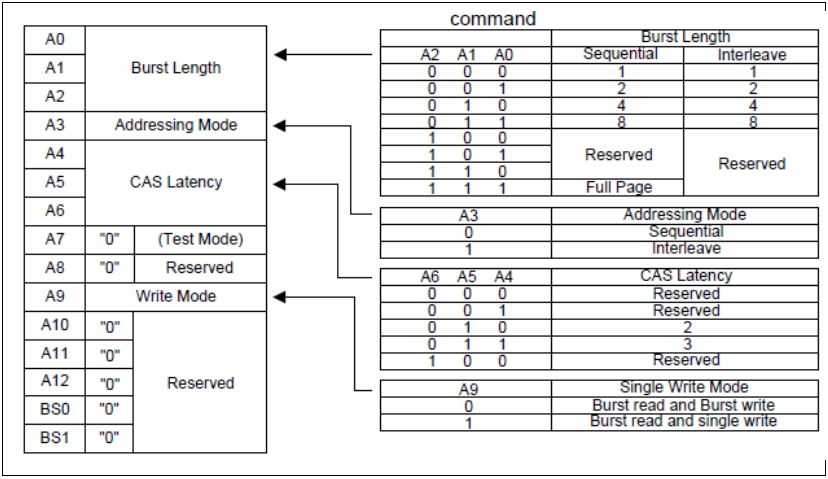

- Load Mode Register加載模式寄存器,修改SDRAM設備的功能參數,burst模式,latency等。

圖3 mode register

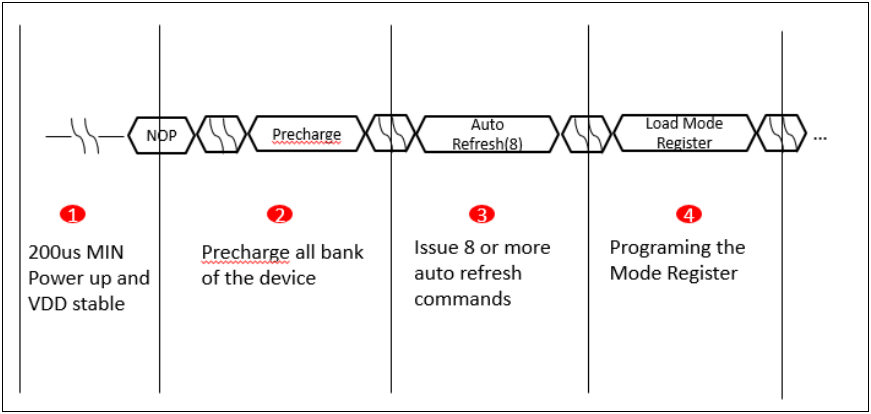

SDRAM Power On Sequence

圖4 SDRAM Power On

AT32 SDRAM控制器

SDRAM控制器主要特點如下:

- 同時支持兩個SDRAM設備

- 支持8位/16位數據總線寬度

- 支持13位行地址,11位列地址(最大可以支持4x16Mx16bit=128MB)

- 支持4個內部Bank

- 支持word/half word/byte訪問

- 支持Burst Read,有6x32bit讀FIFO緩存

- SDRAM時鐘支持HCLK/2, HCLK/3, HCLK/4

- 支持低功耗模式(自刷新模式,掉電模式)

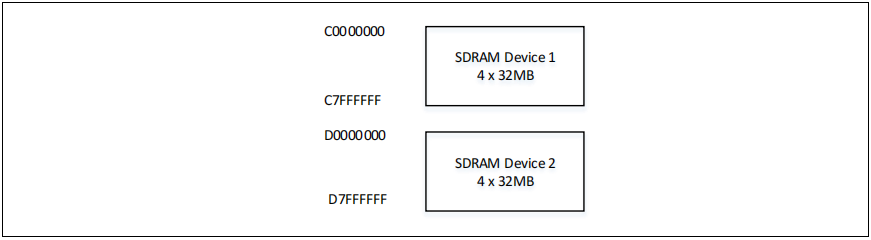

地址映射

圖5 SDRAM地址映射 SDRAM Device1起始地址:0xC0000000SDRAM Device2起始地址:0xD0000000

SDRAM Device1起始地址:0xC0000000SDRAM Device2起始地址:0xD0000000

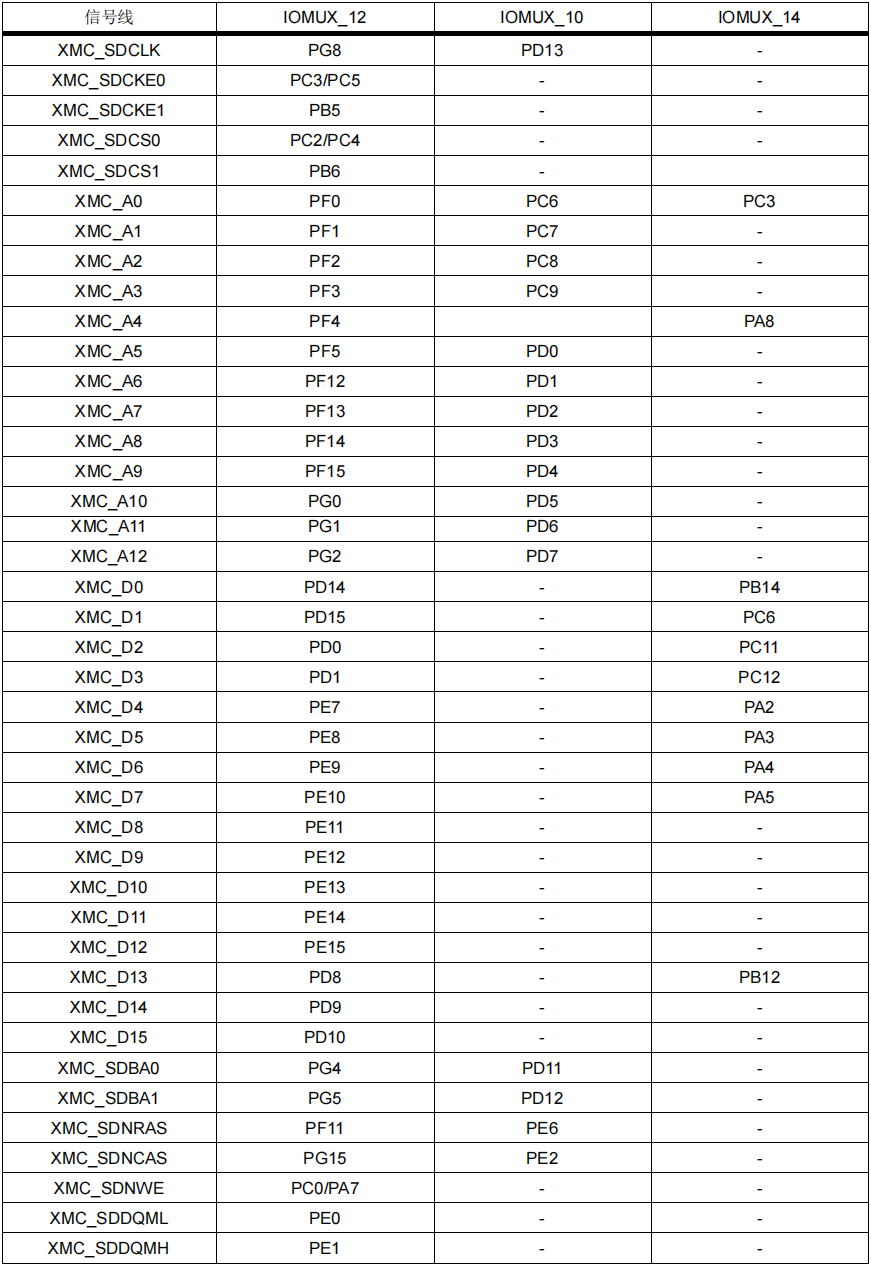

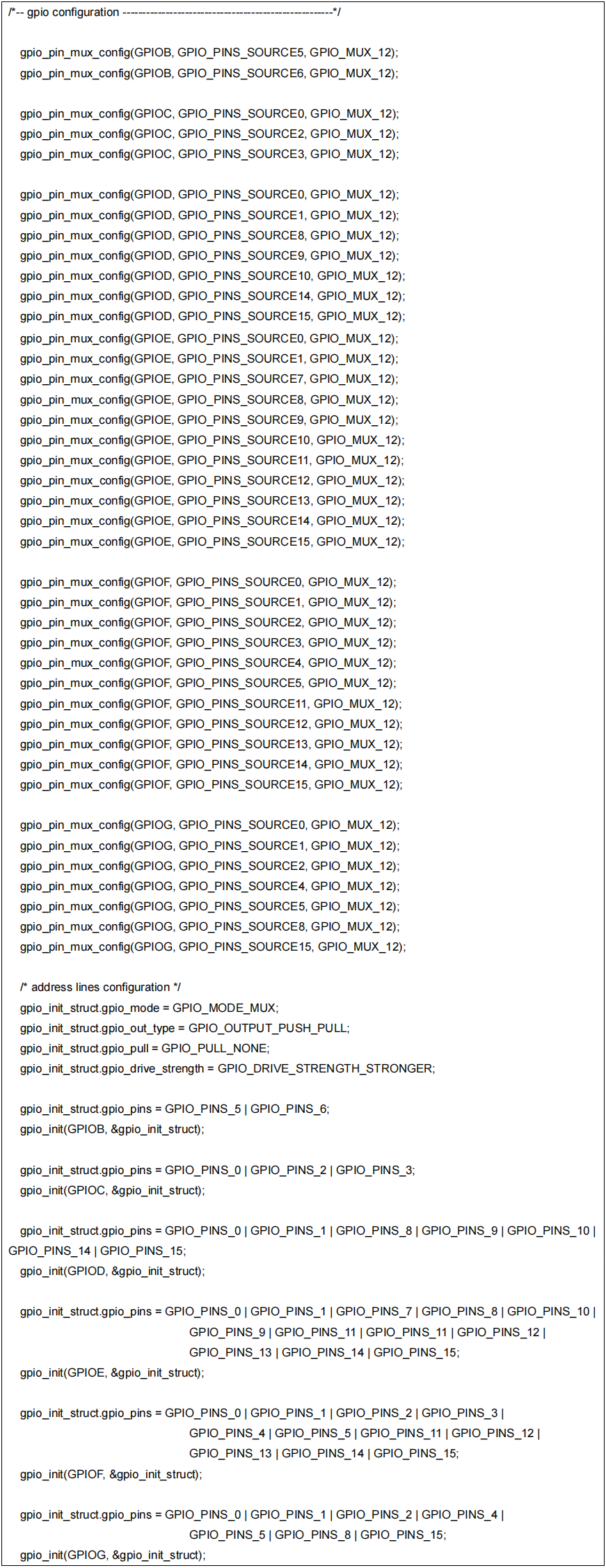

I/O引腳配置

表2 SDRAM IO引腳列表

使用SDRAM IO引腳初始化如下,可根據具體使用引腳進行修改:

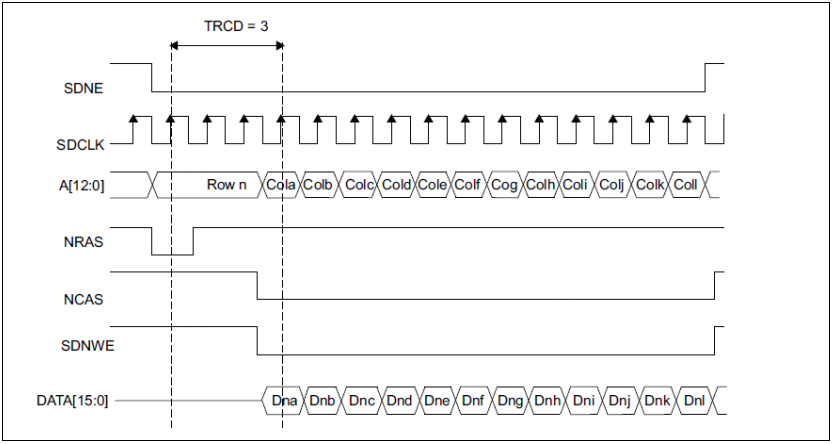

SDRAM讀寫時序

- 寫SDRAM時序

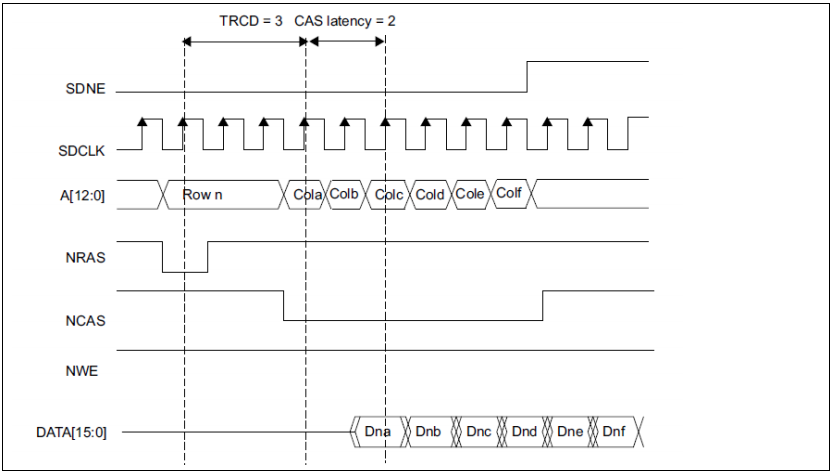

讀SDRAM時序

SDRAM配置

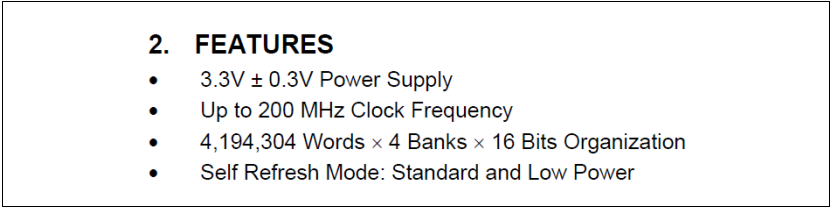

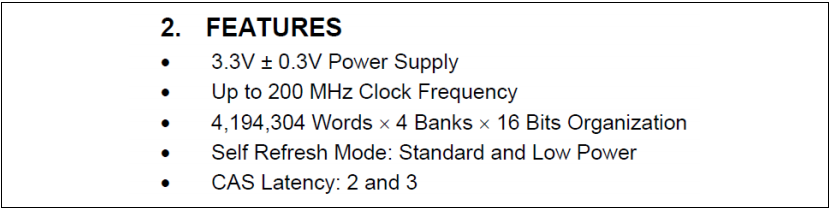

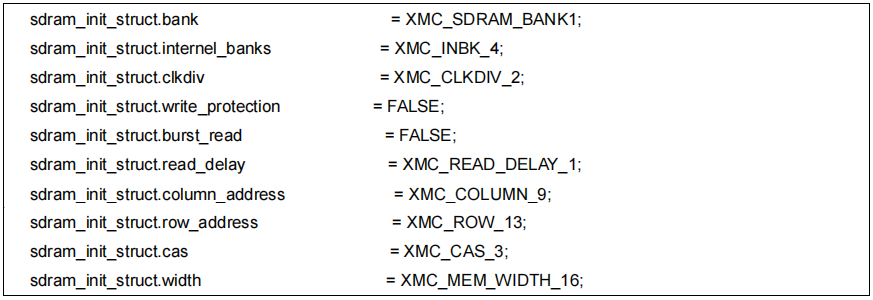

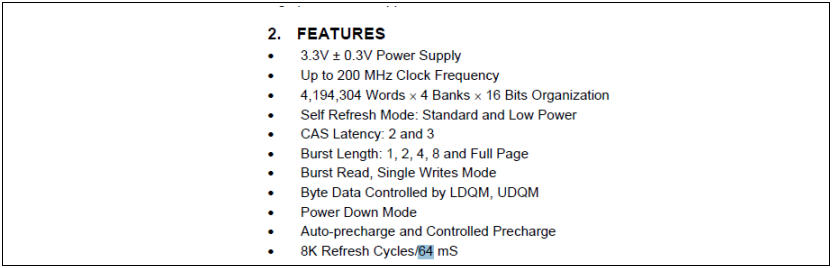

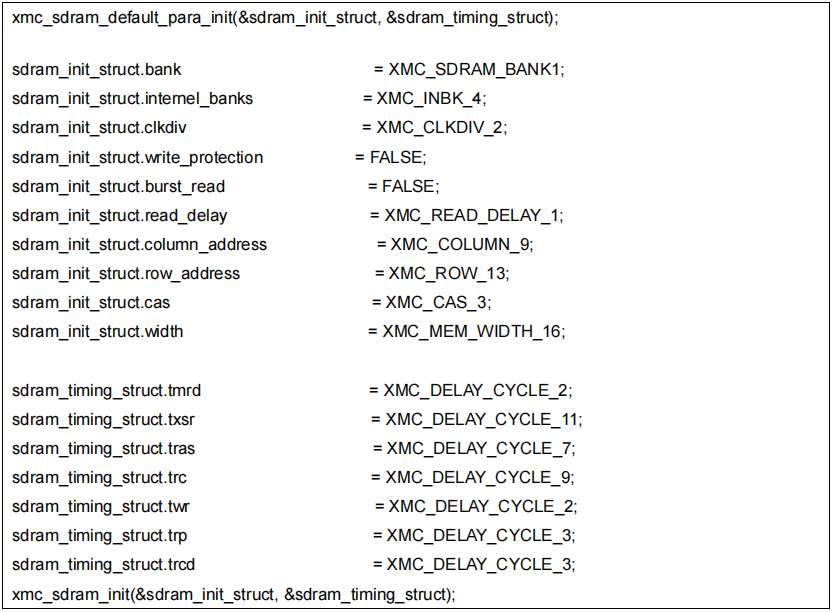

通過配置寄存器SDRAM_CTRLx來設置SDRAM設備的容量,訪問方式等,詳細信息可參考RM。此寄存器包括如下配置:(W9825G6KH作為示例)

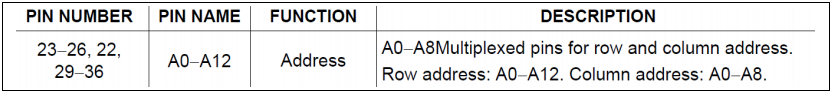

- 行地址/列地址配置

行地址和列地址根據SDRAM設備地址位數進行配置,如下示例:

行地址和列地址根據SDRAM設備地址位數進行配置,如下示例:

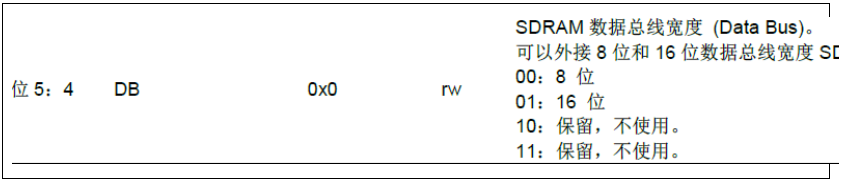

數據總線寬度

根據SDRAM設備支持數據總線寬度進行配置,如下示例支持16bit數據寬度:

根據SDRAM設備支持數據總線寬度進行配置,如下示例支持16bit數據寬度:

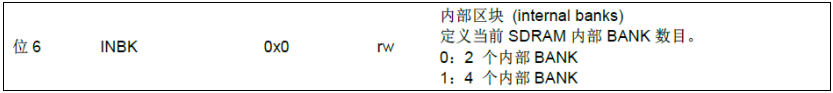

內部區塊個數

SDRAM設備支持內部bank個數:

SDRAM設備支持內部bank個數:

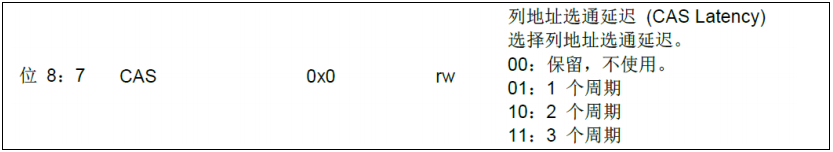

列地址選通延遲(CAS)

SDRAM設備支持延遲:

SDRAM設備支持延遲:

寫保護配置(WRP)

- 如果配置了寫保護,在寫SDRAM設備時會參數Bus error。

- XMC_SDCLK時鐘分頻(CLKDIV)

- BSTR(連續讀)

- RD(讀延時)

配置代碼例程:

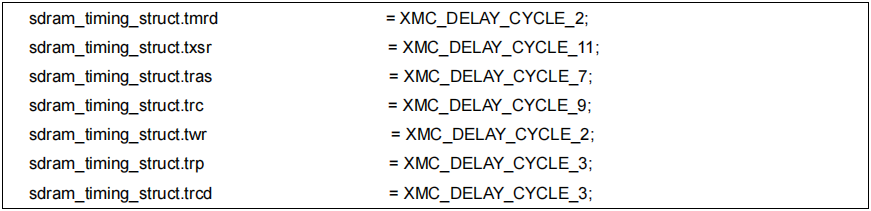

SDRAM時序參數配置

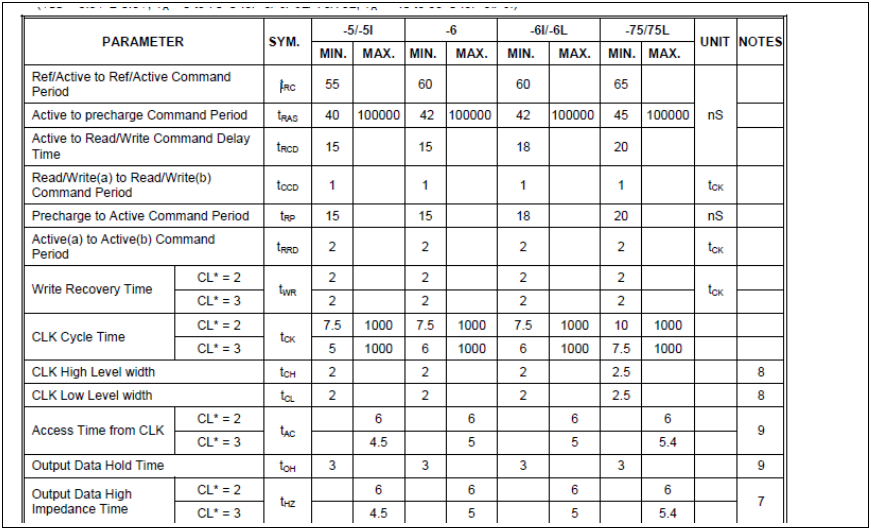

要正常使用SDRAM設備,需要正確配置此部分的實現參數,此參數可在SDRAM設備的datasheet中找到對應值。

配置寄存器SDRAM_TMx:

- TMRD(加載模式寄存器到激活延遲)

- TXSR(退出自刷新延遲)

- TRAS(自刷新周期)

- TRC(刷新命令到激活命令延遲)

- TWR(寫命令到預充電命令延遲)

- TRP(預充電到激活命令延遲)

- TRCD(行激活到列延遲)

例TRCD:最小18ns,SDRAM時鐘144MHz,一個SDRAM時鐘大約為7ns,因此TRCD至少要配置為延遲3個SDRAM時鐘周期。例TWR:SDRAM設備要求2個SDRAM時鐘,因此配置為2

SDRAM設備對時序要求:(W9825G6KH作為示例)

配置代碼例程:

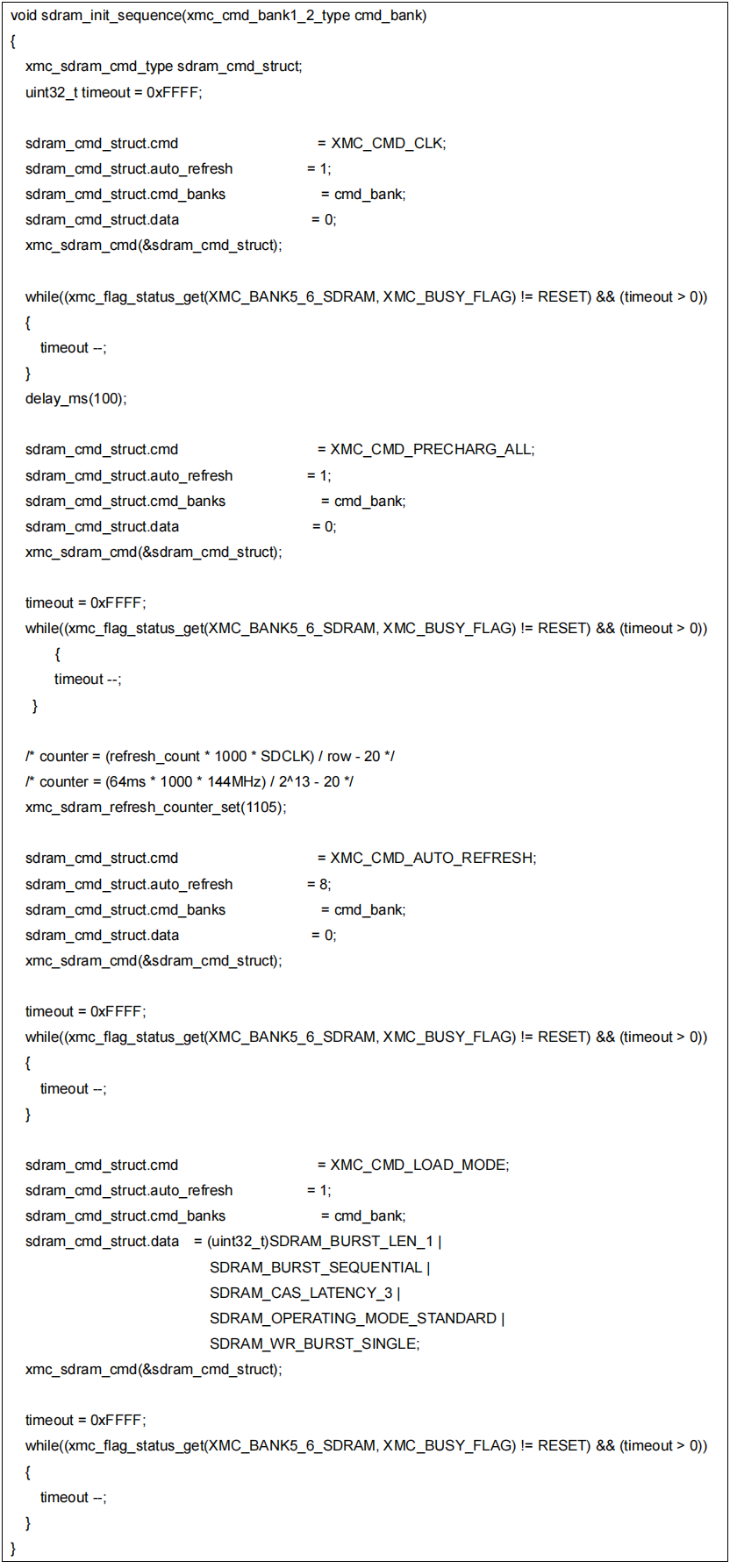

SDRAM啟動序列配置

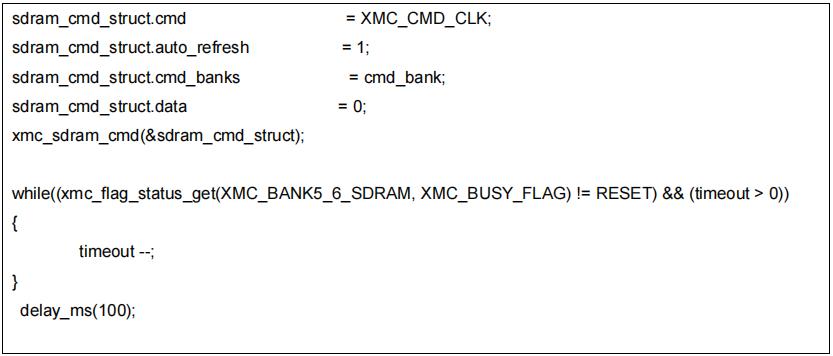

- Clock enable時鐘使能

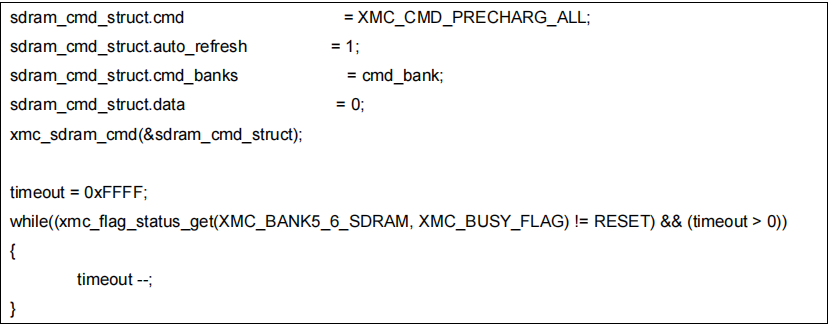

預充電

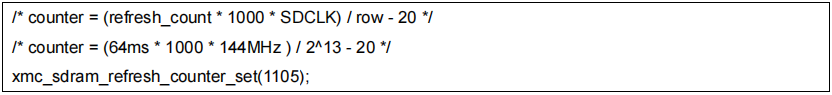

設置刷新計數器

計算方法:counter=(SDRAM resfresh period / number of rows)-20;

刷新速率=64ms/8K=7.8125us;counter=7.8125us*144MHz–20=1105;

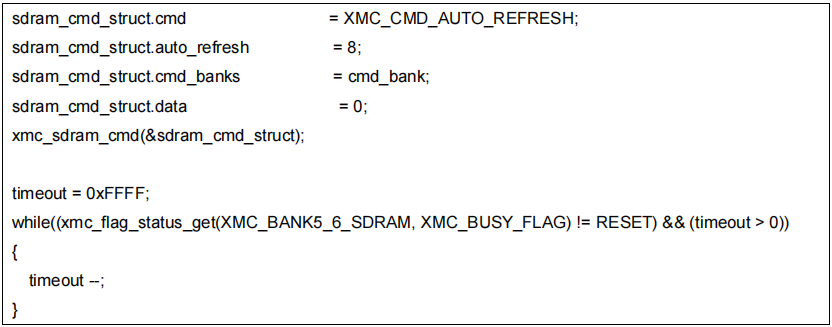

自動刷新

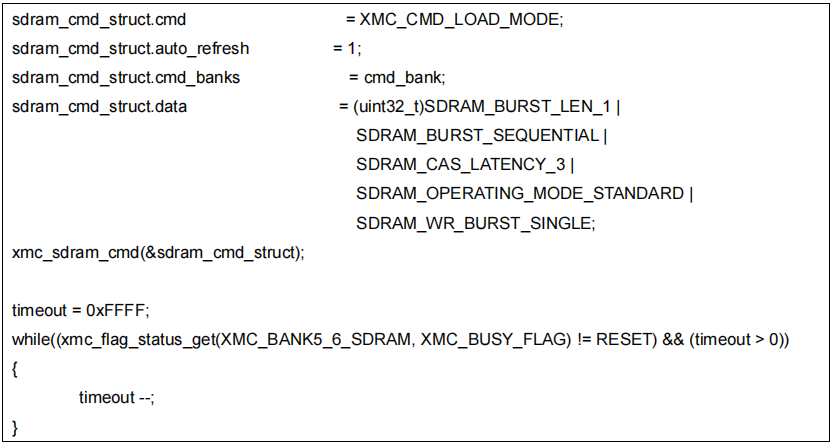

加載模式寄存器

SDRAM例程

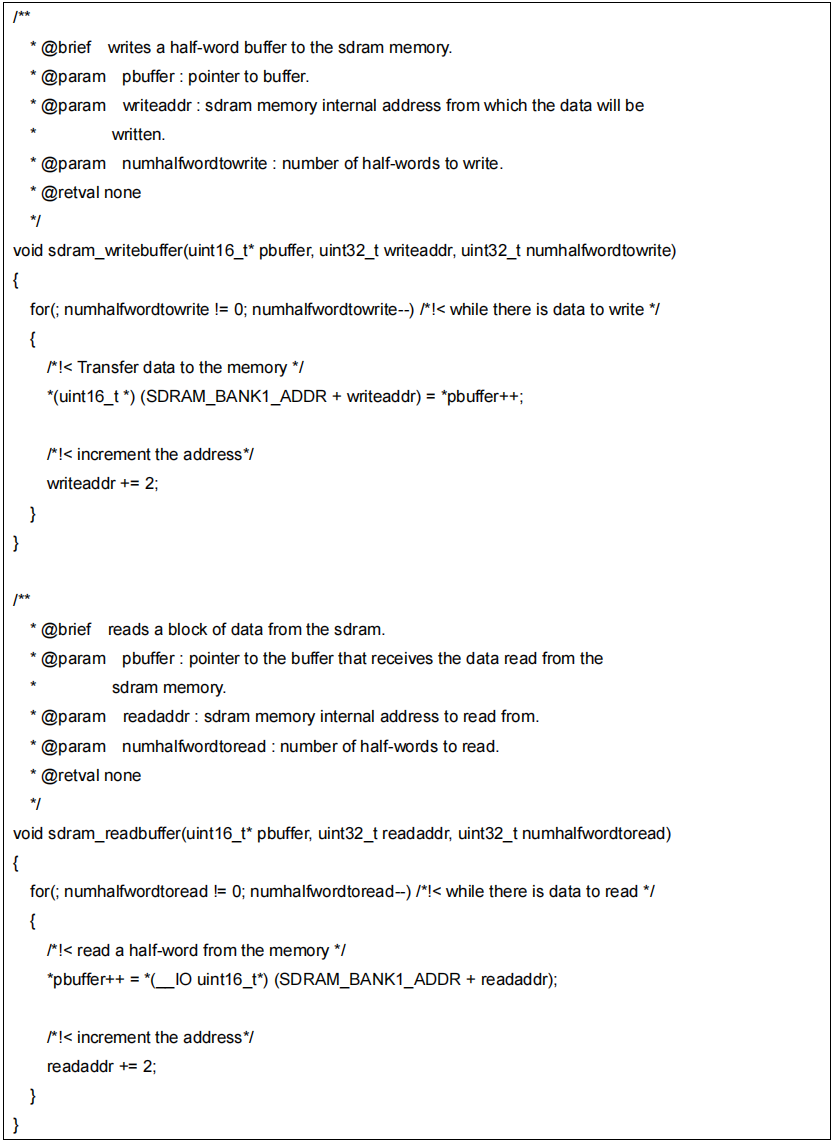

SDRAM Basic此例程配置SDRAM設備之后,對SDRAM設備進行讀寫操作,并判斷讀寫數據是否正確,包括如下步驟:

- GPIO初始化

- SDRAM配置

SDRAM啟動序列

SDRAM讀寫訪問

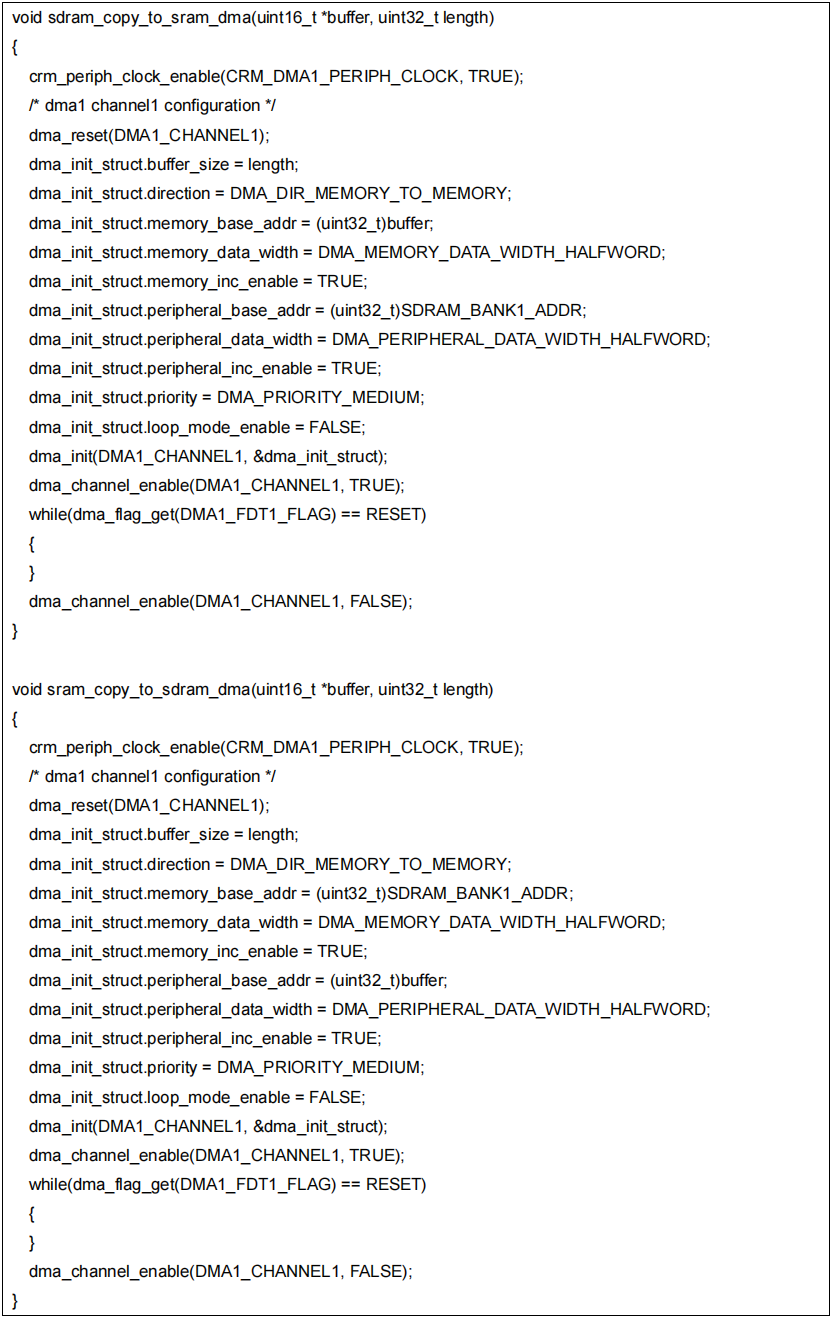

SDRAM DMA此例程配置SDRAM設備之后,使用對SDRAM設備進行讀寫操作,并判斷讀寫數據是否正確,包括如下步驟:

SDRAM DMA此例程配置SDRAM設備之后,使用對SDRAM設備進行讀寫操作,并判斷讀寫數據是否正確,包括如下步驟:

- GPIO初始化(同SDRAM Basic)

- SDRAM配置(同SDRAM Basic)

- SDRAM啟動序列(同SDRAM Basic)

- SDRAN DMA讀寫

關于雅特力雅特力科技于2016年成立,是一家致力于推動全球市場32位微控制器(MCU)創新趨勢的芯片設計公司,專注于ARM Cortex-M4/M0+的32位微控制器研發與創新,全系列采用55nm先進工藝及ARM Cortex-M4高效能或M0+低功耗內核,締造M4業界最高主頻288MHz運算效能,并支持工業級別芯片工作溫度范圍(-40°~105°)。雅特力目前已累積相當多元的終端產品成功案例:如微型打印機、掃地機、光流無人機、熱成像儀、激光雷達、工業縫紉機、伺服驅控、電競周邊市場、斷路器、ADAS、T-BOX、數字電源、電動工具等終端設備應用,廣泛地覆蓋5G、物聯網、消費、商務及工控等領域。

關于雅特力雅特力科技于2016年成立,是一家致力于推動全球市場32位微控制器(MCU)創新趨勢的芯片設計公司,專注于ARM Cortex-M4/M0+的32位微控制器研發與創新,全系列采用55nm先進工藝及ARM Cortex-M4高效能或M0+低功耗內核,締造M4業界最高主頻288MHz運算效能,并支持工業級別芯片工作溫度范圍(-40°~105°)。雅特力目前已累積相當多元的終端產品成功案例:如微型打印機、掃地機、光流無人機、熱成像儀、激光雷達、工業縫紉機、伺服驅控、電競周邊市場、斷路器、ADAS、T-BOX、數字電源、電動工具等終端設備應用,廣泛地覆蓋5G、物聯網、消費、商務及工控等領域。

-

mcu

+關注

關注

146文章

17324瀏覽量

352658 -

控制器

+關注

關注

112文章

16448瀏覽量

179477

發布評論請先 登錄

相關推薦

EE-178:ADSP-TS101S TigerSHARC片上SDRAM控制器

EE-127:ADSP-21065L片內SDRAM控制器

STM32轉AT32代碼轉換

AT32講堂088 | 雅特力AT32F402/F405時鐘配置

AT32講堂087 | 雅特力AT32 IDE快速入門指南

DDR4 SDRAM控制器的主要特點

雅特力AT32 MCU的隨機數生成

AT32講堂085 | 雅特力AT32 MCU HICK時鐘校準

電機控制器mcu的作用 電機控制器mcu的功用是什么

針對 C2000? 微控制器的集成微控制器 (MCU) 電源解決方案數據表

AT32講堂039 | AT32 MCU SDRAM控制器的使用

AT32講堂039 | AT32 MCU SDRAM控制器的使用

評論