時鐘是整個FPGA設計里面無法回避的事物,不能認識時鐘也就沒法做FPGA設計。

· 時鐘控制執行順序·

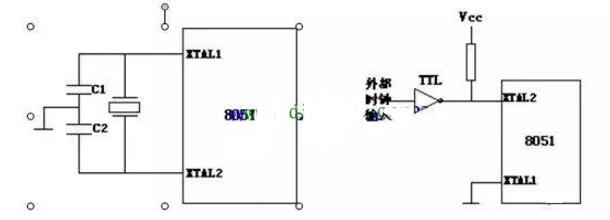

上文解釋了DL程序的并行性,但在設計中需要像C/C++語言的串行控制功能,如先接收外部配置指定,然后接收數據并完成模塊內部配置,再將配置結果反饋到外部,這需要通過時間的精確定位來獲取嚴格的先后關系。

那么怎么來實現呢其實很簡單,假設全部事件需要5個時鐘周期,那么利用一個周期為5的循環計數器來實現。在計數器為1的時候,完成事件1;在計數器為2的時候,完成事件2:……如此循環即可。總結起來就是按照時鐘節拍來完成串行控制。

當然,這樣的電路在FPGA資源的利用上是存在浪費的,因為在執行事件1,用于執行事件2,3,4,5的邏輯處于等待狀態,但其卻始終占用著邏輯資源,也就是這部分電路沒有使能,但是依然存在于FPGA內部。

· 實例分析·

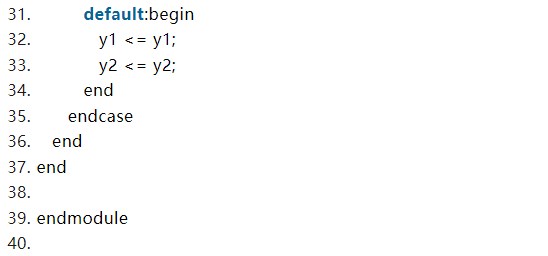

請看如下代碼,建議手動輸入到ise里面,動手綜合后看看實現的RTL圖,看懂電路原理。

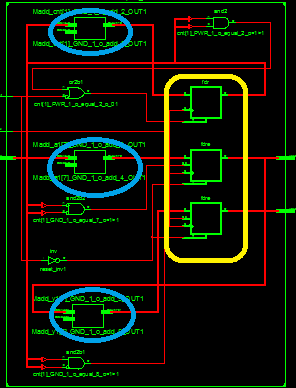

上述代碼綜合后RTL圖如下,淺藍色圓圈圈住的是生成的3個加法器,就是計算cnt和y1,y2的3個加法器。黃色方框里面的是觸發器,負責將結果輸出和反饋到加法器輸入。

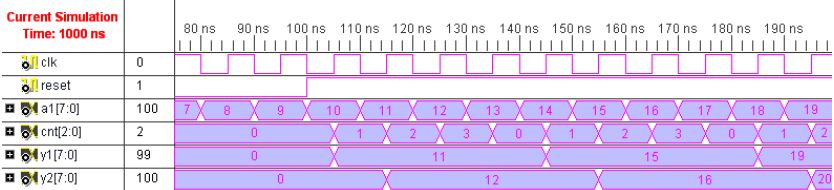

仿真的波形圖如下圖,可以看出,每4個時鐘周期計算一次結果,y1永遠比y2提前一個時鐘周期出結果,y1的值永遠在捕捉到cnt=0的一個上升沿更新,y2永遠在捕獲到cnt=1的上升沿更新。這也是造成y1提前一周期的原因,所有的狀態翻轉都是根據cnt的狀態變化來的,而cnt的變化是時鐘節拍決定的。大家理解好這個例程,也就明白了如何用時鐘操控電路,按照你的想法去運行,同時學會了一段式狀態機的應用。

-

FPGA設計

+關注

關注

9文章

428瀏覽量

26628 -

計數器

+關注

關注

32文章

2261瀏覽量

94982 -

RTL

+關注

關注

1文章

385瀏覽量

59950 -

觸發器

+關注

關注

14文章

2003瀏覽量

61347 -

C++語言

+關注

關注

0文章

147瀏覽量

7027

發布評論請先 登錄

相關推薦

時鐘是電路的實際控制者?

時鐘是電路的實際控制者?

評論