1 SOC和HPU綜合介紹

什么是SOC?SoC稱為系統(tǒng)級(jí)芯片,也稱為片上系統(tǒng)。狹義上講,SOC是將系統(tǒng)關(guān)鍵部件集成在一塊芯片上;從廣義上講, SOC是一個(gè)系統(tǒng),如果說中央處理器(CPU)是大腦,那么SOC就是包括大腦、心臟、眼睛和手的系統(tǒng)。

高通手機(jī)SOC處理器驍龍810芯片,可以看到此芯片主要包括:

- 通用CPU:ARM Cortex-A57和Cortex-A53,CPU主要用于運(yùn)行Android等智能手機(jī)操作系統(tǒng)以及APP程序;

- 特定場景處理器:Adreno 430 GPU、Hexagon DSP、ISP、多媒體處理器等,GPU主要用于3D游戲等場景,DSP主要用于傳感器算法處理;

- 特定功能子系統(tǒng):支持4G LTE的通信基帶處理、GPS/北斗等的定位模塊等;

- WiFi、USB、藍(lán)牙等連接模塊;

- 安全處理模塊;

- 其他一些外圍模塊。

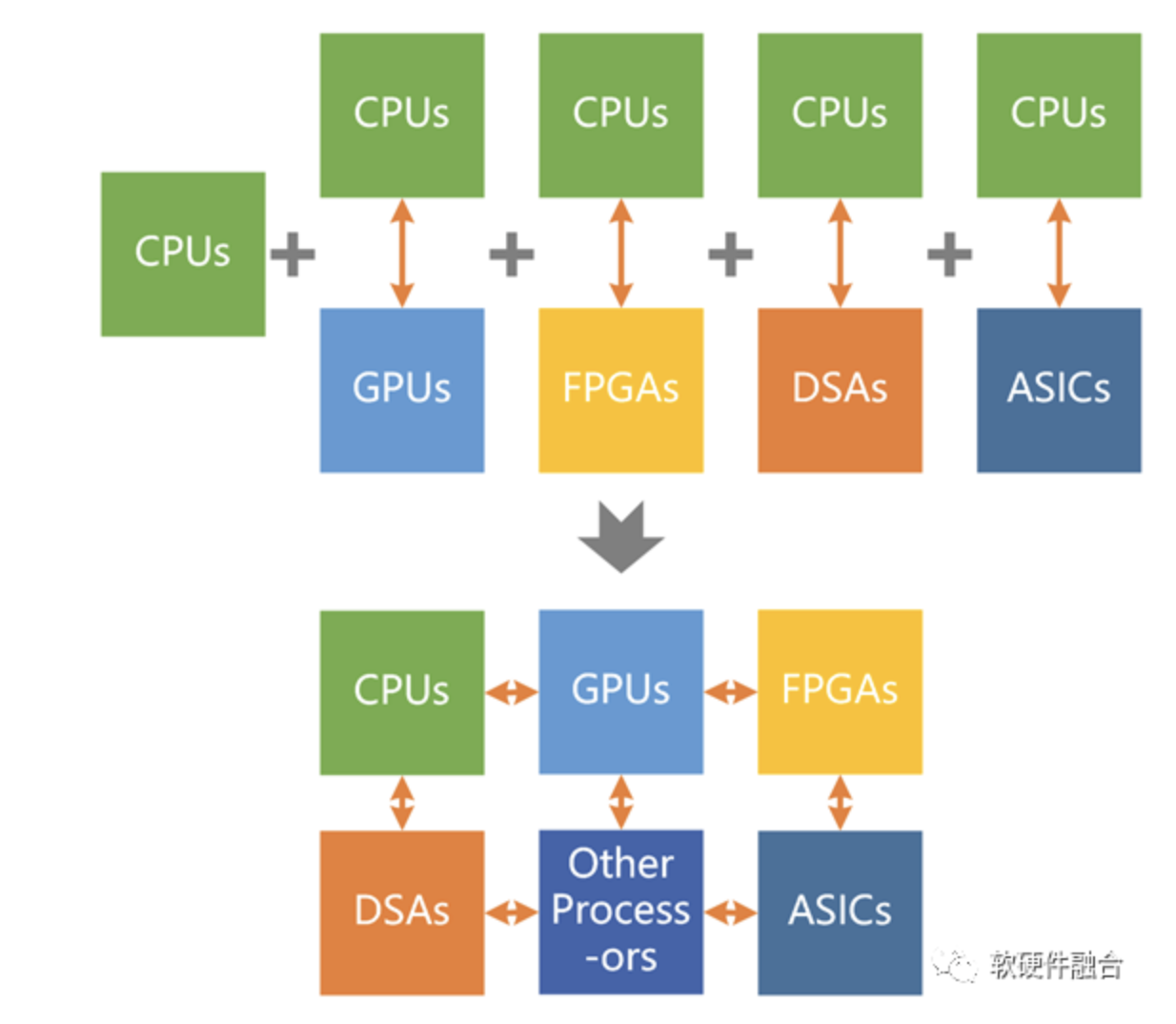

超異構(gòu)計(jì)算,是把CPU同構(gòu)、GPU異構(gòu)、各種DSA異構(gòu)等多種異構(gòu)計(jì)算整合起來的計(jì)算架構(gòu)。超異構(gòu)處理器,則是在芯片層次實(shí)現(xiàn)超異構(gòu)計(jì)算架構(gòu)(言下之意是:超異構(gòu)也可以在板級(jí)的多芯片層次、多計(jì)算節(jié)點(diǎn)的集群層次,甚至數(shù)據(jù)中心等更高層次實(shí)現(xiàn))。

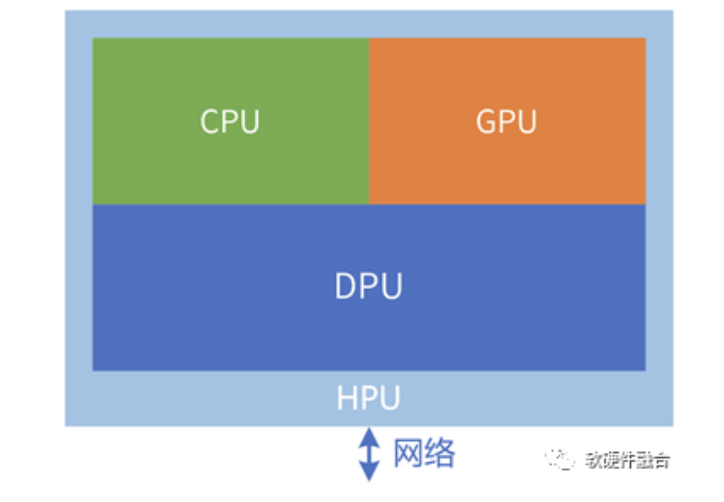

目前,數(shù)據(jù)中心有三大芯片:CPU適合應(yīng)用層的工作,GPU適合業(yè)務(wù)的彈性加速,DPU適合基礎(chǔ)設(shè)施層工作任務(wù)的加速處理。從功能視角看,HPU可以當(dāng)做CPU、GPU和DPU三大功能芯片的融合體。

從馮諾依曼架構(gòu)我們可以得知,計(jì)算機(jī)的五個(gè)組件是輸入設(shè)備、輸出設(shè)備、控制器、運(yùn)算器和內(nèi)存。在現(xiàn)代計(jì)算機(jī)里,通常劃歸為三個(gè)組件:處理器,包含控制器和運(yùn)算器;內(nèi)存,跟馮諾依曼架構(gòu)一致;輸入輸出I/O設(shè)備,輸入輸出都是和外部的通信,把輸入輸出合并為一類設(shè)備。

不同的芯片類型,都是由上述這三類組件組成。其內(nèi)存和I/O設(shè)備沒有本質(zhì)的區(qū)別,核心的區(qū)別則在于處理器部分:

- CPU芯片,其內(nèi)部處理器核都是CPU核。

- GPU芯片,其內(nèi)部處理器核則是數(shù)億千計(jì)的高效能的小CPU核。也因此,GPU本質(zhì)上是眾核并行計(jì)算平臺(tái)。

- 各類DSA芯片,內(nèi)部主要是DSA加速處理器核。

- SOC包含CPU、GPU、ISP等各種偏ASIC級(jí)別的加速處理器核。

- HPU有CPU、GPU、各類DSA等加速處理器核。

從SOC的定義來說,超異構(gòu)處理器也可以歸屬到SOC的范疇。但如果只是稱之為SOC,那無法體現(xiàn)超異構(gòu)處理器和傳統(tǒng)SOC的本質(zhì)區(qū)別。這樣,不利于我們深刻認(rèn)識(shí)超異構(gòu)處理器的創(chuàng)新價(jià)值和重要性所在,以及在支撐超異構(gòu)處理器需要的創(chuàng)新技術(shù)和架構(gòu)方面積極地投入更多的資源。

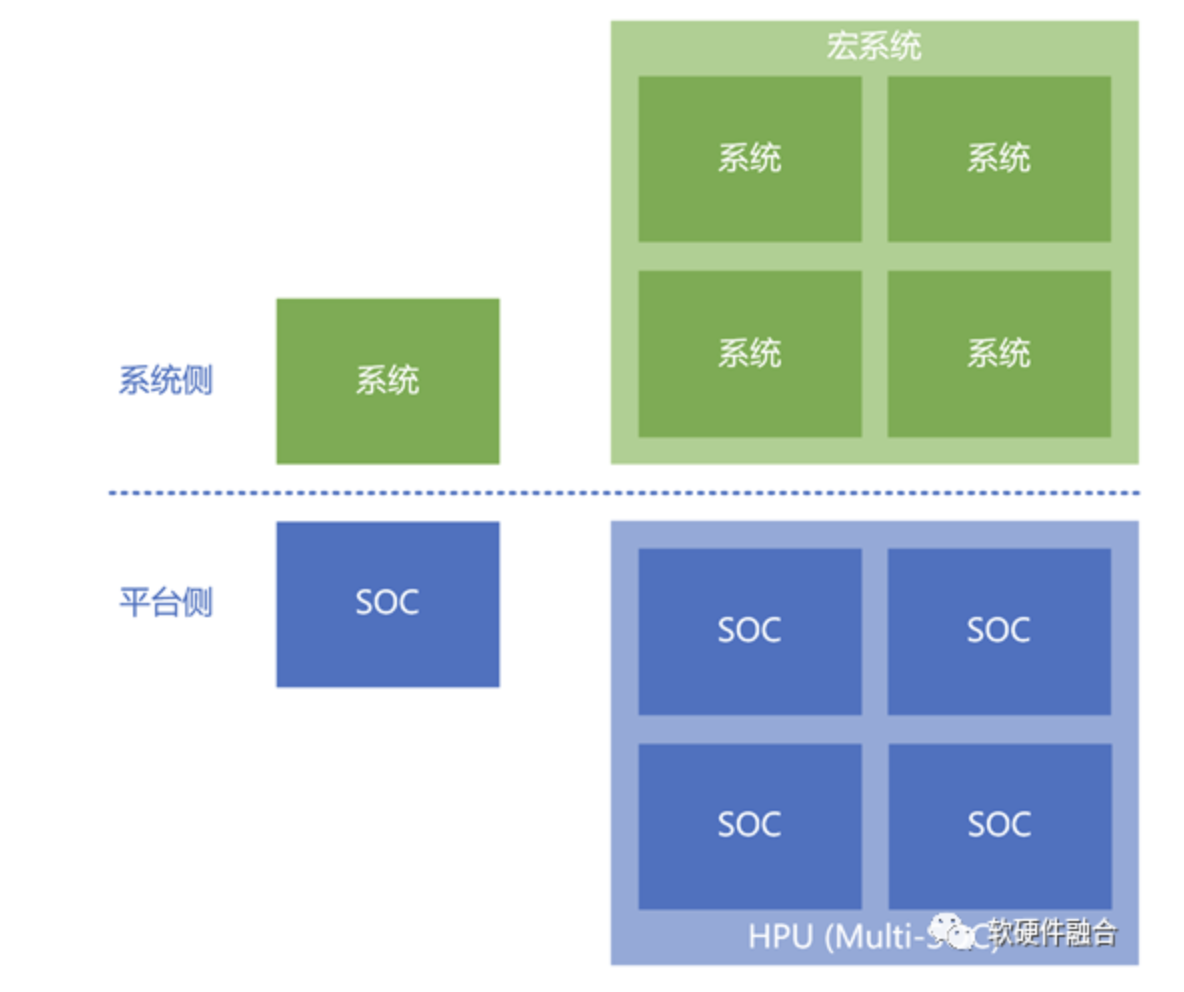

2 區(qū)別1:單系統(tǒng) vs 分布式混合多系統(tǒng)

SOC,顧名思義,系統(tǒng)在芯片上。也即針對(duì)一個(gè)場景的系統(tǒng),設(shè)計(jì)一款芯片。系統(tǒng)和芯片是完全匹配的一對(duì)一的關(guān)系。因?yàn)橄到y(tǒng)多種多樣,這也意味著SOC的類型會(huì)非常地多。

而HPU則定位基礎(chǔ)的通用處理器,針對(duì)的是宏觀的綜合的計(jì)算系統(tǒng)和任務(wù),不針對(duì)任何具體的特定的系統(tǒng)和任務(wù)。也因此,HPU計(jì)算的特征表現(xiàn)在:

- HPU通常通過集群協(xié)作來完成任務(wù);

- 單個(gè)HPU硬件上會(huì)運(yùn)行多個(gè)不同的軟件系統(tǒng)和任務(wù);

- 多個(gè)宏觀的分布式大系統(tǒng),混合交叉地運(yùn)行在多個(gè)HPU上。

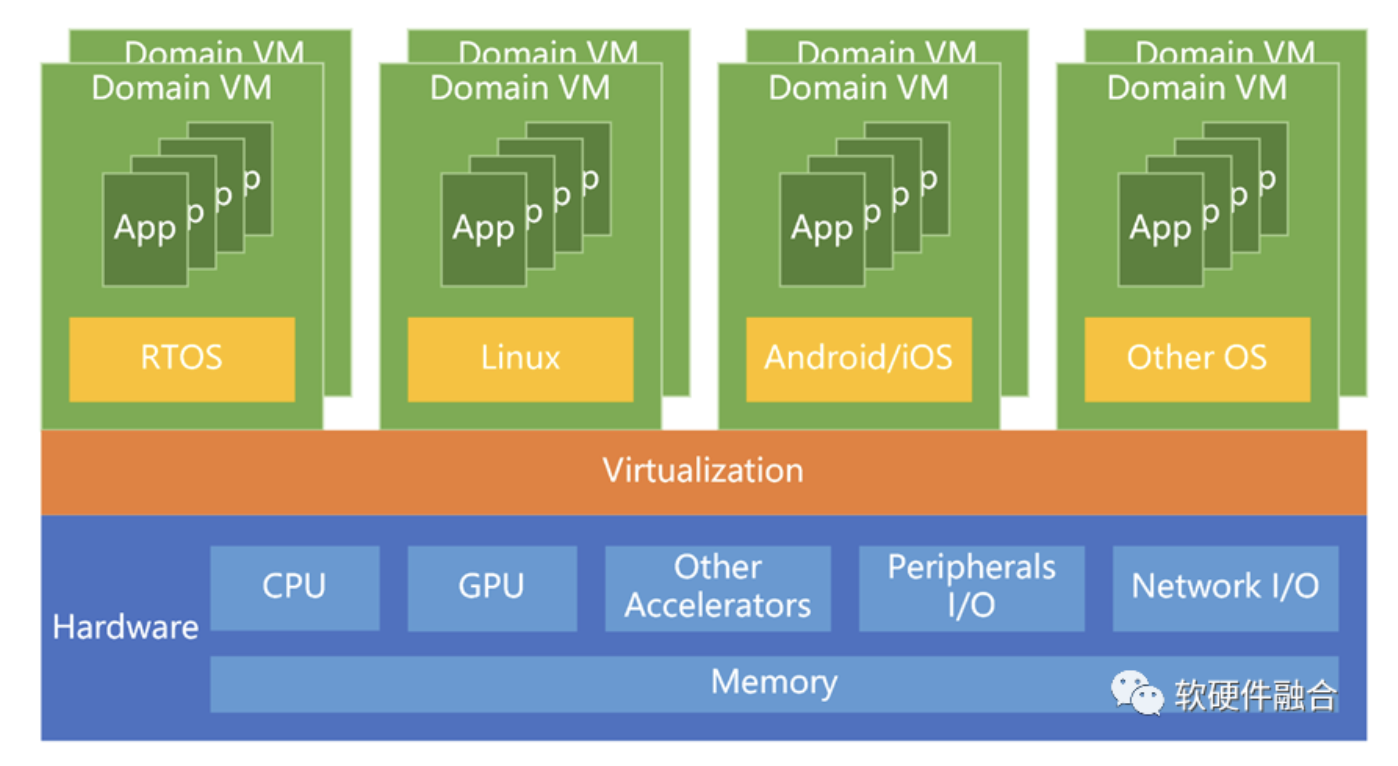

3 區(qū)別2:弱虛擬化 vs 硬件原生虛擬化

虛擬化是HPU和SOC最核心的能力區(qū)別。

SOC因?yàn)槊嫦騿蝹€(gè)系統(tǒng),通常不需要支持虛擬化。有的SOC中的CPU核支持虛擬化,但虛擬化的性能損耗較高;并且僅只有CPU支持虛擬化。其他內(nèi)存、加速器和I/O則不支持虛擬化。

而HPU則不僅僅需要CPU、內(nèi)存的完全硬件虛擬化,其他I/O和加速卡也需要實(shí)現(xiàn)完全的硬件虛擬化。需要強(qiáng)調(diào)的是,I/O虛擬化不僅僅指的是如PCIE SR-IOV或S-IOV的I/O接口的虛擬化,更要實(shí)現(xiàn)I/O內(nèi)部處理引擎的虛擬化。

以汽車芯片為例,汽車EE架構(gòu)目前在經(jīng)歷顛覆性的變化,即從傳統(tǒng)ECU、DCU的架構(gòu)向CCU(Central Control Unit,中央控制器)的架構(gòu)轉(zhuǎn)變。多域融合的自動(dòng)駕駛CCU芯片,跟DCU最鮮明的區(qū)別就在于,是否支持虛擬化。在CCU里,每一個(gè)VM相當(dāng)于傳統(tǒng)的一個(gè)DCU SOC系統(tǒng)。

4 區(qū)別3:軟硬件一體 vs 軟硬件分離

SOC中的軟件通常附著于硬件之上,兩者是匹配的關(guān)系。我們可以根據(jù)硬件的架構(gòu)/接口,定制開發(fā)特定的軟件;也可以通過HAL層,適配標(biāo)準(zhǔn)的軟件和不同的硬件接口。

HPU的要求就要更高很多。HPU上的軟件和硬件沒有直接的關(guān)系。軟件可以運(yùn)行在硬件A,也可以運(yùn)行在硬件B,也可以運(yùn)行在任何其他硬件之上。反過來,硬件也可以運(yùn)行任意可能的軟件。軟件在不同硬件資源上的運(yùn)行和遷移是完全動(dòng)態(tài)的,并且從宏觀角度看,是非常頻繁的。

通常,可以通過虛擬化實(shí)現(xiàn)硬件接口的屏蔽,給軟件提供標(biāo)準(zhǔn)化的硬件,這樣可以方便實(shí)現(xiàn)軟件VM/容器的遷移。但隨著性能的要求越來越高,虛擬化逐漸卸載到了硬件。VM/容器需要通過直通的方式直面硬件接口。虛擬化完全卸載到硬件加速的情況下,需要硬件提供完全一致性的接口/架構(gòu)。

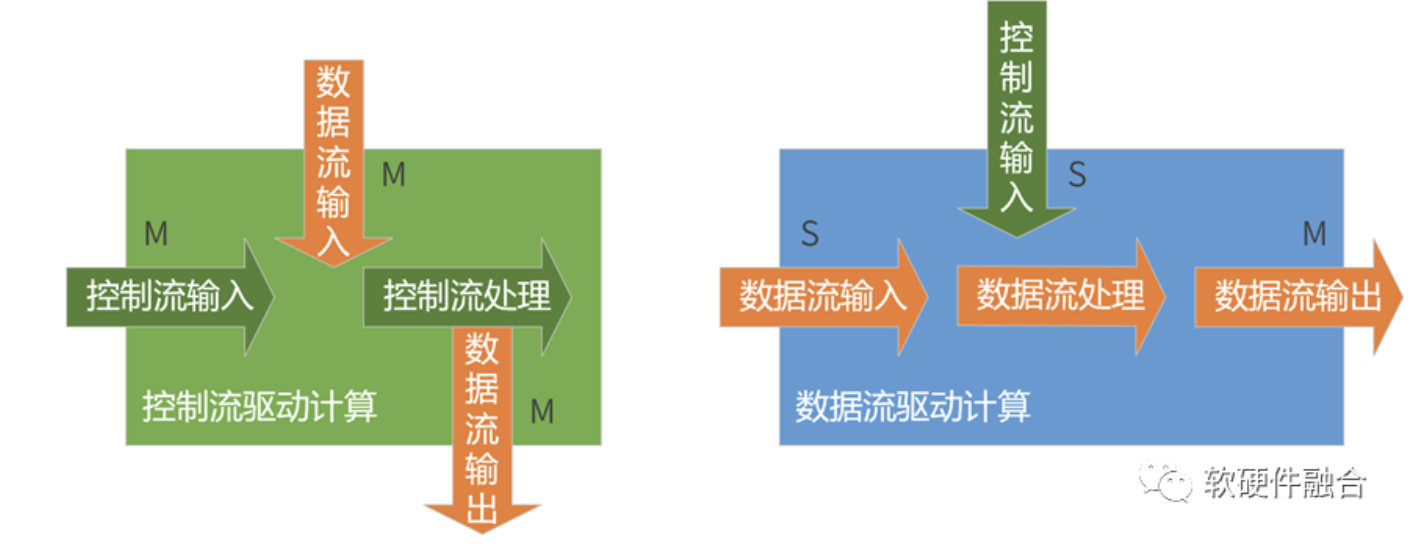

5 區(qū)別4:控制驅(qū)動(dòng) vs 數(shù)據(jù)驅(qū)動(dòng)

在以前,更多的計(jì)算量,更少的數(shù)據(jù)量,因此以CPU單位代表的數(shù)據(jù)流驅(qū)動(dòng)計(jì)算的架構(gòu)是主要的模式。如今,大數(shù)據(jù)計(jì)算時(shí)代,計(jì)算的特征變成“大數(shù)據(jù)量小計(jì)算量”(小計(jì)算量是相對(duì)的說法)的模式,因此,數(shù)據(jù)流驅(qū)動(dòng)計(jì)算的架構(gòu)變成算力的主力擔(dān)當(dāng)。

SOC里,是以CPU為中心的架構(gòu)。主要是依靠嵌入式CPU核中的軟件來驅(qū)動(dòng)整個(gè)SOC的工作運(yùn)轉(zhuǎn)。而在HPU里,則以數(shù)據(jù)為中心,主要依靠數(shù)據(jù)的流動(dòng)來驅(qū)動(dòng)計(jì)算的運(yùn)轉(zhuǎn)。

需要強(qiáng)調(diào)的是,在一些觀點(diǎn)里,大家認(rèn)為:以DPU為中心的計(jì)算架構(gòu),就“天然”是以數(shù)據(jù)為中心的計(jì)算。這個(gè)論斷不完全正確的。以DPU為中心的架構(gòu),依然是以CPU控制驅(qū)動(dòng)整個(gè)板級(jí)系統(tǒng)運(yùn)轉(zhuǎn)的系統(tǒng)架構(gòu),也即是以CPU控制為中心的架構(gòu)。

要真正實(shí)現(xiàn)以數(shù)據(jù)驅(qū)動(dòng)為中心的計(jì)算架構(gòu),需要在底層軟硬件上做非常大的調(diào)整。難度很高,工作量很大。

6 區(qū)別5:軟件的多異構(gòu)協(xié)同 vs 硬件的多異構(gòu)融合

SOC和HPU都是多異構(gòu)組成的混合計(jì)算,區(qū)別在于,SOC僅僅是異構(gòu)的集成,而HPU則需要實(shí)現(xiàn)異構(gòu)的融合。

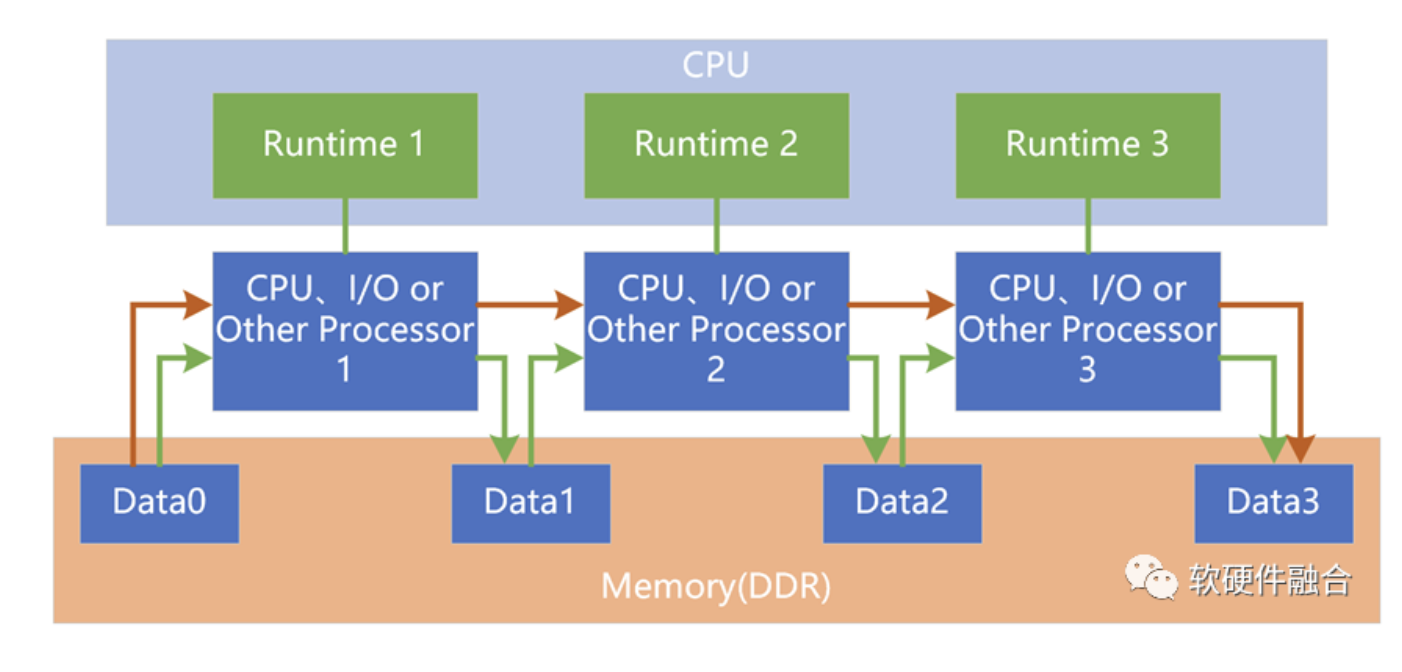

在SOC系統(tǒng)里,每個(gè)加速單元可以看作是CPU+加速單元組成一個(gè)異構(gòu)子系統(tǒng);不同的異構(gòu)子系統(tǒng)之間在硬件上是沒有關(guān)聯(lián)的,需要通過軟件構(gòu)建異構(gòu)子系統(tǒng)之間的交互和協(xié)同。在CPU性能逐漸瓶頸的當(dāng)下,這通常也意味著性能的約束。

而在HPU里,需要實(shí)現(xiàn)硬件層次的不同加速單元之間的直接的、高效的數(shù)據(jù)交互,不需要嵌入式CPU的參與。這樣,在硬件層次,就實(shí)現(xiàn)了CPU、GPU以及各種其他加速單元之間的對(duì)等的深度交互、協(xié)同和融合。

7 區(qū)別6:軟件可編程 vs 多層次可編程

SOC里,其他加速器通常是ASIC層次的,只能施加一些簡單的控制,整個(gè)數(shù)據(jù)面的業(yè)務(wù)邏輯功能是完全確定的,無法軟件編程。在SOC里,能支持軟件編程的通常只有嵌入式CPU。

而在HPU里,可編程能力要更加豐富一些:

- DSA可編程:在每個(gè)計(jì)算節(jié)點(diǎn)都存在,性能敏感,并且功能邏輯不經(jīng)常變化的工作任務(wù),可以劃歸到基礎(chǔ)設(shè)施層。適合DSA加速處理。

- GPU可編程:這里的GPU特指支持并行計(jì)算編程,甚至AI編程,的GPGPU;不是只有圖形加速功能的經(jīng)典GPU。

- CPU可編程:跟SOC中的CPU一樣,支持CPU的完全軟件可編程。

8 區(qū)別7:資源確定 vs 資源彈性可擴(kuò)展

CPU是支持資源(動(dòng)態(tài)的)可擴(kuò)展能力的:通過時(shí)間片把單個(gè)CPU核劃分成千份萬份;再通過同構(gòu)并行把幾十個(gè)CPU核連成一個(gè)大的CPU計(jì)算資源組;還可以通過UPI甚至一致性網(wǎng)絡(luò)的方式實(shí)現(xiàn)多個(gè)CPU芯片的資源擴(kuò)展。

在SOC內(nèi)部,除了CPU可以支持可擴(kuò)展外,其他模塊基本上都是性能確定的設(shè)計(jì),無法支持資源的擴(kuò)展能力。

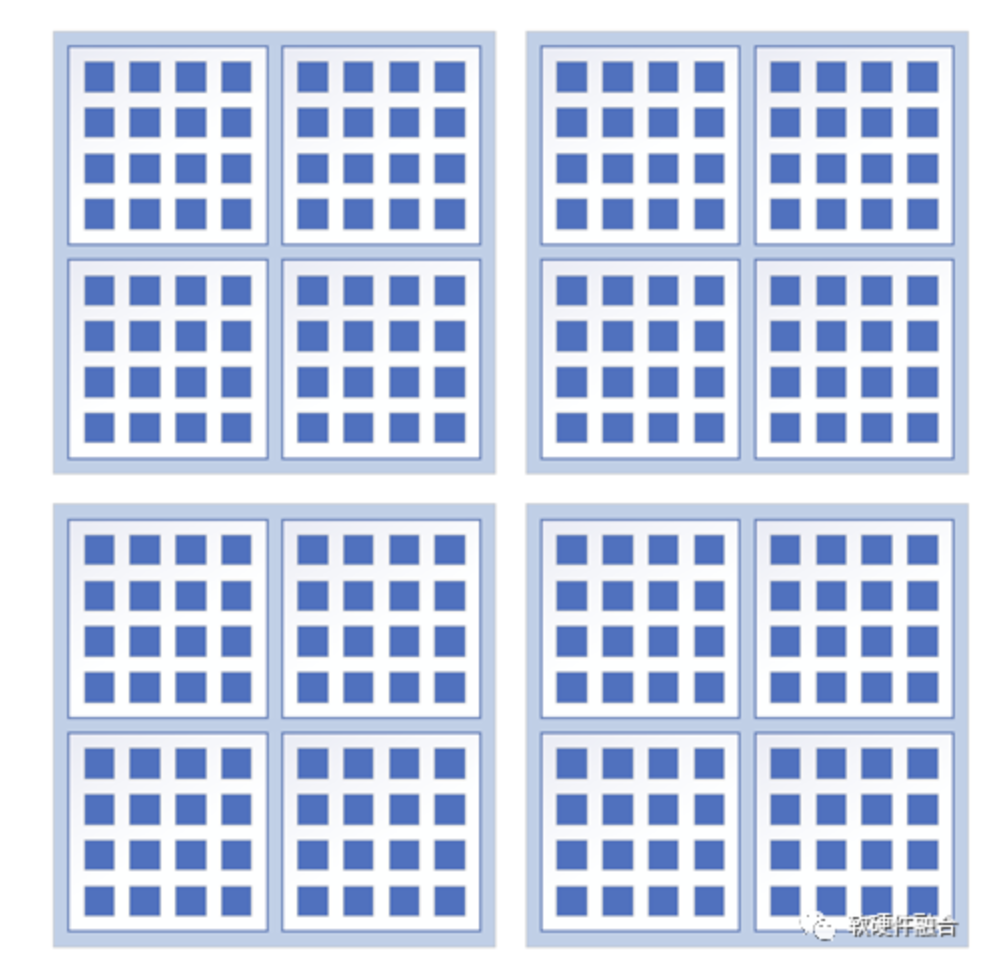

在HPU里,每個(gè)計(jì)算資源,甚至I/O資源,都需要像CPU一樣,支持多個(gè)層次的資源可擴(kuò)展能力。甚至可以實(shí)現(xiàn)數(shù)以萬計(jì)芯片集群的“幾乎無限”的資源擴(kuò)展能力。

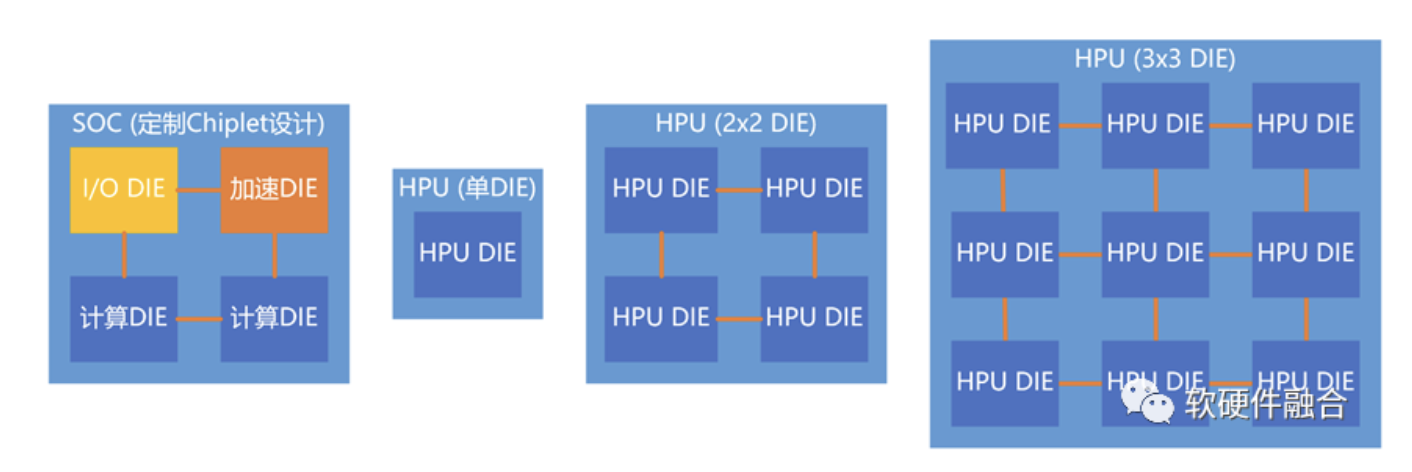

9 區(qū)別8:定制Chiplet vs 原生支持Chiplet

當(dāng)我們做SOC設(shè)計(jì)的時(shí)候,如果需要通過Chiplet優(yōu)化設(shè)計(jì),通常需要針對(duì)性地設(shè)計(jì)若干個(gè)小芯粒。這些芯粒的功能不一樣,然后再把芯粒通過Chiplet連接并封裝成系統(tǒng)芯片。這種方式存在一些問題:

- 優(yōu)化的價(jià)值有限。一個(gè)是部分芯粒可以使用非先進(jìn)工藝,降低成本;另一個(gè)是降低單DIE面積,優(yōu)化良品率。這樣提升的價(jià)值僅僅是百分比的提升。

- 復(fù)用性低。不同型號(hào)的芯粒DIE,非標(biāo)準(zhǔn)器件,本質(zhì)上增加了芯片集成的難度。

HPU采用資源彈性擴(kuò)展的設(shè)計(jì),可以實(shí)現(xiàn):單DIE HPU芯片,以及不同數(shù)量DIE通過Chiplet封裝的不同規(guī)格的HPU芯片。

10 區(qū)別9:設(shè)計(jì)規(guī)模小 vs 設(shè)計(jì)規(guī)模數(shù)量級(jí)提升

目前,隨著系統(tǒng)規(guī)模越來越大,單芯片設(shè)計(jì)規(guī)模也越來越大,但是傳統(tǒng)SOC架構(gòu)所能支撐的系統(tǒng)規(guī)模逐漸逼近上限。規(guī)模上限的意思指的是:雖然工藝和封裝支持更大規(guī)模的芯片設(shè)計(jì),但在傳統(tǒng)架構(gòu)下,突破了規(guī)模上限以后,整個(gè)系統(tǒng)的復(fù)雜度會(huì)急劇上升,很難駕馭;并且,各種資源和性能的利用率會(huì)急劇下降,浪費(fèi)嚴(yán)重,投入產(chǎn)出比不高,不夠經(jīng)濟(jì)。

隨著工藝持續(xù)優(yōu)化,以及Chiplet封裝的進(jìn)步,單芯片的設(shè)計(jì)規(guī)模數(shù)量級(jí)提升。亟需一種創(chuàng)新的架構(gòu)來快速提升“可駕馭條件下”的系統(tǒng)規(guī)模。

SOC支持單系統(tǒng),HPU支持多系統(tǒng)。并且,HPU采用可擴(kuò)展的分布式系統(tǒng)架構(gòu)設(shè)計(jì),每個(gè)子系統(tǒng)相當(dāng)于一個(gè)SOC系統(tǒng)。HPU可駕馭的系統(tǒng)規(guī)模可以做到SOC的10倍甚至100倍。

11 區(qū)別10:專用 vs 通用

SOC是針對(duì)特定的場景,定制開發(fā)的芯片。

HPU面向的是通用的、綜合的復(fù)雜計(jì)算場景,定位在以不變應(yīng)萬變。目前,通用的計(jì)算架構(gòu)主要有三個(gè):

- CPU。CPU又稱GP-CPU,是通用的中央處理單元。CPU可以用在幾乎所有場景。

- CPU+GPU。CPU性能不夠,GPU是眾核并行加速平臺(tái),性能相比CPU數(shù)量級(jí)提升。因此可以把一些性能敏感的并且適合GPU并行計(jì)算的任務(wù)由GPU來完成,其他任務(wù)繼續(xù)放在CPU。

- HPU(CPU+GPU+DSA的融合)。DSA性能效率比GPU要高,同等晶體管資源下,DSA相比GPU可以做到性能數(shù)量級(jí)提升。但DSA僅適合相對(duì)確定性的任務(wù)。依據(jù)二八定律,80%計(jì)算通過DSA完成。然后再使用GPU進(jìn)行剩余性能敏感并且適合并行計(jì)算的任務(wù)加速。剩余不適合加速的部分任務(wù),繼續(xù)放在CPU處理。

**12 總結(jié) **

把上面十個(gè)方面的區(qū)別總結(jié)如下面表格所示。

當(dāng)然,這些是目前我們想到的并且重要的方面。還有很多其他方面的區(qū)別,無法一一列舉。功能上,HPU和SOC都是把很多功能集成在一起,有很多的相似性。但本質(zhì)上,兩者是完全不同的兩個(gè)產(chǎn)品定位和發(fā)展方向。

隨著對(duì)算力的需求持續(xù)不斷的提升,隨著算力網(wǎng)絡(luò)的不斷延伸。未來,幾乎所有的處理器都會(huì)成為類超異構(gòu)架構(gòu)的計(jì)算芯片,超異構(gòu)處理器會(huì)成為支撐宏觀算力的核心底座。

-

傳感器

+關(guān)注

關(guān)注

2553文章

51407瀏覽量

756645 -

處理器

+關(guān)注

關(guān)注

68文章

19409瀏覽量

231202 -

SoC芯片

+關(guān)注

關(guān)注

1文章

617瀏覽量

35045 -

DSA

+關(guān)注

關(guān)注

0文章

50瀏覽量

15256 -

自動(dòng)駕駛

+關(guān)注

關(guān)注

785文章

13932瀏覽量

167016

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

新產(chǎn)品深究,智能手表系統(tǒng)設(shè)計(jì)剖析

C語言深度剖析

深度剖析LED高壓燈帶跟LED低壓燈帶的差異性

從AD8331和ad9215的濾波波形看兩個(gè)板子有性能差異

SoC FPGA有哪些作用?

萌新求助,求ARM內(nèi)核架構(gòu)和SOC架構(gòu)的詳細(xì)資料

各種光纜的詳細(xì)型號(hào)資料說明免費(fèi)下載

SoC功耗是一個(gè)關(guān)鍵的差異化功能

CNC和PLC之間的各種硬件差異

詳細(xì)地剖析HPU和SOC的各種差異

SoC布局中各種IC簡介

詳細(xì)地剖析HPU和SOC的各種差異

詳細(xì)地剖析HPU和SOC的各種差異

評(píng)論