什么是硬件加速引擎

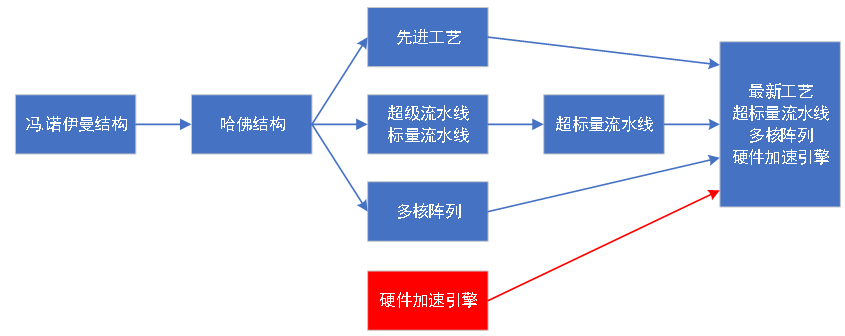

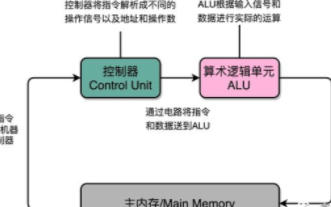

普通計算機用指令運算速度衡量計算性能,而超算則通常用浮點運算速度來衡量其性能。但不管是指令運算還是浮點運算,都脫離不了CPU進行流水線式的指令計算。盡管我們可以通過用先進工藝、采用超標量流水線結構處理器,甚至是多核的陣列來提升CPU的計算性能,但這仍然沒有突破“重圍”,我們一直在一畝三分地徘徊。

我們在個人電腦上打開過多的應用時,由于CPU數量及性能受限,無法承載過多的應用,電腦會逐漸變得很卡。但單純提高CPU的性能,空間受限制,且代價很大。除非是超算中心等首先以性能為目標,對能耗比不那么敏感的應用,否則消費類芯片核心競爭力仍以能功耗及性能為王,承載到芯片上就是PPA(Power Performance Area)。

摩爾定律的終結,我們很難再單一的從CPU身上榨出更多的性能。如果我們將某些復雜耗時的計算,采用專用芯片實現,在完成后再將結果返回給CPU,這樣我們就實現了專用的加速引擎。典型的以個人電腦為例,采用獨立顯卡的配置遠比僅有集成顯卡電腦有著更好的體驗感,因為Nvdia/AMD顯卡的GPU,專用圖形圖像加速運算,降低了CPU的負荷,提高了整機處理應用的能力。

至此,我們的主角終于上場了,世界的最后一塊拼圖,也終于完整了,如下圖所示,為CPU計算加速的方法,終點是最新工藝下,集成硬件加速器的多核超標量流水線處理器。

而我們最后入場的觀眾,即上圖中紅色部分,就是硬件加速引擎。正如前文所述,顯然從CPU的一畝三分地,已經很難再開出質變的花,但硬件加速引擎的引入,讓我們進入了硬件加速的新時代。

我們再梳理一下新提出的概念:硬件加速引擎,也稱為硬件加速器,是一種采用專用加速芯片/模塊,替代CPU完成復雜耗時的大算力操作,其過程不需要或者僅少量CPU的參與。

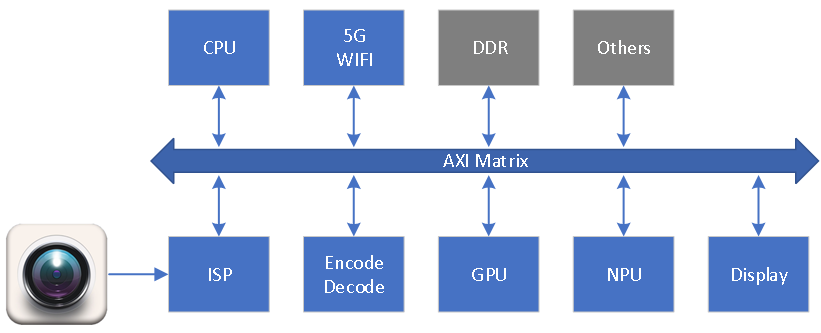

典型的以GPU、DSP、ISP、NPU為例,就是專用的硬件加速引擎。硬件加速引擎的出現,一方面提升了SOC的整體計算性能,另一方面也降低了同等應用場景,對CPU的性能需求。舉例,apple在2021年WWDC上發布了采用自研SOC的全新Macbook系列產品,使用的就是最新自研的號稱地表最強的M1芯片,其規模達到了160億門晶體管,如下圖所示:

M1采用了當時最新的5nm工藝制程,集成8核的CPU,號稱在同等功耗下,達到了2倍目前CPU的最快性能。更為重要的是,M1還集成了眾多專用的硬件加速引擎,協助CPU完成了很多復雜耗時的運算,統計分析主要如下表所示:

| 序號 | 硬件加速引擎 | 功能/性能詳細描述 |

| 1 | GPU | 圖像運算單元,集成128個執行單元,可同時執行24576個線程,運算能力高達2.6TFLOPS。 |

| 2 | Neural Engine | 16核神經網絡加速引擎(NPU),專用卷積網絡推理計算加速,每秒可以進行11億萬次操作。 |

| 3 | Media Encode & Decode Engine | 多媒體視頻編解碼引擎,硬件加速完成視頻的編解碼功能,支持AVS、H.264、H.265等制式。 |

| 4 | Advance Image Signal Processor | 先進的圖像信號處理引擎(ISP),實現實時的圖像采集、Demosaic、3A、2/3D降噪等圖像處理功能。 |

勾勒了一個粗糙的M1的架構圖(其實很多多媒體芯片也是類似的),如下所示,我們簡單梳理一下相關模塊的工作流程。

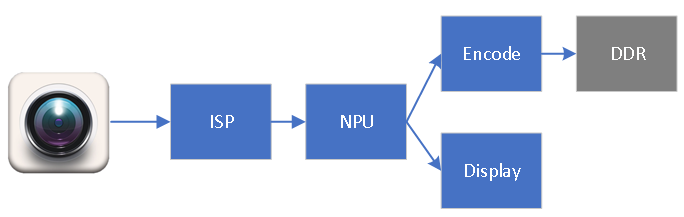

以一個AI人臉識別的視頻拍攝的場景為例,整體計算的流水線如下圖所示,當然每一步還需要CPU參與配置調度,以及DDR讀寫緩存。其中上半部分,采用ISP→NPU→Encode→DDR流水線,實現了實時AI人看臉識別視頻的存儲;下半部分,實現了實時人臉檢測的顯示。

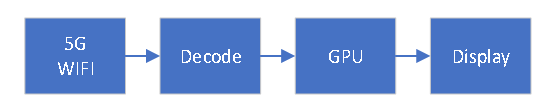

再以體驗一個在線游戲為例,采用下圖的流水線,實現了游戲的實時解碼,圖形圖像的加速運算,以及實時顯示功能。這個過程同樣每個模塊需要DDR參與讀寫,此外,除了少量CPU的配置及調度,CPU很少參與計算,主要由專用硬件加速引擎完成實時的運算。因此專業的事情,專用的模塊做,CPU可以用來做更為復雜的操作,比如文件管理,資源優化等。

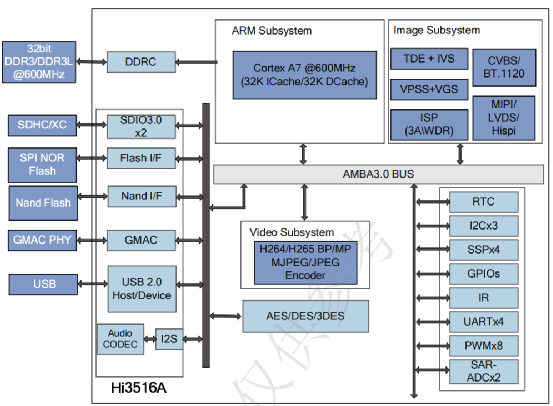

上述例子,CPU與硬件加速引擎協同工作,一起打造了一款號稱地表最強的SOC。這里我們再舉一個例子,以采用硬件加速引擎的方式,降低了產品對CPU的性能要求,從而采用低成本的ARM,在提升性的前提下進一步降低成本。如下圖所示,為海思Hi3516A監控芯片的硬件架構框圖。

該芯片采用單核A7內核作為處理器,主頻運行在600MHz,框圖左側為SoC的高速模塊,右下角為SoC的低速模塊,中下部分AES/DES/3DES為加解密模塊,右上角的CVBS/BT1120為顯示接口,MIPI/LVDS/Hispi圖像采集接口,以上這些組成了SoC的Boot最小系統,以及基本輸入輸出單元。

但這是一款IPC監控芯片,主要用以實現視頻圖像采集,編碼傳輸等功能,為了減小CPU的開銷,協同完成一些復雜的視頻運算,Hi3516A集成了幾個重要的硬件加速引擎,使得其在低碼率,高圖像質量,低功耗方面持續引領行業水平。如下表所示,為Hi3516A芯片繼承的硬件加速引擎,主要如下:

| 序號 | 硬件加速引擎 | 功能/性能詳細描述 |

| 1 | TDE | Two Dimensional Engine,硬件加速實現圖形的繪制,大大減少對CPU的占用,同時又提高了DDR的利用率。 |

| 2 | IVS | Intelligent Video Engine,模塊提供了常用的一些智能分析算法中的一些CV算子,采用硬件實現方式替代CPU進行OpenCV圖像運算。 |

| 3 | VPSS+VGS | Video Processing Sub-System/Video Graph System,硬件加速實現圖像顯示后處理功能,包括降噪、縮放、裁剪、疊加、旋轉等功能。 |

| 5 | ISP | 圖像信號處理引擎(ISP),實現實時的圖像采集、Demosaic、3A、2/3D降噪等圖像處理功能。。 |

| 6 | Video Subsystem | 視頻編碼引擎,支持H.264、H.265等制式以及ROI編碼,最大支持5M Pixel分辨率。 |

IPC芯片可以用規格較低的Cortex A9系列CPU,得益于芯片集成了如上表中專用的硬件加速引擎。采用專用計算模塊完成了圖像處理、視頻編碼、顯示后處理等功能,使得CPU只需要參與配置及調度,同時才有了資源去處理復雜的操作系統任務。

我們總是不斷在追求更快,所以我們窮盡一切辦法去達成目標。硬件加速引擎在傳統CPU無法實現質變的基礎上,實現了計算能力的突破。硬件加速引擎雖然有其專用的局限性,但協同CPU處理,可以以更低的成本及功耗,實現更高的性能,這是當前也是未來計算芯片的大勢所趨。

至此,相信你已經理解了硬件加速引擎的非凡意義,我們也可終于可以提出我們的主題——圖像加速引擎。Hi3516A中的硬件加速引擎都是圖像相關的,本書也將介紹一些基于圖像算法方面的加速,就是我寫本書的初衷。

本書將從傳統圖像加速算法入手,從原理到實現,介紹圖像算法的理論及設計,并且基于Matlab與FPGA開發,講解如何進行硬件加速實現的流程方法。本書適合從事軟件圖像開發的朋友,可以提升你對圖像算法硬件加速的認知;本書同樣也事業FPGA開發的朋友,可以讓你全流程了解如何采用FPGA加速實現一個圖像算法。

在接下來的篇幅,我將從格式轉換、濾波、增強、二值化、銳化、縮放等傳統基礎圖算法入手,從原理到Matlab設計、FPGA加速實現進行由淺入深的詳細介紹。接著,以深度學習LeNet為例,介紹如何在FPGA實現最簡單的硬件加速卷積神經網絡。最后,作為畫龍點睛之筆,我們站上更高的層次,介紹一下傳統ISP和新興的AISP的基本理論概念,以及未來圖像硬件加速的發展走向。

審核編輯:湯梓紅

-

dsp

+關注

關注

554文章

8059瀏覽量

350403 -

芯片

+關注

關注

456文章

51170瀏覽量

427225 -

gpu

+關注

關注

28文章

4774瀏覽量

129350 -

計算機

+關注

關注

19文章

7536瀏覽量

88638 -

硬件

+關注

關注

11文章

3381瀏覽量

66447

原文標題:什么是硬件加速引擎?

文章出處:【微信號:數字芯片設計工程師,微信公眾號:數字芯片設計工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

MPU6050簡介

CAN通信總線接口和XFMC內存擴展接口

MPU6050相關資料分享

N32G4FR系列芯片用戶手冊

N32G457系列芯片用戶手冊

N32G452系列芯片用戶手冊

N32L40x系列芯片產品手冊

N32G4FR系列芯片數據手冊

N32G452系列芯片數據手冊

基于MPU-3000?系列運動處理組件的三軸陀螺

基于VxWorks的硬件加速技術探討

圖像處理硬件加速引擎是什么 如何提高CPU芯片性能

什么是硬件加速引擎?

什么是硬件加速引擎?

評論