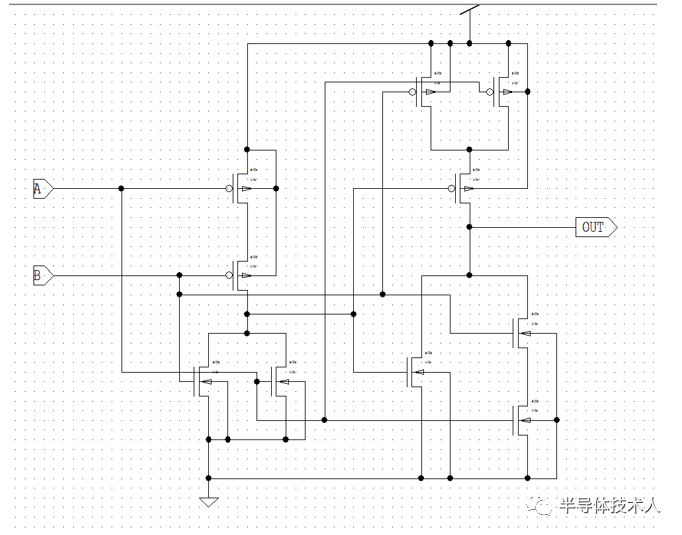

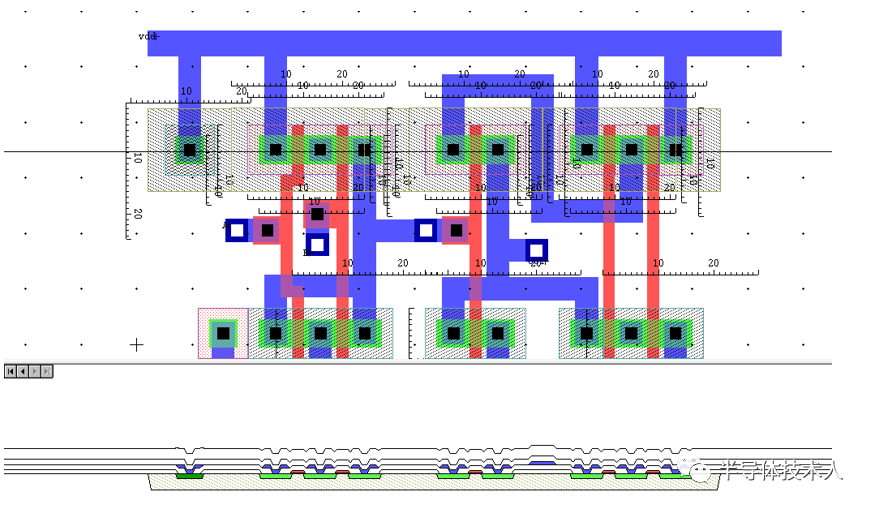

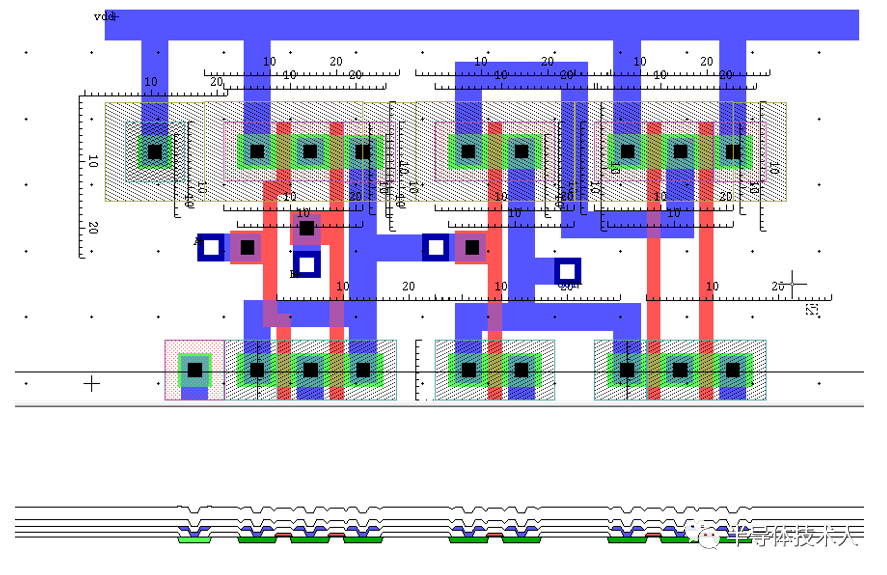

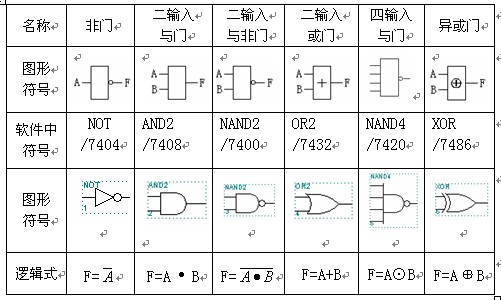

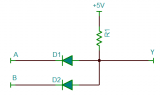

1、用CMOS傳輸門實(shí)現(xiàn)一個(gè)異或門電路。

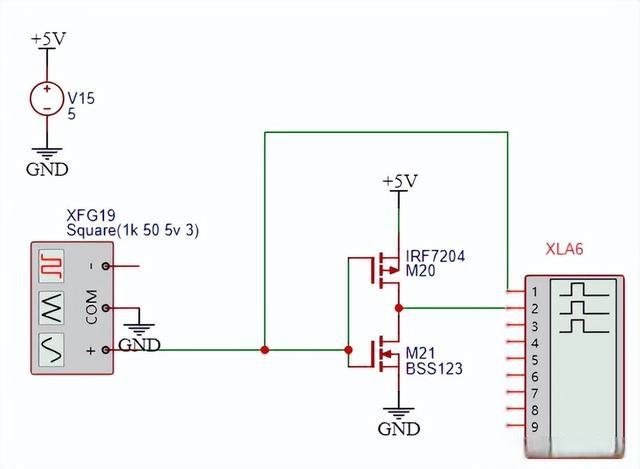

(1)

(2)

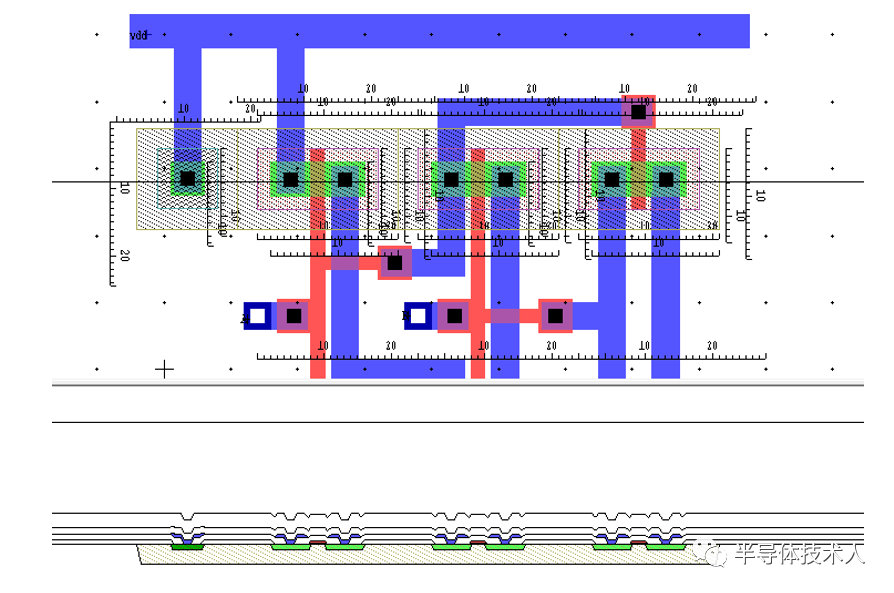

2、用CMOS傳輸門實(shí)現(xiàn)一個(gè)雙路開關(guān)電路,在電路上標(biāo)明輸入端和輸出端,并寫出輸出的邏輯表達(dá)式。

3、說明采用CMOS傳輸門比采用單獨(dú)的PMOS管或NMOS管的優(yōu)勢(shì)是什么?

利用PMOS管對(duì)高電平的傳輸性能好,而NMOS管對(duì)低電平的傳輸性能好,從而使信號(hào)可以獲得全擺幅的傳送而沒有電平損失。

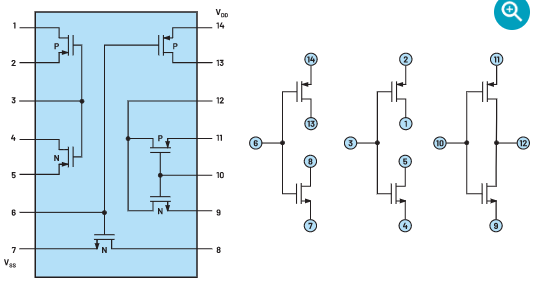

CMOS傳輸門:

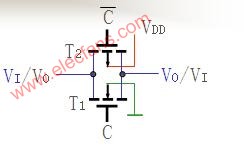

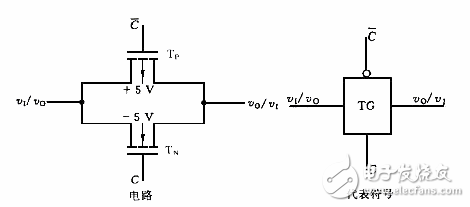

CMOS傳輸門(Transmission Gate)是一種既可以傳送數(shù)字信號(hào)又可以傳輸模擬信號(hào)的可控開關(guān)電路。CMOS傳輸門由一個(gè)PMOS和一個(gè)NMOS管并聯(lián)構(gòu)成,其具有很低的導(dǎo)通電阻(幾百歐)和很高的截止電阻(大于10^9歐)。

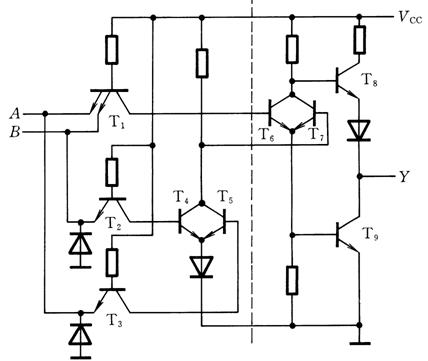

TP和TN是結(jié)構(gòu)對(duì)稱的器件,它們的漏極和源極是可互換的。設(shè)它們的開啟電壓|VT|=2V且輸入模擬信號(hào)的變化范圍為-5V到+5V。

為使襯底與漏源極之間的PN結(jié)任何時(shí)刻都不致正偏,故TP的襯底接+5V電壓,而TN的襯底接-5V電壓。兩管的柵極由互補(bǔ)的信號(hào)電壓(+5V和-5V)來控制,分別用C和!C表示。傳輸門的工作情況如下:當(dāng)C端接低電壓-5V時(shí)TN的柵壓即為-5V,vI取-5V到+5V范圍內(nèi)的任意值時(shí),TN不導(dǎo)通。同時(shí)、TP的柵壓為+5V,TP亦不導(dǎo)通。可見,當(dāng)C端接低電壓時(shí),開關(guān)是斷開的。

為使開關(guān)接通,可將C端接高電壓+5V。此時(shí)TN的柵壓為+5V,vI在-5V到+3V的范圍內(nèi),TN導(dǎo)通。同時(shí)TP的棚壓為-5V,vI在-3V到+5V的范圍內(nèi)TP將導(dǎo)通。由上分析可知,當(dāng)vI<-3V時(shí),僅有TN導(dǎo)通,而當(dāng)vI>+3V時(shí),僅有TP導(dǎo)通當(dāng)vI在-3V到+3V的范圍內(nèi),TN和TP兩管均導(dǎo)通。

進(jìn)一步分析還可看到,一管導(dǎo)通的程度愈深,另一管的導(dǎo)通程度則相應(yīng)地減小。當(dāng)一管的導(dǎo)通電阻減小,則另一管的導(dǎo)通電阻就增加。由于兩管系并聯(lián)運(yùn)行,可近似地認(rèn)為開關(guān)的導(dǎo)通電阻近似為一常數(shù)。

-

CMOS

+關(guān)注

關(guān)注

58文章

5735瀏覽量

236090 -

門電路

+關(guān)注

關(guān)注

7文章

199瀏覽量

40260 -

模擬器

+關(guān)注

關(guān)注

2文章

881瀏覽量

43419 -

NMOS管

+關(guān)注

關(guān)注

2文章

121瀏覽量

5534 -

PMOS管

+關(guān)注

關(guān)注

0文章

83瀏覽量

6723

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

電子技術(shù)--門電路與邏輯代數(shù)

邏輯門電路的概念 幾種常見門電路的實(shí)現(xiàn)

CMOS邏輯電路、傳輸門XOR

用CMOS傳輸門實(shí)現(xiàn)一個(gè)異或門電路

用CMOS傳輸門實(shí)現(xiàn)一個(gè)異或門電路

評(píng)論