本文將詳細介紹輸出延時(output delay)的概念、場景分類、約束參數獲取方法以及約束方法。

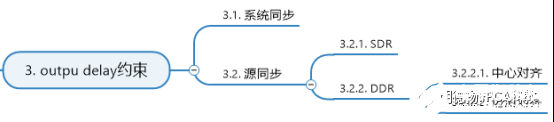

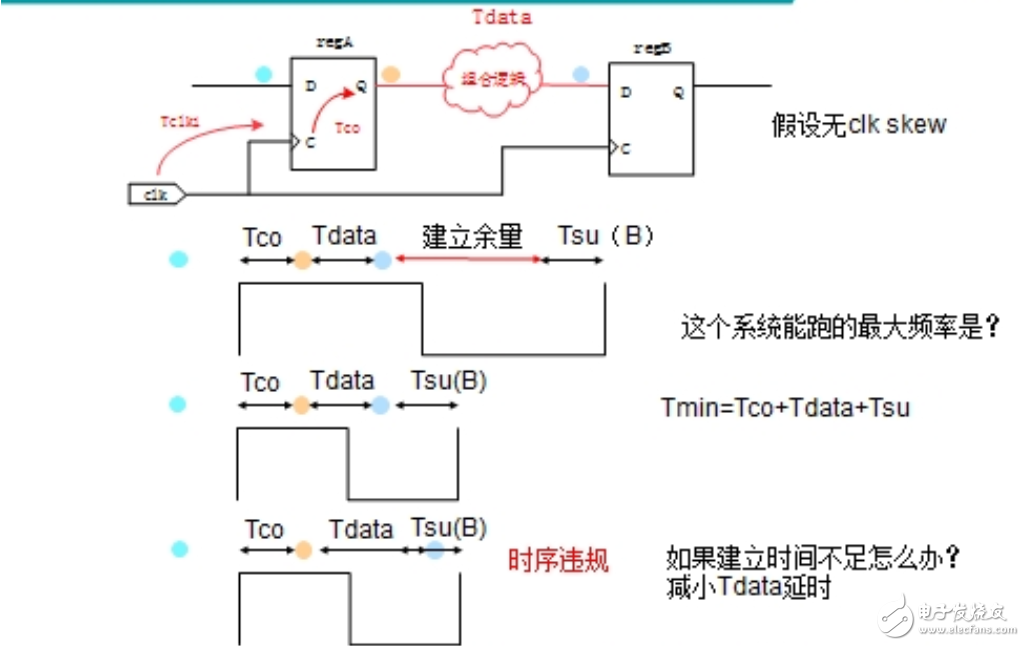

圖1 output delay約束類型

如上圖1所示:輸出延時(output delay)約束與輸入延時(input delay)約束相似,輸出延時亦分成系統同步和源同步兩大情形。

其中源同步根據時鐘特性,又可以細分成SDR和DDR兩種情況。根據數據和時鐘的相位關系,DDR可以分成中心對齊和邊沿兩種。本文將詳細討論各種情況下的約束方法。

第1節 輸出延時約束的目的

在詳細討論輸出延時約束之前,明確為什么要做輸出延時約束,通過該約束可以解決什么問題?

第2節 輸出延時概念

設置輸出延時的目標:讓FPGA調整自身輸出的時序,使輸出的時序滿足下游器件寄存器的建立時間和保持時間要求,來使得下游器件能夠正確的捕獲數據。

2.1 輸出延時的max與min

2.1.1 max

max的意思是最大延時時間,用于考慮建立時間:一般為正數,表示數據在時鐘采樣沿之前就到達。

最大延時時間公式:最大板級延時+TSU。TSU為下游器件要求的建立時間。假如板級延時為0,則max就是下游器件的“TSU”。

2.1.2 min

min的意思為最小延時時間,用于考慮保持時間:一般為負數,表示數據在時鐘采樣沿之后還保持了一段時間 。

公式:最小板級延時-TH。TH為下游器件要求的保持時間。假如板級延時為0,min則是下游器件的“-Th”。

第3節 輸出延時的兩種測量方法

3.1 下游器件的參數(推薦)

第一種是根據下游器件的參數來設置建立時間和保持時間,通過下游器件的數據手冊,可以得知下游器件寄存器的建立時間和保持時間的要求。在得知下游器件的建立時間和保持時間之后,就可以進行相應的設置,從而實現時序約束。

3.2 示波器測量

第二種方法是用示波器測量下游器件的一個輸入端口,來得到它的時序信息。 比如說它的延時這種信息。但這種方法一般不常用。本書推薦使用第一種方法,因為第二種方法要求硬件做的比較規范,不能出現延時不斷抖動的情況。

第4節 各應用場景下的約束方法

接下來討論各種不同情況下輸出接口的時序約束方式。

4.1 系統同步

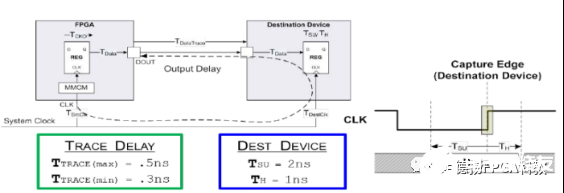

如圖2所示,系統同步就是FPGA和下游器件共用一個時鐘,可以認為這個時鐘的延時等于零。但實際上,FPGA把數據送給下游器件,是有一定延時的。

一般下游器件的寄存器會有一個建立時間和保持時間參數。可以從數據手冊中得到下游器件相應的參數,比如說它的建立時間是2ns,保持時間是1ns。而FPGA的延時可能符合一個抖動的情況,通過示波器測量或者計算方式可以得到FPGA的板級延時。比如說它的板級延時最大是0.5ns,板級延時最小是0.3ns。

圖2 系統同步接口示意圖

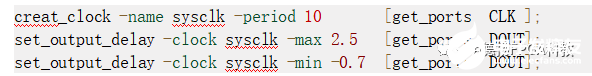

當測量得到板級延時之后,下一步便可以進行配置了。比如說最大的輸出延時為最大的板級延時加上建立時間要求,即2ns+0.5ns=2.5ns。最小板級延時為輸出最小延遲時間減去下游芯片寄存器保持時間,即0.3ns–1ns=-0.7ns。使用TCL語句實現以上約束的代碼如下所示:

上面約束語句首先是通過creat_clock創建了一個生成時鐘,輸出給下游芯片作為時鐘信號(需要注意該信號本身是存在的,只是通過創建生成時鐘的方式告知quartus、vivado等綜合軟件該信號是時鐘信號)。然后,set_output_delay –clock sysclk -max 2.5 [get_ports DOUT]的含義就是輸出信號DOUT相對生成時鐘sysclk的最大延遲是2.5ns。而set_output_delay –clock sysclk -min -0.7 [get_ports DOUT] 的含義就是輸出信號DOUT相對生成時鐘sysclk的最小延遲是-0.7ns。

這是系統同步的情況,系統同步就是FPGA和下游器件共用一個時鐘信號。

4.2 源同步SDR

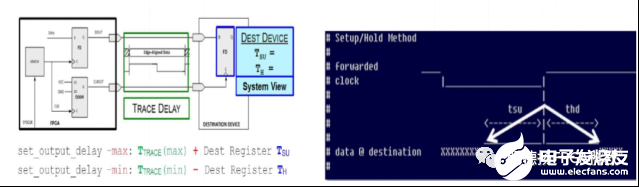

接下來看一下源同步,如圖3所示,FPGA輸出數據給下游器件同時,也會與數據同步輸出一個時鐘信號給下游器件,時鐘和數據一起傳輸。其中分為SDR和DDR。SDR是指使用時鐘上升沿去采樣數據,DDR是指上升沿和下降沿都去采樣數據。

圖3 SDR傳輸示意圖

上圖3為典型的SDR傳輸示意圖,SDR使用上升沿對數據進行采樣。SDR的原理、方法與系統同步都是一樣的,也是通過查數據手冊得到下游器件寄存器的建立時間、保持時間。它保持的要求也能知道我的這個延時的抖動是多少啊。在測量之后得到最大抖動和最小抖動,就能根據公式計算出最大延遲時間和最小延遲時間。根據公式,最大延時時間是指板級傳輸延時最大值加上下游器件建立時間要求,而最小延遲是指板級傳輸延遲最小值減去下游器件保持時間。

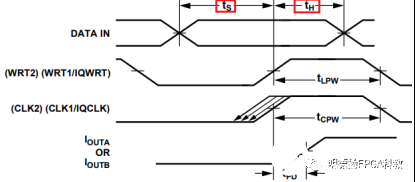

MP801開發板提供了兩路高速DAC,AD9709時鐘頻率最高支持125MHz,輸出也是符合SDR要求的,通過閱讀手冊獲取該芯片寄存器的建立時間和保持時間。如下圖4是AD9709芯片的接口時序圖,CLK2是時鐘信號,WRT2是類似寫使能的信號,一般與時鐘CLK保持一致即可,DATA IN是FPGA個AD9709芯片的八位數字信號,而IOUTA OR IOUTB是DAC芯片的兩路模擬輸出信號,與本次時序分析無關。建立時間是指數據必須在時鐘上升沿之前到達的一段時間,所以下圖中ts就是AD9709接口寄存器建立時間。保持時間是指數據必須在時鐘上升沿之后保持的一段時間,所以下圖中tH就是AD9709接口寄存器的保持時間。

圖4 AD9709接口時序圖

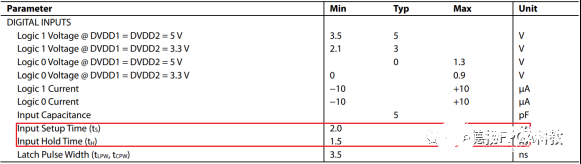

在根據芯片手冊的數據表查的上圖4中對應的時間,如下圖5所示,tS的最小值為2.0ns,故建立時間為2.0ns,保持時間tH為1.5ns。能夠對概念理解,不管是什么芯片都可以根據芯片手冊的接口時序圖得知接口寄存器的建立時間和保持時間,后續時序約束可以直接使用該參數。

圖5 AD9709芯片時間參數

4.3 源同步-DDR(查手冊方法)

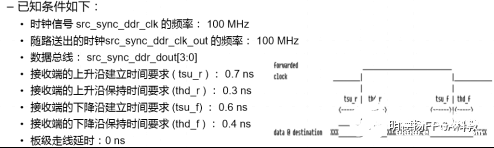

DDR其實就是SDRAM的升級版,為了提高數據傳輸效率,DDR在時鐘的上升沿和下降沿都對數據采樣。同樣可以查手冊得到接口寄存器的建立時間、保持時間,由于在時鐘上升沿和下降沿都在采集數據,在這兩個邊沿都會存在建立時間和保持時間的要求,例如:

圖6 DDR接口示意圖

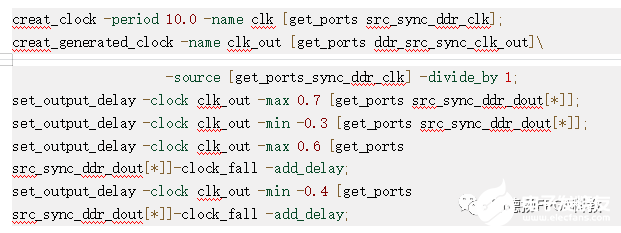

如上圖6要求上升沿建立時間tsu_r為0.7ns,上升沿的保持時間thd_r為0.3ns,下降沿的建立時間tsu_f為0.6ns,下降沿的保持時間thd_f為0.4ns。進行IO約束之前,一般都會先約束一個生成時鐘,目的在于告訴綜合軟件該接口信號以哪個時鐘信號為標準,便于后續約束直接使用。根據理論知識,如果時鐘線與數據信號線的PCB走線做了等長處理,那么源同步的最大延遲為下游器件的建立時間,最小延遲為0減去下游器件的保持時間。所以該DDR上升沿最大延遲0.7ns,最小延遲為0-0.3ns=0.3ns,下降沿最大延遲0.6ns,最小延遲是-0.4ns。上述約束轉換成TCL代碼如下所示:

注意這個clock_for下降沿的時候,要加上-add_delay。上面的六句約束中的前面兩句時鐘約束不是一定存在的,這兩句與前面的時鐘約束方式是一樣的,后面四句set_output_delay用于約束輸出接口信號所對應的最大和最小輸出延遲,帶有clock for的表示以時鐘的下降沿作為參考點,從而完成對DDR輸出接口信號的約束。

有的讀者會注意到input delay 有個什么叫中心對齊的,為什么這里就沒有了?因為 input delay 是靠測量的方式去得到的,而output delay是查數據手冊的方式獲得的數據。那么他的邊緣這個點的時候,就不不可能會抖動。在下降沿的時候,在之前會穩定,穩定多久,之后會穩定多久,因此他一定是這么穩這樣一個情況的啊,他會把這個實際參數要求給你啊,所以沒有什么邊緣對齊和中心對齊的情況。我們從查數據手冊就會查到這幾個參數,然后進行配置就可以了啊。還有一點就是對于我們的板級延時的一般情況下呢,如果我們硬件做的好的板,這件事是不需要考慮的。也就是說我們的output delay 一般呢就是設置它的鑒定時間啊,就是從手冊里面得到它鑒定時間和保質時間這兩個參數。然后根據它公式直接就是配置就可以了啊,所以它output delay 的方式相對比較簡單。

第5節 總結與建議

根據經驗,按照順序去索引,找到對應的情況,按要求進行約束。比如說這個端口是屬于上面三種情況中的哪一種,就按照那一種進行配置,進行約束就可以了。

input delay 、output delay就是告訴綜合工具現在的實際情況。告訴綜合軟件FPGA下游器件的情況、要求是什么,綜合軟件得知這些參數后,結合自身的參數,在對設計進行布局、布線時就會去考慮滿足下游器件的建立時間和保持時間要求。如果延遲時間過長,可以通過減小內部走線的延遲,或者采用更加接近芯片管腳的觸發器去實現設計,減小輸出延遲來達到目的。如果延遲過短導致下游器件保持時間不滿足,綜合軟件可以通過增加走線延遲等增大輸出延遲時間的方式滿足下游器件保持時間的要求。總之,只要添加合理的約束,告知綜合軟件下游器件的延遲要求,綜合軟件就可以通過調節內部觸發器的布局、走線來滿足下游器件的建立時間和保持時間的要求,從而達到約束的目的。這就是 output delay 一個配置方式,相對比較簡單。

審核編輯:湯梓紅

-

dac

+關注

關注

43文章

2309瀏覽量

191569 -

時鐘

+關注

關注

11文章

1747瀏覽量

131802 -

時序約束

+關注

關注

1文章

115瀏覽量

13458

發布評論請先 登錄

相關推薦

VIVADO時序約束及STA基礎

FPGA時序約束之衍生時鐘約束和時鐘分組約束

FPGA時序約束分析余量

詳解FPGA的時序input delay約束

set_output_delay的本質是什么?淺談set_ouput_delay時序

時序約束連載01~output delay約束

時序約束連載01~output delay約束

評論