簡介:介紹S3C4510B型ARM微處理器和基于該處理器設計的最小系統,概述該系統外圍應用電路的選型,以便使用者自行設計開發。

ARM(Advanced RISC Machines),既可以認為它是一個公司的名字,也可以認為它是一類微處理器的統稱,還可以認為它是一種技術名稱,習慣上稱之為"高級精簡指令集計算機機器公司"。目前,各種各樣ARM微處理器的設備應用數量已經遠遠超過了通用計算機。在工業和服務領域中,使用ARM微處理器的數字機床、智能工具、工業機器人、服務機器人正在逐漸改變著傳統的工業生產和服務方式。因此,基于ARM微處理器的開發應用正成為數據時代的應用技術潮流。本文介紹S3C4510B型ARM微處理器最小系統的構建,并給出系統外圍相關器件的選型。

2 S3C4510B

S3C4510B是韓國三星公司(Samsung)基于以太網應用系統的高性價比16/32位RISC微處理器,內含1個由ARM公司設計的低功耗、高性能16/32位ARM7TDMI型RISC處理器核,最適合用于對價格和功耗敏感的應用領域。

S3C4510B的工作電壓為3.3V,總高主頻為50MHz,采用208引腳QFP封裝。其外部數據總線(雙向、32位)支持外部8、16位、32位的數據寬度;22位的地址總線可尋址每一個ROM/SRAM組、FLASH存儲器組、DRAM組和外部I/O組4M字(16M字節)的地址范圍。該微處理器內建37個32位的寄存器(31個通用寄存器和6個狀態寄存器),在某一時刻寄存器能否訪問由處理器的當前工作狀態和操作模式決定。單個S3C4510B具有的片內外圍功能模塊包括1個帶總線請求/應答引腳的外部總線控制器;1個32位系統總線仲裁器;1個可配置為內部SRAM的一體化指令/數據Cache(8KB);1個僅支持主控模式的ⅡC接口;1個Ethernet控制器;2個帶緩沖描述符的HDLC(高層數據鏈路控制)通道;1個DMA控制器;2個可工作于DMA方式或中斷方式的UART模塊;2個可編程32位定時器;18個可編程I/O口;1個含有21個中斷源的中斷控制器和1個PLL電路。

3 硬件設計

3.1 最小系統設計

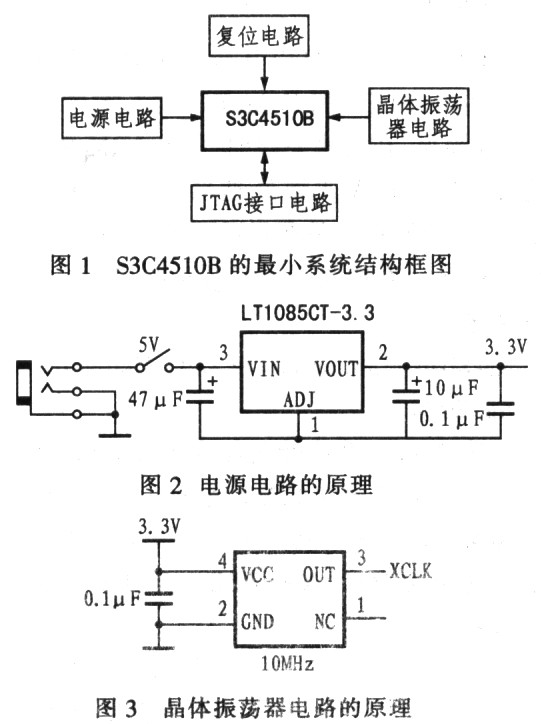

最小系統是由保證微處理器可靠工作所必須的基本電路組成的。S3C4510B的最小系統由S3C4510B、電源電路、晶體振蕩器電路、復位電路和JTAG接口電路組成。它們的連接關系如圖1所示。

3.1.1 電源電路

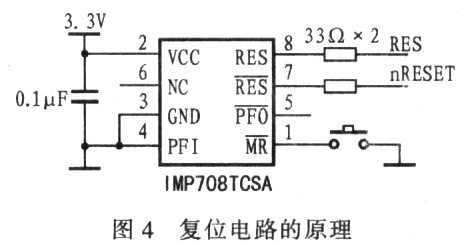

在系統中,S3C4510B及部分外圍器件需3.3V電源,另外,部分器件需要5V電源,為簡化系統電源電路的設計,要求整個系統的輸入電壓為5V直流穩壓電源。為了得到可靠的3.3V電壓,此處選用Linear Technology公司生產的LT1085CT-3.3型DC-DC變換器,它的輸入電壓為5V,輸出電壓為3.3V,輸出電流可達3A。電源電路如圖2所示。

3.1.2 晶體振蕩器電路

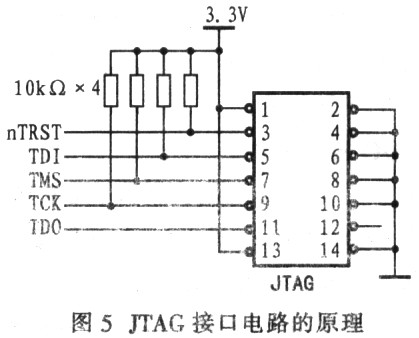

該電路用于向S3C4510B和其他電路提供工作時鐘。鑒于有源晶體振蕩器在工作可靠性和精度上都要優于無源晶體振蕩器,故在系統中使用了有源晶體振蕩器。根據S3C4510B的最高工作頻率及PLL電路的工作方式,選擇10MHz的有源晶體振蕩器,其頻率經過S3C4510B內部PLL電路倍頻后,最高可達50MHz。內部PLL電路兼有頻率放大和信號提純的功能,因此,系統可以以較低的外部時鐘信號獲得較高的工作頻率。晶體振蕩器電路如圖3所示。

3.1.3 復位電路

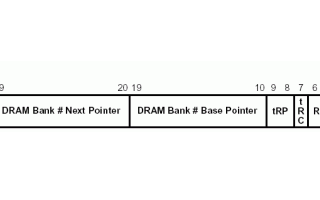

該電路主要完成系統的上電復位和系統運行時用戶的按鍵復位功能,有助于用戶調試程序。此處選用IMP公司生產的IMP708TCSA型復位電路,它的工作電壓為3.3V,具有1個手動復位輸入引腳和2個復位輸出引腳(高電平有效引腳和低電平有效引腳各1個),可以滿足不同復位信號的要求。復位電路如圖4所示。

3.1.4 JTAG接口電路

JTAG(Joint Test Action Group-聯合測試行動小組)是一種國際標準測試協議,主要用于芯片內部測試及對系統進行仿真、調試,JTAG技術是一種嵌入式測試技術。通過JTAG接口可對芯片內部的所有部件進行訪問,是開發調試嵌入式系統的一種簡潔高效的手段。它有2種連接標準,即14針接口和20針接口。此處選擇14針接口的標準。JTAG接口電路如圖5所示。

在設計完以上4部分電路后,S3C4510B就具有安全和可靠工作的基本條件。

3.2 外圍引出接口設計

最小系統的設計是為更好地研究開發微處理器服務的,因此,還應將微處理器的一些必要引腳用接口插座引出,方便實驗開發使用。下面將以模塊為單元介紹典型的需要引出的引腳,并給出相應電路的選型。

3.2.1 FLASH存儲器模塊

所需引腳為ADDR[21:0]、XDATA[31:0]、nRCS0、nOE、nWBE0、nRESFT。推薦電路為INTEL公司生產的TE28F320B,其存儲容量為32M位(4M字節),工作電壓為2.7V-3.6V,采用48腳TSOP封裝或48腳FBGA封裝,16位數據寬度。

3.2.2 SDRAM模塊

所需引腳為ADDR[21:0]、XDATA[31:0]、nSDCS0、nDWE、nSDRAS、nSDCAS、nWBE0、nWBE1、SDCLK、CKE。推薦電路為Winbond公司的W986416DH,其存儲容量為4組×16M位(8M字節),工作電壓為3.3V,常見封裝為54腳TSOP,兼容LVTTL接口,支持自動刷新和自刷新,16位數據寬度。

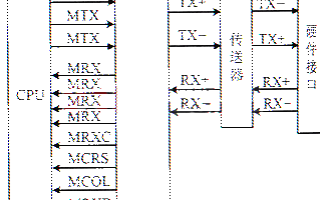

3.2.3 以太網接口模塊

所需引腳為TX_ERR、TXD[3:0]、TX_EN、TX_CLK、RX_ERR、RXD[3:0]、RX_CLK、RX_DV、RX_ERR、nRESET、CRS、COL。推薦接口電路為Davicom公司生產的DM9161,它是單口高速以太網物理層接口電路,可提供MII接口和傳統7線制網絡接口,工作電壓為3.3V。

3.2.4 I2C接口模塊

所需引腳為SCL、SDA。此處外擴1個Atmel公司生產的AT24C01作為I2C接口模塊的存儲器,其工作電壓為5V,可提供128字節的EEPROM存儲空間,用于存放少量在系統掉電時需要保存的數據。

3.2.5 實時時鐘模塊

所需引腳為E_ADDR3、SCL、SDA。Philips公司生產的PCF8583是一種低功耗CMOS實時時鐘/日歷接口電路,工作電壓為3.3V,內置256字節的SRAM,通過I2C接口與外部進行數據通信,每次讀、寫操作完成后,內置的地址寄存器會自動增加。

3.2.6 ADC模塊

所需引腳為E_ADDR0、E_ADDR1、E_ADDR2、E_nWBE0、E_nOE、nADC_CS,ADC_CLK。National公司生產的ADC0809是一種8位8通道逐次逼近式A/D轉換器,工作電壓為5V,具有高速、高精度、溫度依賴性小和功耗低等特點。

3.2.7 DAC模塊

所需引腳為E_D[7:0]、nDAC_CS。National公司生產的DAC0832是8位CMOS D/A轉換器,工作電壓為5V,由8位輸入寄存器、8位DAC寄存器、8位D/A轉換器和轉換控制電路組成,2級寄存器使它能夠實現多路D/A的同步轉換輸出。

3.2.8 通用I/O接口模塊

引腳P0-P3可外接跳線選擇高、低電平用作狀態輸入或其他輸入功能;引腳P4-P7可外接LED,用作程序運行狀態的顯示或其他輸出顯示。

以上僅列出了8種模塊所用到的引腳和電路,此外還有串行接口模塊、總線驅動模塊、譯碼模塊、LED/LCD顯示模塊、鍵盤模塊等,不再一一列舉。以上提到的E_xxx引腳均為經過總線驅動與電平轉換電路后的引腳,此類電路有TI公司的N74ALVC16245(雙8通道)、SN74LVC4245(通道)等。

4 硬件調試

系統上電后,電源電路的輸出電壓為DC3.3V;有源晶體振蕩器的輸出頻率為10MHz;復位電路的輸出端(以低電平有效引腳為例)在按鈕未按下時輸出為高電平,按下按鈕后為低電平,按鈕松開后輸出端恢復為高電平。

通過JTAG接口調試S3C4510B,上電前應檢查S3C4510B的引腳nEWAIT是否已上拉,引腳ExtMREQ是否已下拉,對這2個引腳的處理關系到S3C4510B能否正常工作,必須非常注意。上電后,如果在使能片內PLL電路的情況下,引腳MCLKO/SDCLK可輸出50MHz的波形,就說明S3C4510B已正常工作。此時,就可使用集成開發工具ADS或SDT通過JTAG接口對電路內的部件訪問和控制,如通過對電路內部控制通用I/O口的特殊功能寄存器的操作來點亮連接在P4-P7口上的LED,如果LED能夠按照寄存器的設置正常開關,那就說明所設計的最小系統是可靠的。

5 結束語

ARM微處理器將以其極好的性能和極低的功耗與高端的MIPS和PowerPC嵌入式微處理器抗衡。可以預見,在將來一段時間內,ARM微處理器仍將主宰32位嵌入式微處理器市場。學習和掌握ARB微處理器技術是非常必要的,而設計ARM微處理器是最小系統是一種學習該技術的極佳方法。

審核編輯:湯梓紅

-

mcu

+關注

關注

146文章

17317瀏覽量

352642 -

微處理器

+關注

關注

11文章

2274瀏覽量

82776 -

S3C4510B

+關注

關注

0文章

30瀏覽量

17450 -

最小系統

+關注

關注

9文章

252瀏覽量

29160

發布評論請先 登錄

相關推薦

基于S3C4510B微處理器和uClinux實現存儲系統的設計

基于S3C4510B的串口網絡服務器最小系統

μClinux在S3C4510B上的移植

基于ARM型微處理器的最小系統設計

s3c4510b中文手冊,s3c4510b用戶手冊

s3c4510b中文資料

μClinux在S3C4510B上的移植

基于S3C4510B的存儲系統原理與設計

基于S3C4510B的HDLC協議實現

三星ARM處理器S3C4510B的HDLC通道使用及編程

基于S3C4510B微處理器和操作系統實現網絡通信工程的編寫設計

基于S3C4510B型微處理器的最小系統設計

基于S3C4510B型微處理器的最小系統設計

評論