今天給大家分享的是:在電路設計和PCB設計如何防止ESD損壞設備。

在電子行業中,保護設備免受ESD損壞是必須要注意的。靜電放電(ESD)是一種非常高的電壓尖峰,很容易損壞集成電路和低功率半導體等小信號元件。

常見的ESD是由人體接觸電子設備引起的,電荷在人體內累積,然后當身體接觸到設備時,電荷就會放電,并伴隨著非常高的電壓尖峰。

下面介紹在PCB設計中如何減少ESD損害:

一、使用鉗位二極管

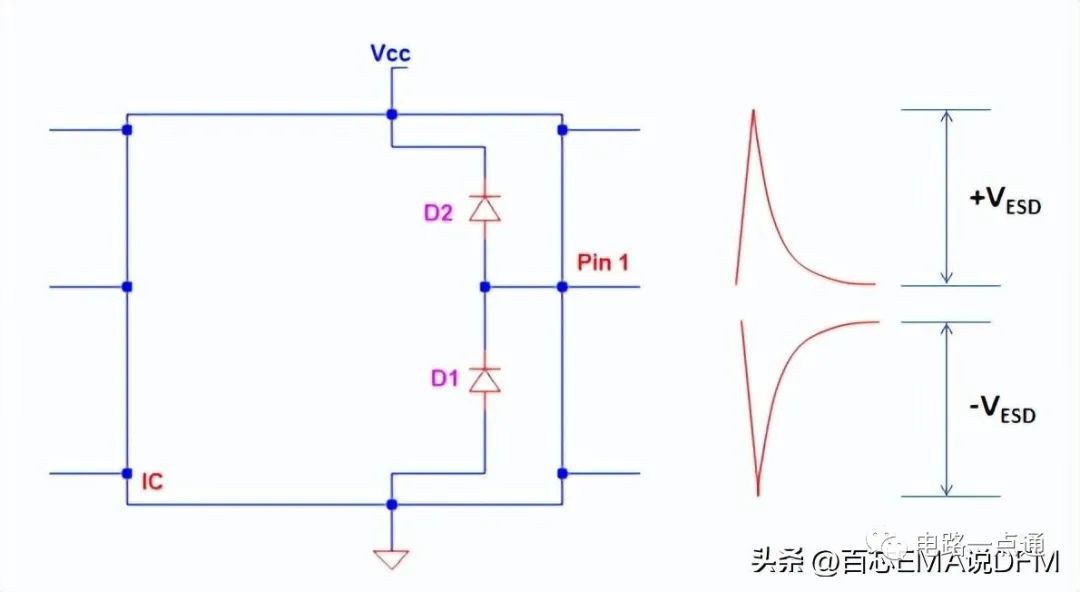

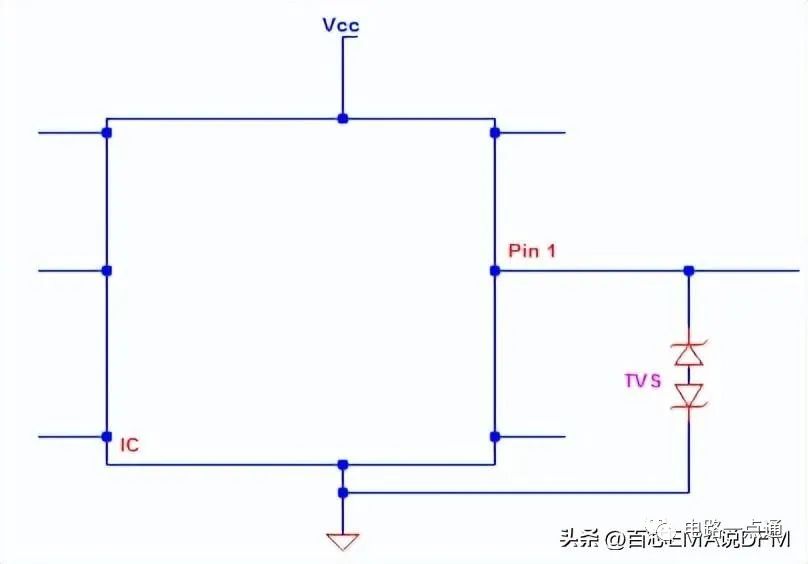

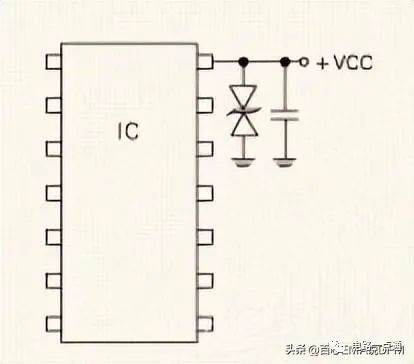

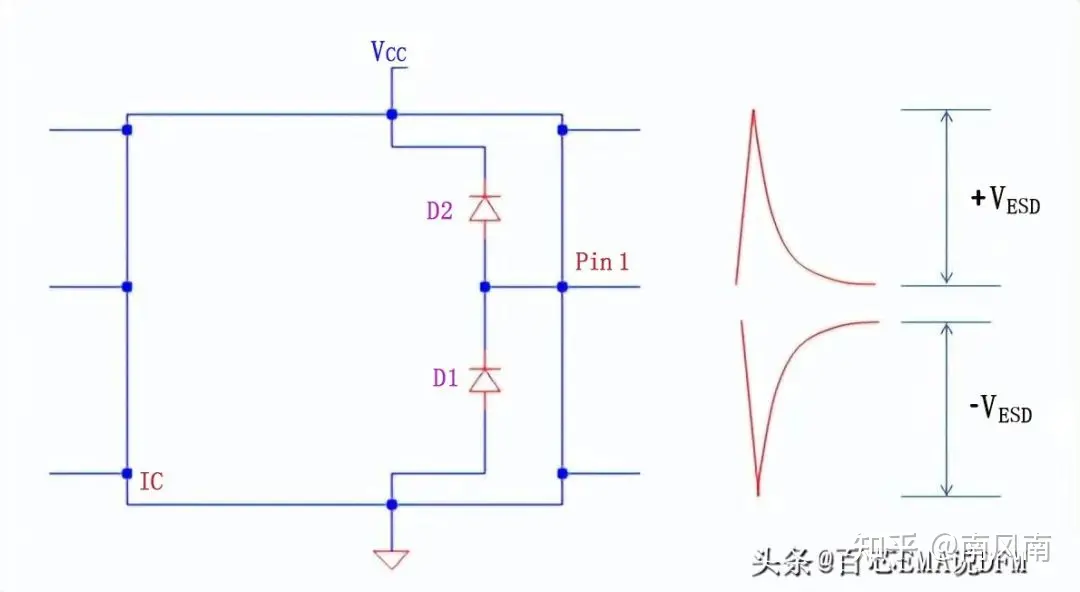

鉗位二極管最常用于集成電路中,以保護器件免受ESD的損壞。微控制器、數字信號控制器和處理器都具有內部的ESD鉗位二極管。但是在低成本控制器內部有時候會沒有鉗位二極管,這個時候就需要靠近在外部添加一個鉗位二極管。下圖是IC固有的ESD鉗位二極管。

IC固有的ESD鉗位二極管

正常工作時,假設引腳1的電壓預計在0-3.3V之間,D1和D2不會干擾。假設高電平為3.3V,則D1反偏不導通,另一方面D2也是不導通的,因為陰極連接到VCC,引腳的高電平等于VCC。當引腳1中的電壓為0時,D2反向偏置,D1無偏置。

當存在由ESD引起的高壓尖峰時,二極管會導通。例如:尖峰非常高,D2將正向偏置,尖峰將轉移到VCC,從而保護IC的內部組件。當存在非常高的負尖峰時,D1將傳導并將尖峰轉移到地面。

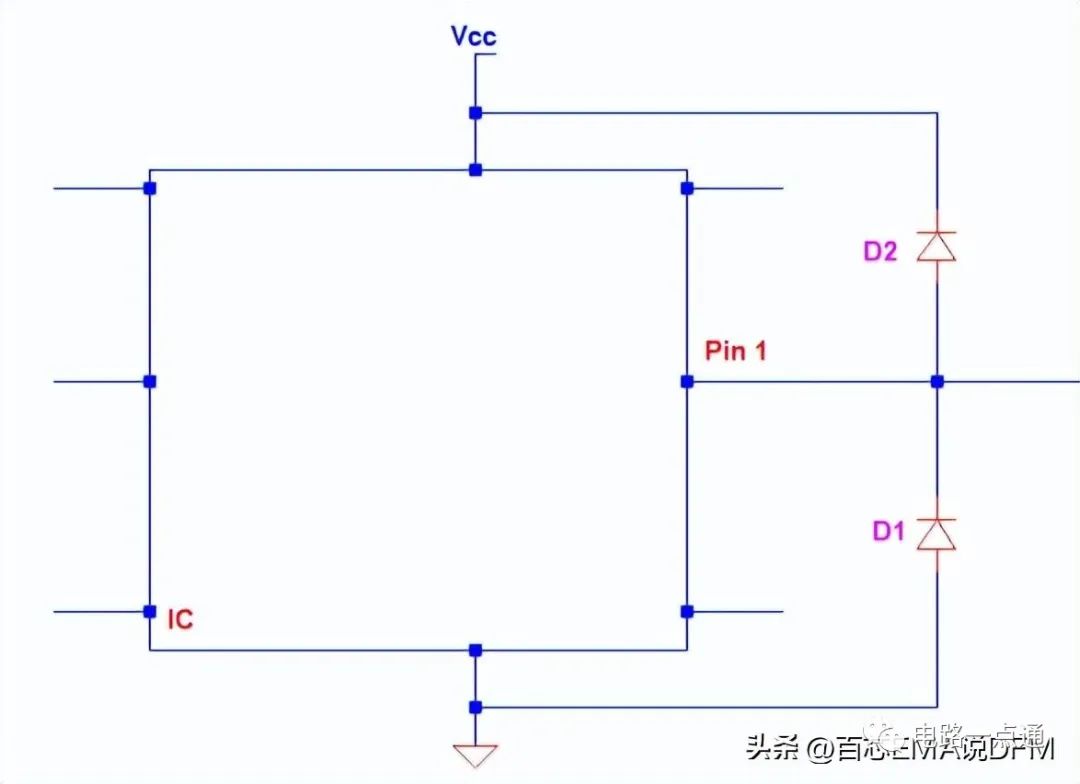

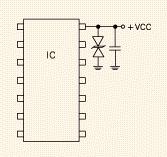

這里必須要了解清楚你使用的IC是否具有保護。如果沒有的話,就在外部添加鉗位二極管。如下圖所示:

在外部添加鉗位二極管

如果打算在IC的所有引腳中都添加鉗位二極管的話,那是肯定不行,而且成本也會很高。通常來說,在產品制造并放入外殼后,IC將不能再用,鉗位二極管需要實現的特性引腳比較少。當然鉗位二極管你可以用硅二極管或者肖特基二極管。

下面是通常需要鉗位二極管保護的最常見的引腳:

1、編程引腳

通常來說,編程引腳是供工程師使用的。有些產品需要在現場重新編程,編程引腳上發生ESD的可能性比較高。

在編程引腳上添加鉗位二極管的另一個原因是因為合規性,如果你是要銷售自己的產品,那就必須要遵守ESD標準。在ESD測試中,裸露的引腳是特意注入電壓尖峰,產品不能夠損壞。

2、重置引腳

一般來說,不會希望產品在沒有什么理由的情況下重置或者重啟,這個時候復位引腳可從外部訪問,當ESD發生時,設備可能會重啟啟動或者永久損壞。在浪涌等其他合規性測試期間,復位引腳可能會受到干擾,設備將重新啟動,這樣的情況不希望發生的。(雖然這不是ESD情況,但是由于浪涌電壓尖峰的電平非常高,也相當于模擬了ESD)

3、用于檢測線路電壓或者更高直流電壓的IC引腳

這些引腳實際上,從外部是沒有辦法訪問的,ESD在這些引腳上的可能性很小,然后再浪涌測試或者實際浪涌期間,這些引腳可能會遇到更高的尖峰電壓,而這些尖峰本質上就像ESD。根據經驗松開尖峰,就會容易損壞ESD。

二、使用瞬態電壓抑制器

瞬態電壓抑制器是快速作用的鉗位二極管,不是普通的PN二極管,例如上面的鉗位二極管。

TVS在作用和功能方面和鉗位二極管差不多。一旦達到其擊穿電壓,器件就會鉗位,否則為開路。

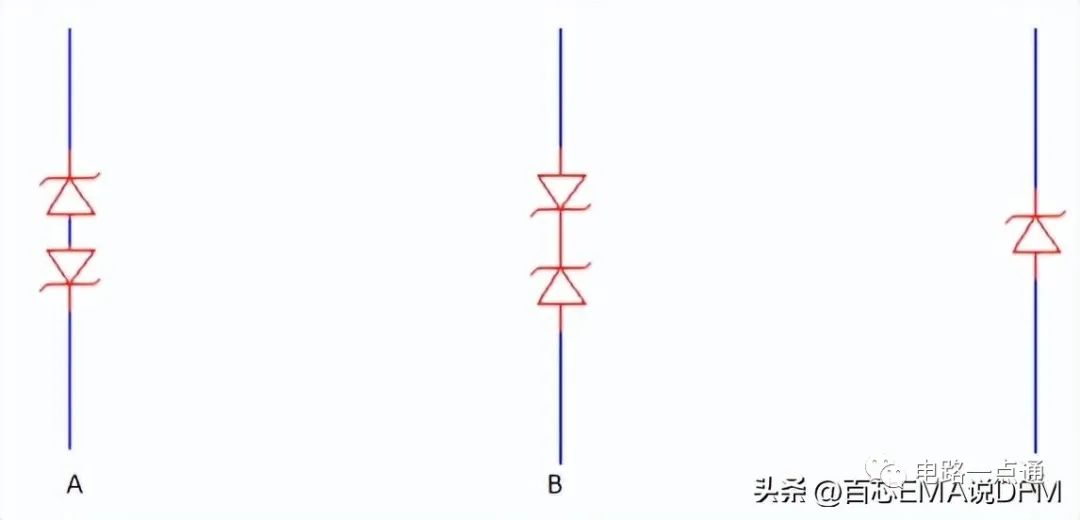

下圖顯示了常見的TVS符號,圖A、B為雙向TVS,C為單向TVS。雙向TVS可以阻止ESD正向或負向尖峰。另一方面,單向的只能抑制一個定向尖峰。

常見的TVS符號

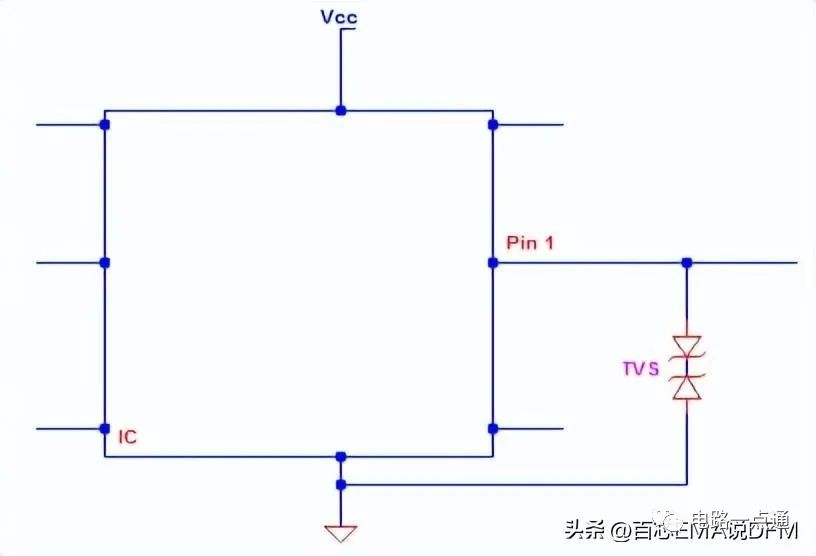

下面3個圖是使用TVS保護特定引腳免受ESD影響的示例連接。

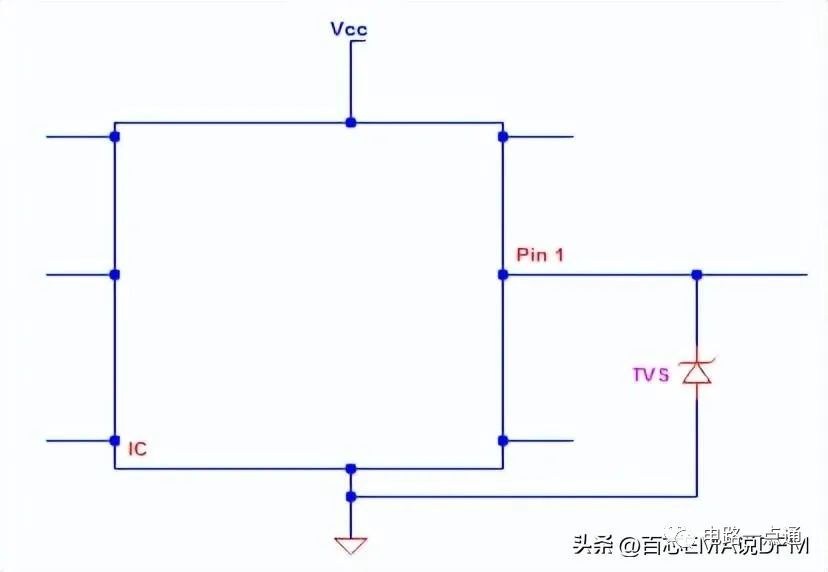

1、安裝在IC引腳的單向TVS

在電路正常工作時,TVS不導通。但存在正尖峰時,設備將鉗位,當存在負尖峰時,設備將正向偏置并將尖峰轉移到地面。

安裝在IC引腳的單向TVS

2、雙向TVS

在正常工作下,TVS不會產生干擾。在正電壓尖峰或負電壓尖峰期間,TVS將鉗位并保護IC.

雙向TVS

3、雙向 TVS

在正常工作下,TVS 不會產生干擾。在正電壓尖峰或負電壓尖峰期間,TVS將鉗位并保護 IC。

雙向 TVS

三、使用齊納二二極管

使用齊納二極管作為ESD保護與單向TVS原理相同,齊納二極管的缺點是不如TVS快,并且考慮到TVS相同的尺寸,只能處理較小的能量,需要更大的齊納二極管來承受能量,但是會占用PCB的空間,成本也會更高。

四、使用高頻電容

在汽車電路設計中,假定人體具有300PF的等效電容。該電容可以存儲高達8KV的電位,當人接觸任何東西時,體內的電荷就會放電。如果是小型電子設備,就會損壞。

下面的設置顯示了安裝在IC引腳中的電容如何受到ESD保護,當人體接觸到該引腳時,人體的電容與電容ESD形成并聯。正因為如此,人體內的8KV電位才會被抑制。

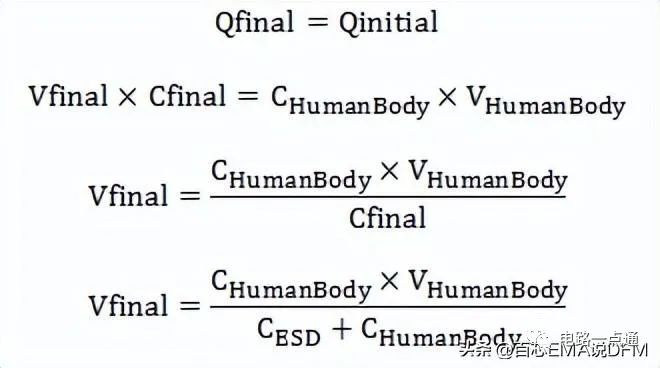

在電荷守恒中,最終電荷等于初始電荷,所以將人體視為初始電荷

當人體接觸帶有ESD的引腳時,發生充電。然后:

根據電荷守恒:Qinitial=Qfinal。Cfinal是CESD和人體電容的并聯組合。Ufinal 是電容器將承受的實際電壓。然后:

如上所述,V HumanBody為 8kV,C HumanBody為 330pF。假設我們將選擇 33nF CESD,那么最終電壓將為:

因此,在引腳上安裝33nfESD保護電容后,引腳所承受的電壓僅為79.2V,而不是8KV,而電容的額定電壓必須高于此值,如果要進一步降低電壓水平,只需要增加ESD電容即可。但是進一步增加電容也會增加PCB的尺寸。

以上就是4種防止ESD損壞設備的方法。你可以讓任意選擇,這4種方法在應用程序中有優點也有缺點,可以在實際測試中驗證是否真的有效。

PCB設計可以減少不必要的故障排除和返工成本,,下面是在PCB設計中如何防止ESD的措施。

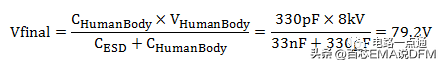

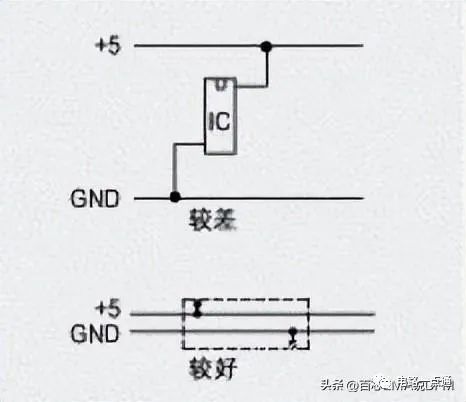

五、減少電路回路面積

電流被感應到閉合且具有變化的磁通量的電路回路中,電流的幅值與回路的面積成正比。也就是說,回路的面積必須減少,因為回路越大,磁通量越大。

減少電路回路面積

電流被感應到閉合且具有變化的磁通量的電路回路中,電流的幅值應與回路的面積成正比,也就是說,回路的面積必須減少,因為回路越大,磁通量越大,在電路中感應出的電流越強。

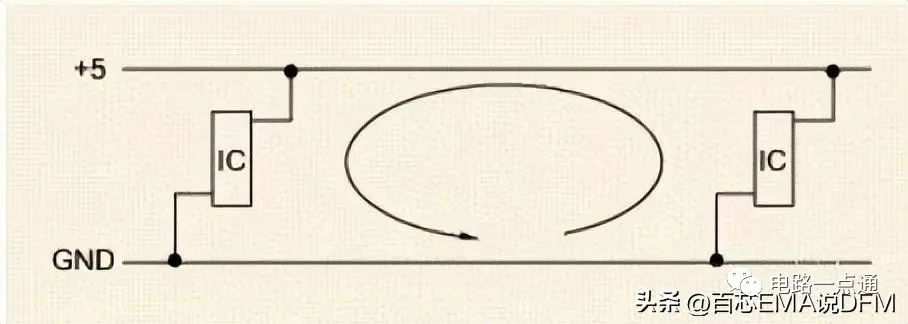

最常見的回路上圖所示,由電源和地之間的環路面積,還降低了ESD脈沖產生的高頻EMI電磁場。如果不能使用多層電路板,則電源和地線必須如下圖所示連接到一個網格上。

電源和地線連接到一個網格

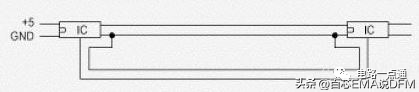

并網連接可以起到電源和地層的作用,各層印刷線路均與過孔相連,過孔之間的連接間距在每個方向上應在6cm以內。另外在布線時,電源和接地印制線盡量靠近也可以減少環路面積,如下所示:

電源和接地印制線盡量靠近也可以減少環路面積

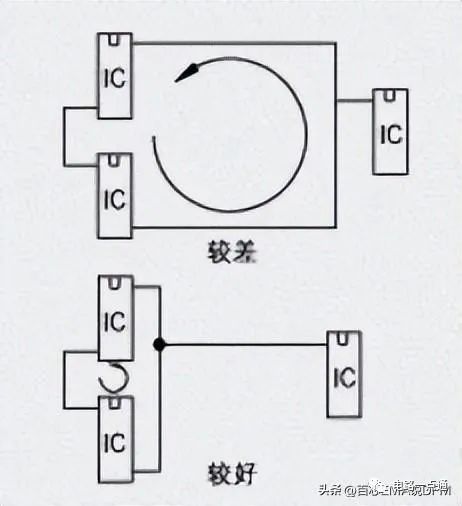

減少環路面積和感應電流的另與一種方法是減少互連設備之間的平行路徑,如下所示:

減少互連設備之間的平行路徑

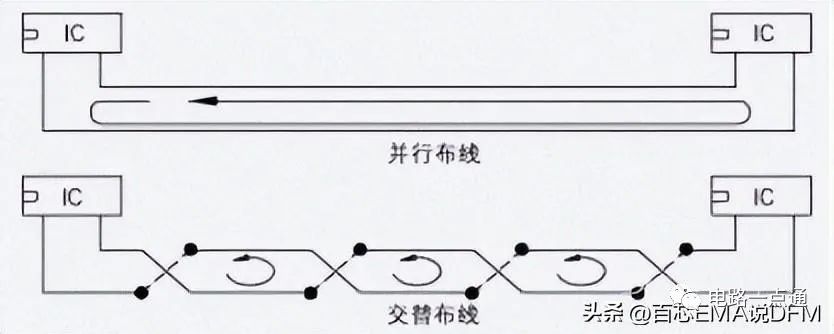

當必須使用超過30cm的信號連接線時,可以使用保護線,如下圖所示:

使用保護線

更好的一個方法時,在a保護線或者接地層13mm以內的信號線附近布設接地信號線,每個傳感器或者電源線的長信號線(>30cm)與接地線。

在保護線或者接地層13mm以內的信號線附近布設接地信號線

六、線的長度

長信號線也可以成為接收ESD脈沖能量的天線,使用較短的信號線會降低信號線作為天線接收ESD電磁場的效率,互連相鄰位置的設備以減少互連印刷線的長度。

七、減少電荷注入

ESD直接放電到接地層可能會破壞敏感電路。因此,在使用瞬態二極管時,最好在易損元件的電源和地之間防止一個或者多個高頻旁路電容。旁路電容減少電荷注入并保持源極和接地端口之間的電壓差。TVS分流感應電流,保持TVS鉗位間的電壓差。TVS和電容應盡可能靠近被保護的IC放置,以確保從TVS到地的路徑最短以及定然的長度,以減少寄生電容效應。

減少電荷注入

連接到必須安裝到PCB上的銅層,理想情況下,銅層必須與PCB接觸層隔離,并通過短導線連接到焊盤。

八、其他的措施

1、避免時鐘、復位信號等重要信號線在PCB邊緣;

2、將PCB不用的部分設置為地平面;

3、主機殼地線距離信號線至少4mm;

4、保持主殼地線的長寬比小于5:1,減少電感效應;

使用 TVS 二極管保護所有外部連接。

審核編輯:湯梓紅

-

二極管

+關注

關注

147文章

9702瀏覽量

167554 -

ESD

+關注

關注

49文章

2064瀏覽量

173375 -

半導體

+關注

關注

334文章

27703瀏覽量

222621 -

電路設計

+關注

關注

6677文章

2464瀏覽量

205333 -

PCB設計

+關注

關注

394文章

4698瀏覽量

86339

原文標題:電路設計和PCB設計如何防止ESD損壞設備

文章出處:【微信號:電路一點通,微信公眾號:電路一點通】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

PCB設計中如何減少ESD損害

PCB設計中如何減少ESD損害

評論