廣義的集成電路制造主要包括設計、制造和封裝(含測試)叁個方面。?

集成電路最初的設計方法是全手工設計,如手工畫因,人工刻制曝光用的多層掩模等。人工設計僅適用于小規模集成電路。20世紀70 年代,第一代集成電路。計算機輔助設計 (Integrated Circuit Computer Aided Design, ICCAD)系統問世。由于當時的計算機存儲量不夠大,運算速度也不夠快,因此 ICCAD 工具只能簡單處理版圖級設計問題。20 世紀 70 年代末,出現了份真和自動布局布線工具,提高了集成電路的設計效率。1983年,工作站(Workstation)在市場上鎖露頭角。有力地支持了 ICCAD 技術的發展,出現了第二代 ICCAD 系統,增加子邏輯級設計功能,20世紀90年代,ICCAD 系統進入第叁代 將行為級設計以硬件描述語言(Hardware Description Language, HDL) 的方式納入自動化設計的范疇。

進入21 世紀后,集成電路設計向可制造設計 (Design for Manufacturability,DFM)方向發展,其重要技術方向有軟硬件協同設計、衛 庫、低功耗設計、可靠性設計,以及系統芯片 (System on Chip, SoC)和系統級封裝 (Sxstem in Package, SiP)。??

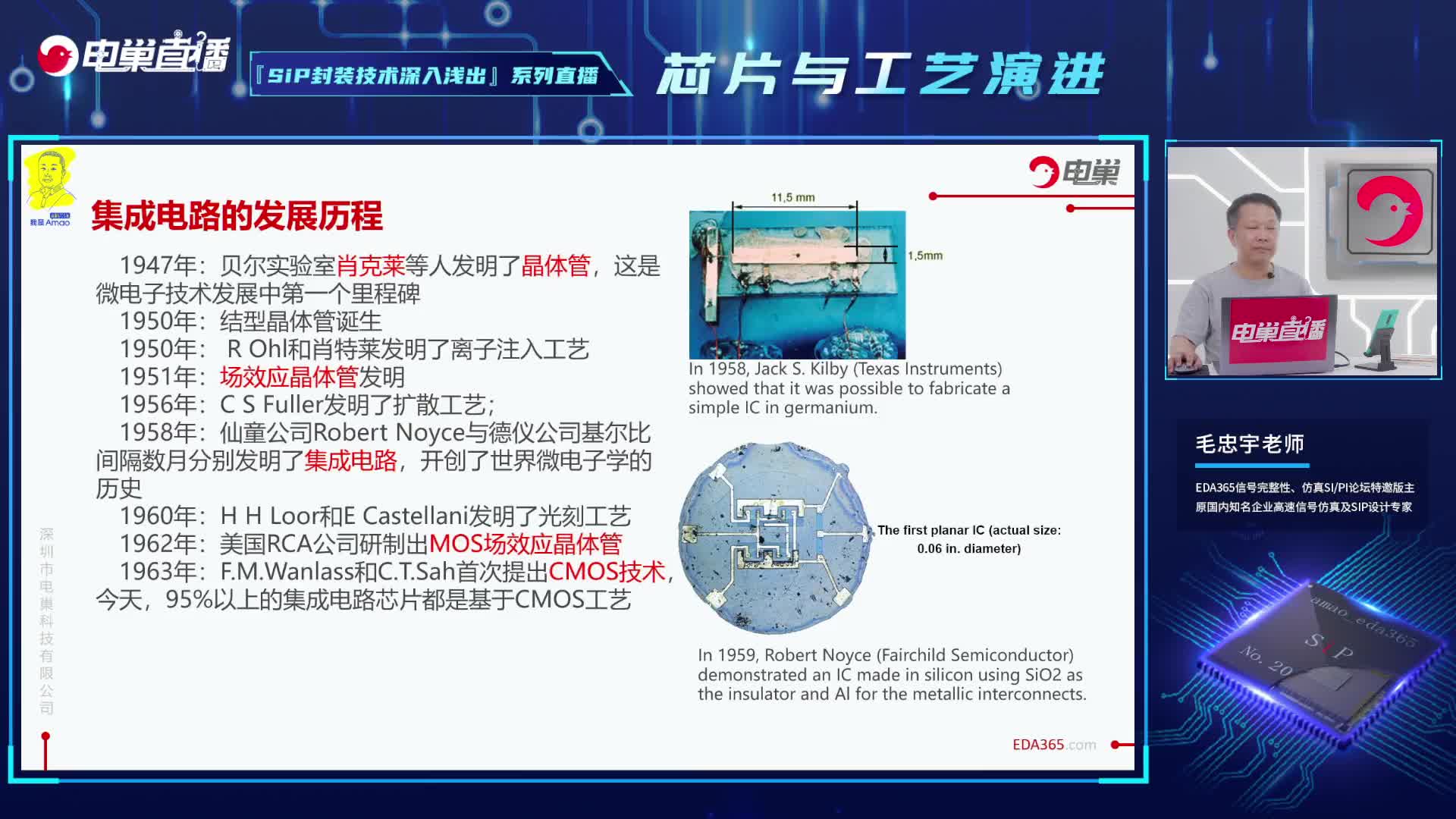

集成電路制造是一個在特定薄膜上制造特定圖形的過程。其中的氧化、外延、摻雜(擴散、離子注人)、沉積(物理氣相沉積、化學氣相沉積)等工藝為薄膜制造工藝,光刻(曝光和刻蝕)工藝為圖形制作工藝。

曝光和刻蝕是集成電路完成圖形制作的最核心工藝,縮小加工尺寸首先要減小曝光光源的波長。

20世紀 70年代中期以前,曝光光源為汞燈,永燈是一種多波長的光源,其波長范圍為 400~700nm。1982 年,曝光光源改進為紫外線 (Ulraviolet, UV)g線(波長為 436nm)和i線(波長為 365nm)。1994 年,曝光光源波長進人深紫外線(DUV)領域,主要為準分子激光 KrF(波長為 248nm)和 ArF(波長為 193nm)。

2003年12月,荷蘭 ASML (Advanced Semiconductor Material Lithography) 公司發布了全球首套商用浸沒式光刻 (Inmersion Lithogrephy) 設備,將純凈水充滿投影物

鏡最后一個透鏡的下表面與硅片之間,使得曝光光源的有效波長縮短,將 193mm 光刻延伸到 32nm CMOS 技術節點。此外,利用雙曝光/成像(Double Exposure/ Double Pattering)技術,將193nm 浸沒式光刻技術擴展到了 10n/ n 技術節點。

經過一定圖形曝光后的薄膜,還必須去除不需要的部分才能得到所希望的圖形,這就是刻蝕工藝。最初的刻蝕技術是濕法刻蝕,由于是各向同性腐蝕,所以對圖形尺寸的控制性較差。1980年以后,刻蝕技術進人干法刻蝕的時代,其中包括等離子刻蝕和反應離子刻蝕 (Reactive lon Etching, RIE),后者是當前主流的刻蝕技術。

當所有的晶體管通過薄膜技術和光刻技術在硅片上制作完成時,還必須采用互連技術將上百萬乃至數十億個晶體管按照所設計的規則連接起來才能形成真正的電路。最初的互連材料是鋁,研究表明,0.25μm 工藝(鋁導線,Sio?介質)的情況下,由互連產生的延遲已經超過門電路的延遲。1907 年,IBM 宣布推出了采用銅(電導率為59.6x10?S/m) 互連技術的芯片,這就是著名的鑲嵌工藝整機或系統是集成電路與最終消費者之問的界面,集成電路只有通過在整機或系統中的應用才能體現其價值;封裝是集成電路芯片與整機或系統的界面,只有經過封裝后的芯片才能裝人系統,并在系統中發揮應有的效用款動的套成電路封裝沿用丁晶休管外i (Transistor Ouuline, 10)封裝狂式。20世紀00年代中期,雙列直括封裝 (Double In-line Package, DIP)成為集成電路卦裝的主流。20世紀80年代,表面貼裝技術 (Sutace Mount Technology,SMT) 得到長足發展,出現丁多種封裝形式,如塑料有號線片式載體 ( Plastie Leaded Chip Camrier, PLCC) 封裝、塑料四面引線扁平封裝 (Plastic Quad Flat Package, POFP) 等。

20 世紀80年代至90年代,集成電路封裝引腳開始由周邊型向面陣型發展,如針概陣列 (Pin Grid Array,PGA)封裝。自20 世紀90年代的球柵陣列(Bar Grid Aray, BGA)封裝開始,封裝的 “插裝”概念被 “貼裝”所顛覆,“管腳”被“焊球”所替代。20 世紀末,芯片尺才封裝 (Chip Size Package, CSP)解決了芯片面積小而封裝面積大的矛盾,引1發了封裝技術的革命。今后集成電路封裝將向系統級封裝 (System in Package, SiP)的方向發展。3D 封裝中最重要的技術是硅通孔 (Through Silicon Vias, TSV),該技術基于 IBM 的 Merlin Smith 和 Emamuel Stem 于1964 年的發明專利,2010 年以后開始在集成電路封裝中得到應用。

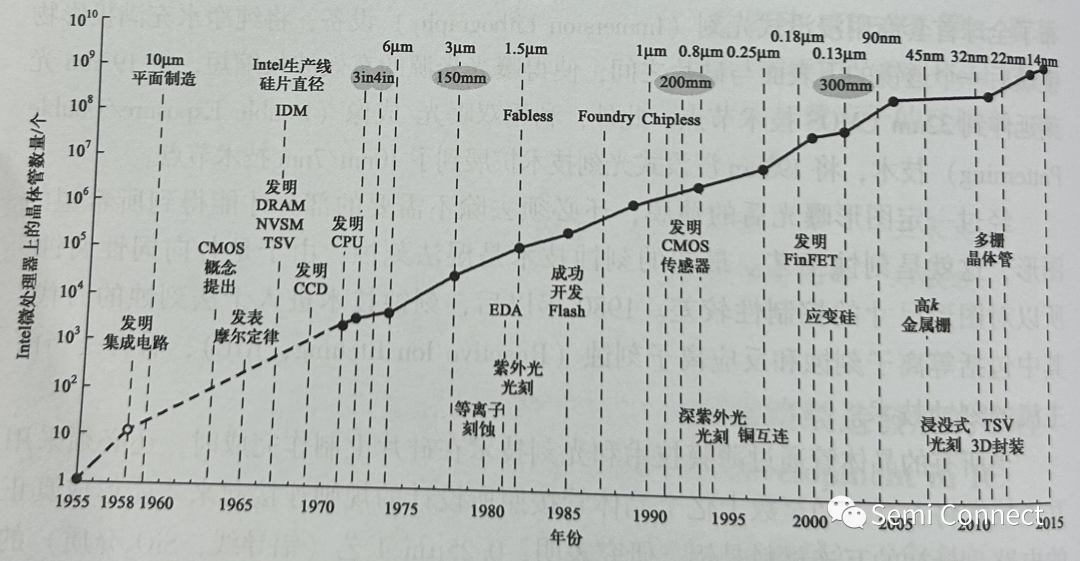

集成電路制造技術中的另一個發展趨勢是硅片直徑不斷增大。以Intel 生產線為例,1972年硅片直徑為 3in,1992,年為 200mm,2002 年 Intel 建立了第一條300mm 硅片的生產線。

綜上所述,集成電路制造技術發展的重要里程碑如圖所示。

審核編輯:湯梓紅

-

集成電路

+關注

關注

5392文章

11622瀏覽量

363175 -

電路設計

+關注

關注

6677文章

2464瀏覽量

205335 -

封裝

+關注

關注

127文章

7992瀏覽量

143400

原文標題:集成電路制造發展的里程碑,積體電路製造發展的里程碑

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

集成電路制造技術的應用

集成電路的發展趨勢與設計挑戰

集成電路電源芯片的分類及發展

世界集成電路發展歷程及產業結構的變化

全球集成電路產業的發展特點是什么?

9.5.1 集成電路對光掩模材料的要求及發展∈《集成電路產業全書》

集成電路制造的起源和發展

集成電路封裝的發展歷程

集成電路制造的發展歷程

集成電路制造的發展歷程

評論