什么是 ASIC 設計

ASIC 設計是開發復雜電子系統的過程。該系統可制造成特殊用途的半導體設備,通常用于大批量應用或具有嚴格的功耗、性能和尺寸限制的應用。ASIC 系統設計人員使用高級語言并通過仿真和可視化來開發和評估算法。

許多系統設計人員使用 MATLAB 和 Simulink 作為高級環境來指定 ASIC 設計的算法。通過將這些產品與第三方 EDA 工具結合使用,系統設計人員可以與 ASIC 硬件設計人員協作,使用 MATLAB 和 Simulink 對數字和模擬/混合信號 (AMS) ASIC 設計的新算法內容進行建模、仿真、優化和實現。

建模

您可以選擇使用 MATLAB 或 Simulink 開發硬件實現的算法來開始 ASIC 設計開發。MATLAB 提供了一種基于語言且無時間限制的簡潔建模環境,而 Simulink 提供了一種支持使用多速率模塊圖、狀態機和其他建模結構進行圖形化建模的環境。MATLAB 代碼可以整合到 Simulink 模型中,因此,您可以從 MATLAB 順利過渡到 Simulink 工作流。

通過將 Simulink 模型與現有代碼整合并使用 HDL 協同仿真對其進行仿真,來增強該模型以使其適用于 ASIC 設計。為了評估模擬組件與數字組件之間的交互,可以添加 Mixed-Signal Blockset 中的組件,如鎖相環 (PLL) 與數據轉換器(ADC 和 DAC)。

針對代碼生成優化模型

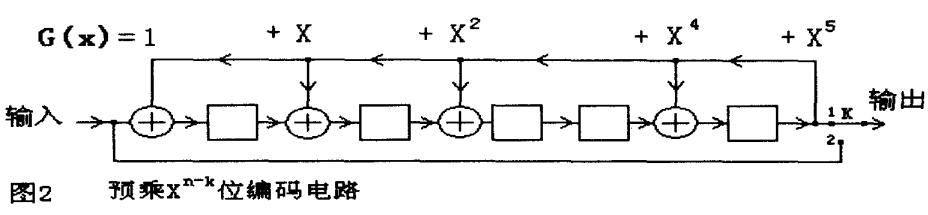

接下來,您可以基于硬件實現優化 ASIC 設計模型。算法開發人員可與 ASIC 硬件設計人員協作優化模型的硬件架構。首先是審查 MATLAB 代碼或 Simulink 模型,驗證它是否適用于 HDL 代碼生成。我們有 300 多個 Simulink 模塊和 200 多個 MATLAB 函數支持生成 HDL 代碼,您可以使用它們來構建模型。其次是使用 Fixed-Point Designer 將浮點模型轉換為定點模型,以減少設計的面積和功耗。通過將 Simulink 模型從基于幀的模型轉換為流式模型,可以針對 ASIC 設計進一步優化這些模型。

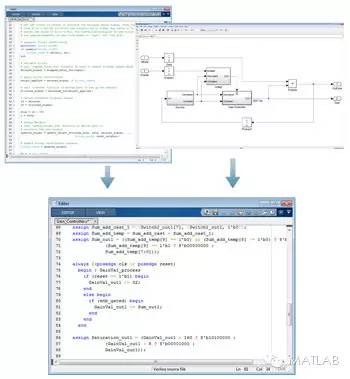

針對 HDL 代碼生成進行基于模型的優化

通過 ASIC 架構,可以采用多種方式從功耗-性能-面積 (PPA) 方面優化實現。系統設計人員可以與 ASIC 硬件設計人員協作,使用 HDL Coder 從 MATLAB 代碼或 Simulink 模型生成可綜合的 Verilog 和 VHDL 代碼。HDL Coder 提供了一系列優化選項,可以幫助設計人員盡可能實現 ASIC 設計的最高性能。這些選項包括時鐘速率自動優化、資源共享和流水線化,它們可以顯著減少實現設計所需的邏輯數量。HDL Coder 還支持為多速率設計和觸發子系統生成 HDL 代碼。

HDL 和 SystemC 代碼生成

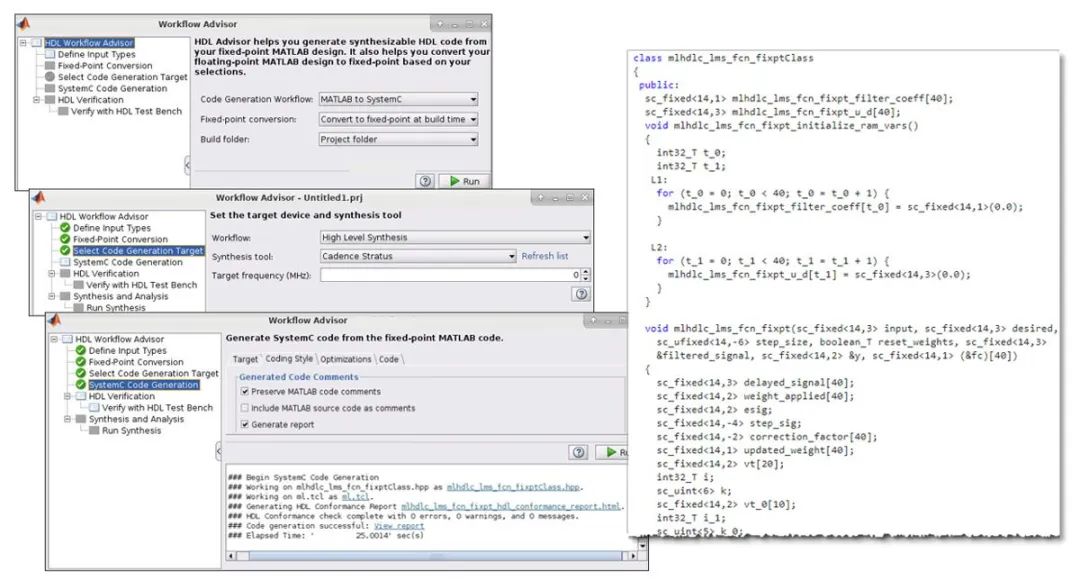

使用 HDL Coder,您可以按照引導式工作流完成 ASIC 設計的 HDL 代碼生成過程。HDL Coder 可檢查 MATLAB 和 Simulink 模型與 HDL 代碼生成的兼容性,支持自定義生成的 HDL 代碼,生成預綜合報告,并生成 HDL 測試平臺。

您可以通過 MATLAB 函數生成可綜合的 SystemC 代碼。生成的 SystemC 代碼可作為 Cadence Stratus 高級綜合工具的輸入。通過將 Stratus HLS 與 Genus 邏輯綜合解決方案和 Joules RTL 功耗解決方案相集成,ASIC 設計人員可以提前了解 ASIC 設計實現的功耗-性能-面積 (PPA)。

使用 HDL Coder,可以從 MATLAB 代碼生成 SystemC、Verilog/SystemVerilog 或 VHDL 代碼。

FPGA 原型構建

在 ASIC 設計中,FPGA 原型構建是一種通過硬件測試來評估算法實現的常見方法。HDL Coder 可與 AMD Xilinx、Intel 和 Microchip 設備的 FPGA 工作流相集成,在開發板上實現快速原型構建。

使用 FPGA 開發板對原型設計進行 FPGA 在環測試。

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605999 -

asic

+關注

關注

34文章

1206瀏覽量

120755 -

仿真

+關注

關注

50文章

4124瀏覽量

133991 -

Verilog

+關注

關注

28文章

1351瀏覽量

110391 -

代碼

+關注

關注

30文章

4825瀏覽量

69046

原文標題:什么是 ASIC 設計?利用仿真及 Verilog、VHDL 和 SystemC 代碼生成進行 ASIC 設計

文章出處:【微信號:MATLAB,微信公眾號:MATLAB】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

如何在FPGA上實現HDL代碼完成MATLAB轉換

如何在ModelSim下用SystemC的做驗證?

如何使用FPGA器件進行ASIC原型設計

ASIC和FPGA有什么區別

ASIC,ASIC是什么意思

ASIC到FPGA的原型驗證代碼轉換技術

MathWorks推出基于MATLAB生成HDL代碼的產品

并行CRC電路HDL代碼的快速生成

FPGA vs ASIC

什么是ASIC?ASIC中的“特定應用”是什么意思?

什么是ASIC設計?使用HDL和SystemC代碼生成進行ASIC設計

什么是ASIC設計?使用HDL和SystemC代碼生成進行ASIC設計

評論