在數據處理模塊中,我們經常會涉及數據流控反壓。什么是流控呢?簡單來說就是控制數據流停止發送。常見的流控機制分為帶內流控和帶外流控。帶外流控流控比較簡單,就是需要一根額外的信號線來表示流控信息,如ready,1表示可以發送數據,0表示不可以發送數據.如果取名為fc(flowcontrol),則0表示可以發送數據,1表示停止發送數據。帶內流控機制中,流控信息是通過數據通路傳輸的,沒有額外的流控信號線。帶內流控在接口模塊非常常見,例如以太MAC的pause幀和PCIe的信用量機制。流控系列文章分為4篇,今天是第一篇。首先將最簡單的流控機制,fifo與帶外流控。

1、什么是FIFO

FIFO(first in first out)是一種用寄存器reg或者RAM實現的存儲結構,常用于存儲數據通道中的數據流,采用先入先出的數據,當下游模塊無法及時處理上流模塊輸出的數據時,此時需要用FIFO暫存數據,防止數據丟失。

2、FIFO的流水反壓機制

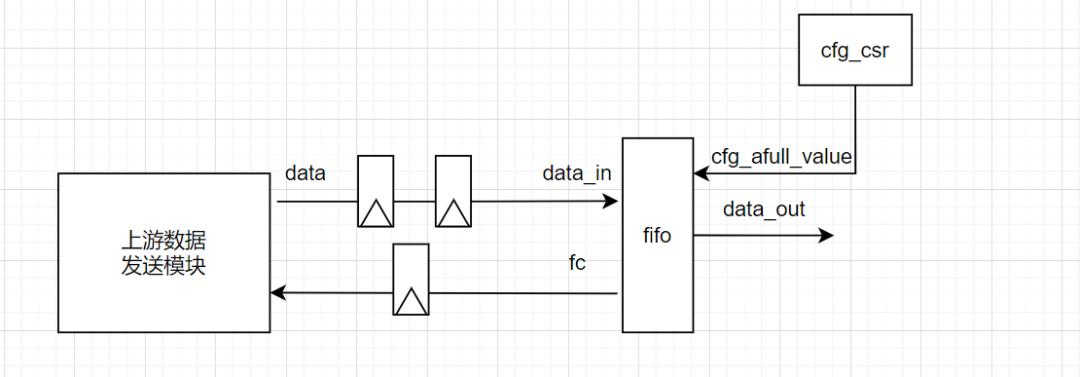

每一個fifo都有一個將滿閾值cfg_afull_value(名稱隨意,看得懂就行),通常由寄存器配置模塊cfg_csr提供。當fifo內的數據量達到或超過cfg_afull_value時,將滿信號afull從0跳變成1,即fc信號從0跳變1。上游發送模塊感知到fc為1時,則停止發送數據,有可能是1~2周期就停止,有可能是一個整包發送完才停止,根據代碼實現才能判斷。在fc跳變成1后,fifo需要能夠緩存路徑上的data以及上游發送模塊停止發流之前發出的所有data。這就是fifo的流控機制。

圖1:fifo流控示意圖

3、FIFO深度如何設置

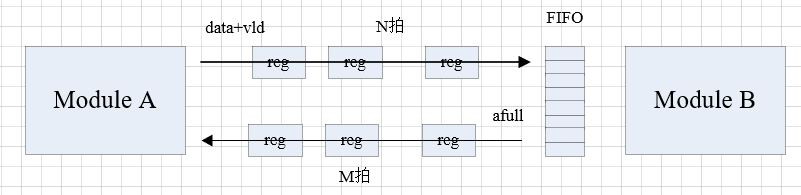

如圖2所示,數據data和有效信號vld從模塊A產生,經過N拍延時,輸入到FIFO,FIFO產生將滿信號afull,經過M拍延時反饋到模塊A,假設模塊A接收到afull=1時,立即停止發送數據。假設FIFO深度為fifo_depth,每拍為一個時鐘周期。

圖2:fifo深度計算示意圖

1為了保證FIFO不發生溢出,請問將滿閾值cfg_afull_value至少應該設置成多少?

2為了充分發揮FIFO的性能,FIFO深度depth應該為多少?

FIFO將滿閾值如何設置:

當FIFO中的數據為cfg_afull_value時,產生afull=1,

Afull=1經過M拍到達模塊A,此時FIFO中應該有(cfg_afull_value+M)個數據。

Afull=1到達模塊A時,模塊A立即停止發送數據,此時電路中還存在N拍數據將陸續送到FIFO中,所以最后FIFO中應該為(cfg_afull_value+M+N)個數據,

為了保證數據不會溢出,所以應該滿足公式fifo_depth>= cfg_afull_value+M+N,因此,將滿閾值應該至少為depth_fifo-(M+N)

FIFO深度depth應該為多少?

若fifo_depth過小,afull有效之后,fifo中存儲的數據將很快被下游數據讀取,而新的數據又無法及時到達FIFO,因此會造成流水氣泡,影響電路性能。

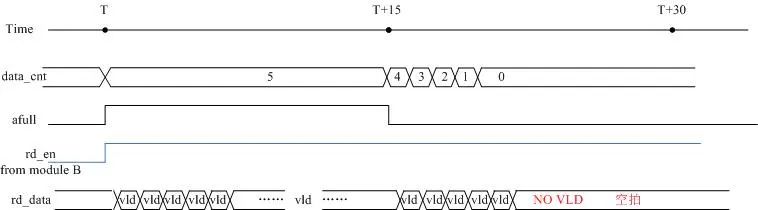

假設M=5 ,N=10,假設fifo_depth=20,則cfg_afull_value=5, 所以在T時刻,fifo中存了5個數據后afull=1會有效,在之后的15個周期內會陸續存入15個數據。假設下游模塊B每個周期讀取FIFO中的一個數據,因為當FIFO內的數據data_cnt小于5時,afull才會無效(為0),因此在T+15和T+30的時刻內,下游電路B只能讀5個數據,因此會造成數據斷流,影響電路性能。

圖3:流控信號時序圖

為保證電路性能,在T+15到T+30這個時間段內應該有15個數據可讀,因此cfg_afull_value應該不小于15(M+N)。所以FIFO深度應該不小于2*(M+N)

結束語

其實FIFO的流控方式有個明顯的弊端,一旦反壓路徑M(見圖2)過大,會明顯浪費資源。

編輯:黃飛

-

寄存器

+關注

關注

31文章

5363瀏覽量

121158 -

RAM

+關注

關注

8文章

1369瀏覽量

115002 -

fifo

+關注

關注

3文章

389瀏覽量

43855 -

Mac

+關注

關注

0文章

1110瀏覽量

51706

原文標題:4種常見的流控機制(一) FIFO與流控

文章出處:【微信號:IC學習,微信公眾號:IC學習】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

FIFO隊列原理簡述

鏈接后的RX郵箱的FIFO機制是什么意思?

鏈接CAN RX郵箱的FIFO機制怎么使用?

流控制機制,流控制機制原理是什么?

FPGA之FIFO練習3:設計思路

FPGA之FIFO的原理概述

STM32F429芯片帶FIFO的DMA傳輸實現過程

異步FIFO之Verilog代碼實現案例

過流保護是由什么組成 過流保護與其它保護機制的區別

XILINX FPGA IP之FIFO Generator例化仿真

常見的流控機制之fifo與帶外流控

常見的流控機制之fifo與帶外流控

評論