01

復合狀態

復合狀態是一個非常有用的工具,可以幫助分解和分組一些相關的狀態( 復合狀態的作用 ),它們可以對它們進行過渡,這將傳播到所有子狀態。復合狀態必須滿足某些格式良好的條件才能有效:

- 復合狀態必須具有初始狀態(可視為默認端口)。

- 從子項到子項的轉換不能“跨越”復合狀態的邊界(使用輸入/輸出端口獲得相同的效果)。

當走過指向復合狀態的過渡時,將從復合的初始(默認)狀態繼續執行。

02

歷史機制

歷史機制將以復合狀態存儲最后一個活動狀態,并在任何后續轉換到相同復合狀態時“恢復”其激活( 這就是歷史機制的作用 )。此機制不會影響輸入端口,輸入端口的行為就像以前沒有保存的歷史記錄一樣( 歷史機制的特點 )。

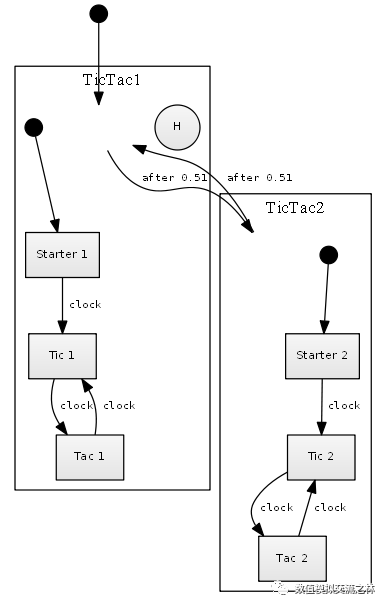

在這個例子中,我們模擬了兩個鐘擺在每個時鐘事件中切換,每 0.51 秒在兩者之間交替一次。在 TicTac1 中,我們從狀態“ Starter 1 ”開始,然后在“Tic 1”和“Tac 1”之間繼續。然后我們跳到 TicTac2,繼續“Starter 2”。在“Tic 2”和“Tac 2”之間跳躍0.51秒后,我們回到“TicTac1”。

然后,由于歷史節點,我們記住上次訪問的狀態并直接進入它,在本例中為“Tic1”,Starter 1 不會重新激活。當返回到 TicTac2 時,由于沒有歷史記錄狀態,我們從“Starter 2”狀態重新啟動。

所有這些都可以在下面顯示的模擬該狀態圖的計時圖上看到。(一定要結合上面的話與下面的圖)

-

信號處理器

+關注

關注

1文章

254瀏覽量

25351 -

有限狀態機

+關注

關注

0文章

52瀏覽量

10372 -

狀態機

+關注

關注

2文章

492瀏覽量

27653 -

fsm

+關注

關注

0文章

35瀏覽量

12844 -

邏輯控制器

+關注

關注

0文章

42瀏覽量

9543

發布評論請先 登錄

相關推薦

什么是有限狀態機呢

有限狀態機的建模與優化設計

VHDL有限狀態機設計-ST

初學者對有限狀態機(FSM)的設計的認識

如何使用FPGA實現序列檢測有限狀態機

有限狀態機設計是HDL Designer Series的關鍵應用

基于事件驅動的有限狀態機介紹

基于事件驅動的有限狀態機介紹

一個基于事件驅動的有限狀態機

什么是有限狀態機?如何解決傳統有限狀態機「狀態爆炸」問題?

有限狀態機復合狀態與歷史機制是什么意思?

有限狀態機復合狀態與歷史機制是什么意思?

評論