SerDes的簡介

SerDes 是SERializer串行 器/DESerializer解串器的簡稱,這種主流的高速的時分多路復用(TDM)點對點的串行通信技術可以充分利用通信的信道容量,提升通信速度,進而大量的降低通信成本。目前,商用基于SerDes架構的通信協議最高可實現單通道112Gbps的速率。

SerDes的主要作用就是把并行數據轉化成為串行數據,或者將串行數據轉化為并行數據的,能提供比并行傳輸更高帶寬。

實際上PCIE,JESD204B等復雜協議都是基于SerDes協議,常見的電SerDes就PCIE等協議來說,更接近物理層,所以SerDes通常又被稱之為物理層(PHY)器件。

正是因為SerDes的強電氣屬性,使得 Serdes具有以下優點:

①減少布線沖突(非獨立時鐘嵌入在數據流中,解決了限制數據傳輸速率的Signal時鐘的Jilter問 題);帶寬高 ;

②引腳數目少 ;

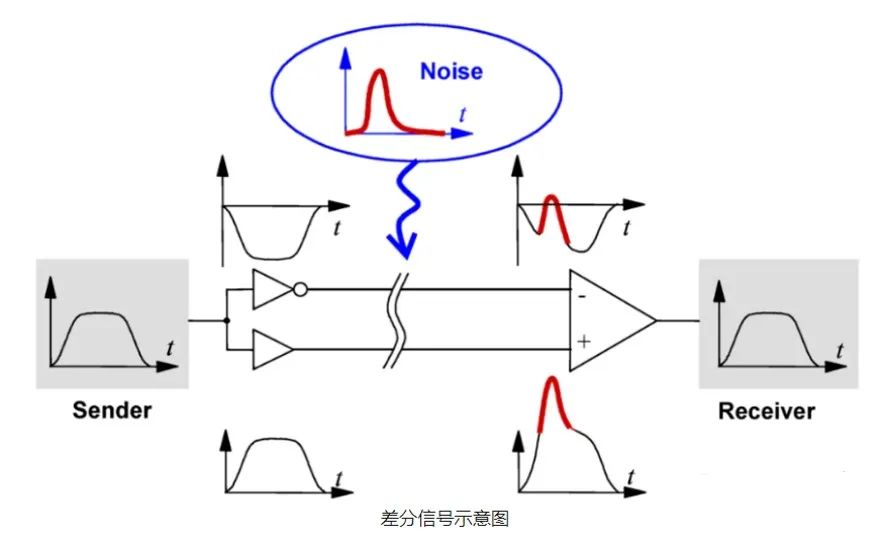

③抗噪聲、抗干擾能力強(差分傳輸);

④降低開關噪聲;

⑤擴展能力強;

⑥更低的功耗和封裝成本;

SerDes的分類

SerDes支持非常多的的主流工業標準,比如Serial RapidIO ,FiberChannel(FC),PCI-Express (PCIE),Advanced Switching Interface,Serial ATA(SATA),1-Gb Ethernet,10-Gb Ethernet(XAUI),Infiniband 1X,4X,12X等。根據SerDes的結構的不同可以將其分為四類:

①并行時鐘SerDes:將并行寬總線串行化為多個差分信號對,傳送與數據并聯的時鐘。這些SerDes 比較便宜,在需要同時使用多個SerDes 的應用中,可以通過電纜或背板有效地擴展寬總線;

②8B/10B編碼SerDes(最常見的結構):將每個數據字節映射到10bit代碼,然后將其串行化為單一 信號對。10位代碼是這樣定義的:為接收器鐘恢復提供足夠的轉換,并且保證直流平衡(即發送相 等數量的‘1’和‘0’)。這些屬性使8B/10B編碼SerDes 能夠在有損耗的互連和光纖傳輸中以較少的信號失真高速運行;

③嵌入式時鐘SerDes:將數據總線和時鐘串化為一個串行信號對。兩個時鐘位,一高一低,在每個 時鐘循環中內嵌串行數據流,對每個串行化字的開始和結束成幀,并且在串行流中建立定期的上升邊沿。由于有效負載夾在嵌入式時鐘位之間,因此數據有效負載字寬度并不限定于字節的倍數;

④位交錯SerDes:將多個輸入串行流中的位匯聚為更快的串行信號對。

SerDes的結構

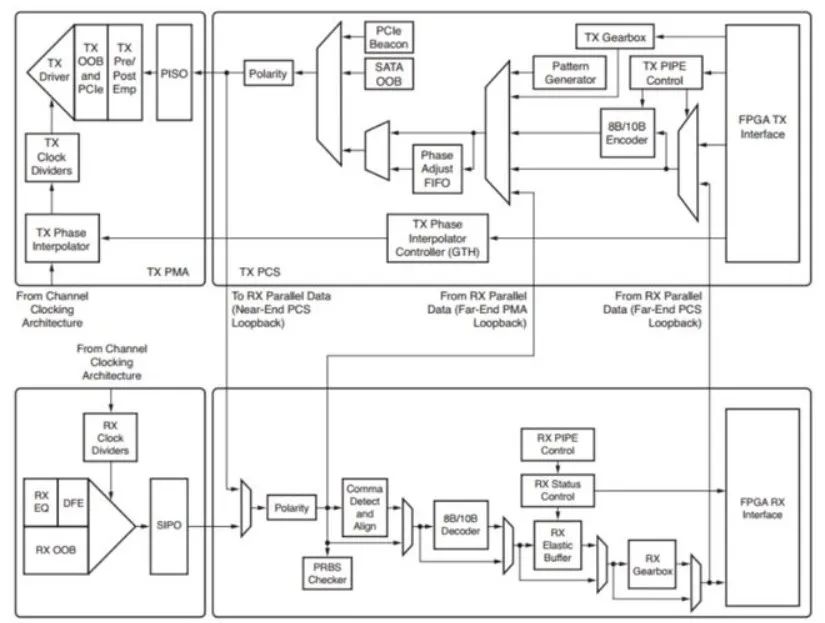

SerDes收發器內部包括高速串并轉換電路、時鐘數據恢復電路、數據編解碼電路、時鐘糾正和通道綁定電路,為各種高速串行數據傳輸協議提供了物理層(PHY)基礎。而主流的8B/10B編 碼SerDes則主要由物理介質相關子層( PMD)、物理媒介適配層(Physical Media Attachment,PMA)和物理編碼子層( Physical Coding Sublayer,PCS )所組成,且收發器的 TX發送端和RX接收端功能獨立。

SerDes收發器內部的電路物理層結構圖

各物理層的作用:

①PCS層,負責數據流的編碼/解碼,是標準的可綜合CMOS數字邏輯,可以通過邏輯綜合實現 軟硬綜合實現。

②PMA層,是數模混合CML/CMOS電路,負責負責串化/解串化,是理解SerDes區別于并行接 口的關鍵。

③PMD層,負責串行信號通信。

涉及到的相關模塊:

①TXPLL:這個模塊主要使用具有1ps以下的抖動的時鐘為參考,輸出數GHZ級的時鐘。

②RXCDR(時鐘恢復):這個模塊是一個復雜的控制回路,作用是來追蹤傳入數據的平均相位, 并不管Path上的任何SI或失真,通常是通過復雜的相位旋轉器或CDR驅動的鎖相環來完成的。

③TXdriver:這個模塊把序列化模塊轉化為差分信號。

④RX均衡器:此模塊用連續的時間均衡器以及DFE(裁決反饋均衡器)來均衡高速效應,通常 需要一個自動增益的電路來促進均衡效果,RX均衡器通常以狀態機邏輯和軟件的形式來實現

自動校準。

轉化過程:

①發送(TX)即并轉串,簡單的來說就是并行信號通過FiFO,傳遞給內部的8b/10b編碼器、擾碼器,防止數據連0/1,之后傳遞給串行器進行轉化,經過均衡器均衡后,由驅動發出。

②接收(RX)即串轉并,簡單的來說就是輸入的串行信號經過線性均衡器均衡后,去除了高速時鐘的jilter后,CDR從數據中恢復Caputure時鐘,并通過解串器轉為對齊的并行信號,由驅動發出。

SerDes底層硬件

SerDes底層硬件包括早期的LVDS和現在CML:SerDes信號層采用的LVDS工作在155Mbps~1.25Gbps之間,而CML(電流模式信號)在600Mbps和10+ Gbps。因此現在SerDes一般使用CML。但是LVDS和CML信號可以互通,但要有外接電阻做電平轉換。

高速邏輯電平的特性

LVDS、CML、LVPECL之間是有區別,但都使用差分傳輸Differential Transmission 信號傳輸的一種技術,區別于傳統的一根信號線一根地線的非平衡型單端Single End Transmission 做法,差分傳輸在這兩根線上都傳輸信號,這兩個信號的振幅相同,相位相反。在這兩根線上的傳輸的信號就是差分信號。信號接收端比較這兩個電壓的差值來判斷發送端發送的邏輯狀態。在電路板上,差分走線必須是等長、等寬、緊密靠近、且在同一層面的兩根線。

審核編輯:劉清

-

接收器

+關注

關注

14文章

2479瀏覽量

72213 -

編解碼器

+關注

關注

0文章

268瀏覽量

24304 -

PHY

+關注

關注

2文章

305瀏覽量

51862 -

串行解串器

+關注

關注

0文章

7瀏覽量

6711 -

SERDES接口

+關注

關注

0文章

28瀏覽量

3061

原文標題:SerDes的基礎知識

文章出處:【微信號:信號完整性學習之路,微信公眾號:信號完整性學習之路】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

通信基礎知識教程

高速接口SerDes基礎知識總結

SerDes的基礎知識

SerDes的基礎知識

評論