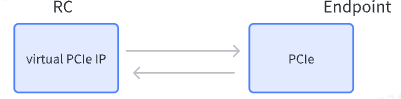

我們在進行PCIe RTL仿真時,由于PCIe ltssm協商過程比較復雜,導致PCIe ltssm進入L0狀態所花費的時間比較長(大概在20~60分鐘,因代碼復雜度、服務器性能、PCIe速率不同而所有差異),而如果進行網表級別的仿真一般需要1周以上的時間。此時加速PCIe仿真,提高效率是我們必須考慮的問題。常見的加速模式有如下三種。我們以VIP PCIe(Verification IP,一種PCIe驗證虛擬IP)對接Endpoint的仿真環境進行說明。  ? ? ? 1、選擇低速模式加速仿真 在測試某些與速率不相關的功能時,為了減少仿真時間,可以選擇低速率模式,如選擇gen1,gen2。特別是gen1(2.5Gbps)速率下,ltssm協商所需要的時間最短。適用于測試跟速率無關的功能,比如說用戶邏輯功能的正確性。Gen3以及以上速率跟gen1/gen2比起來,多了均衡協商過程,此階段耗時最多。 2、使用PIPE口仿真加速 在完整的PCIe協商過程中,PHY的link協商時間較長。如果對接VIP支持PIPE(phy-interface-pci-express)互連的話,可以bypass PHY,直接使用PIPE接口連接,即Endpoint PCIe PIPE口對接VIP PIPE,能夠有效減少PCIe上電協商所需要的時間。側重PCIe TL層功能點以及用戶邏輯的測試用例,可以bypass PHY,使用PIPE口互連,測試PHY相關功能的用例不能使用此方法。 3、使用加速宏定義或者配置加速

? ? ? 1、選擇低速模式加速仿真 在測試某些與速率不相關的功能時,為了減少仿真時間,可以選擇低速率模式,如選擇gen1,gen2。特別是gen1(2.5Gbps)速率下,ltssm協商所需要的時間最短。適用于測試跟速率無關的功能,比如說用戶邏輯功能的正確性。Gen3以及以上速率跟gen1/gen2比起來,多了均衡協商過程,此階段耗時最多。 2、使用PIPE口仿真加速 在完整的PCIe協商過程中,PHY的link協商時間較長。如果對接VIP支持PIPE(phy-interface-pci-express)互連的話,可以bypass PHY,直接使用PIPE接口連接,即Endpoint PCIe PIPE口對接VIP PIPE,能夠有效減少PCIe上電協商所需要的時間。側重PCIe TL層功能點以及用戶邏輯的測試用例,可以bypass PHY,使用PIPE口互連,測試PHY相關功能的用例不能使用此方法。 3、使用加速宏定義或者配置加速

PCIe ctrl(TL層和DL層)和PHY在設計時為了方便用戶測試,一般都添加了加速的手段,通常有2種手段:

1)代碼頂層或者內部的部分的寄存器決定是否加速:

如果在頂層,可以通過配置寄存器 or 改變例化值的方式實現; 如果在內部,可以通過force的方式實現

2)通過宏定義實現:

例如VCS仿真時加上+define+AUTO_FAST_SIMULIATION,具體宏定義名稱由IP確定。

加速原理 A)大幅減少鏈路狀態機在各狀態下的timeout時間,相對于正常模式,仿真模式下timeout時間可以減少至正常模式的千分之一或百分之一; B)大幅度減少訓練成功所需序列的數量,例如連續接收到1000個序列表示當前狀態訓練成功,加速模式下可以只需要10個序列就能訓練成功

審核編輯:彭菁

-

寄存器

+關注

關注

31文章

5363瀏覽量

121169 -

仿真

+關注

關注

50文章

4124瀏覽量

133993 -

服務器

+關注

關注

12文章

9304瀏覽量

86066 -

PCIe

+關注

關注

15文章

1260瀏覽量

83193 -

代碼

+關注

關注

30文章

4827瀏覽量

69054

原文標題:驗證:3種加速PCIe仿真的方法

文章出處:【微信號:處芯積律,微信公眾號:處芯積律】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

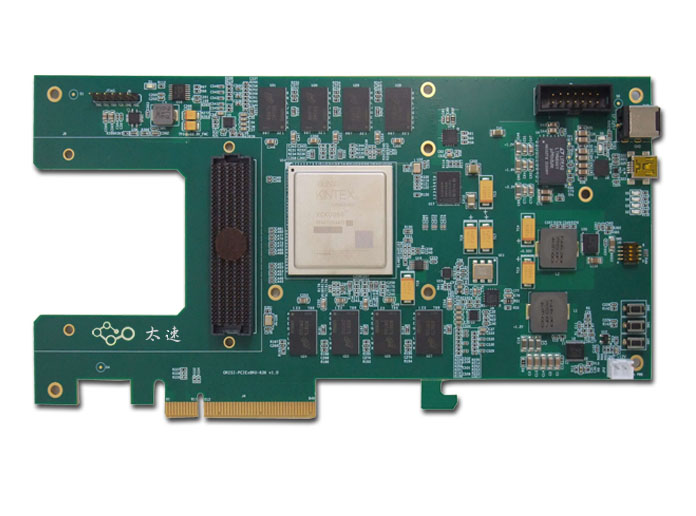

基于Xilinx XCKU115的半高PCIe x8硬件加速卡

英特爾Optane On Secondary HDD無法加速PCIe驅動器

用于加速c代碼的PCIe FPGA如何開始

PCIe加速卡的發展

講真,這絕對是加速FPGA的仿真過程的最佳方法

加速FPGA的仿真方式之——腳本命令

PCIe的SmartNIC如何改變方案加速規則

求一種基于Xilinx XCKU115的半高PCIe x8 硬件加速卡

ADM-PCIE-8K5 PCIe加速器板--賽靈思公司最新成員

PCIe 5.0:加速云中的數據移動

是德科技推出PCIe和UCIe仿真解決方案

如何加速PCIe仿真

如何加速PCIe仿真

評論