在UVM寄存器模型的操作中,寄存器用于設置DUT狀態(tài)和芯片狀態(tài)信息的上報,有前門和后門讀寫兩種方式。

推而廣之,其他的DUT內(nèi)部信號,由于驗證的需要,有時也需要進行后門讀寫。這些信號除了包含前門可讀的寄存器以外,還會包含reg/wire信號、狀態(tài)機的狀態(tài)值、memory內(nèi)容等。

總的來看,獲取DUT內(nèi)部狀態(tài)分為前門和后門兩種方式。

前門讀寫

前門讀寫:使用總線對DUT發(fā)起真實的讀寫,一般需要總線VIP支持,僅針對DUT內(nèi)部可訪問的地址空間,如配置和上報寄存器、memory。

這種方式好處在于能夠和芯片真實的工作場景保持高度相似,能夠發(fā)現(xiàn)時序配合上的一些問題。

缺點一方面也是前門的“真實性”,當需要讀寫的地址空間數(shù)量很大時,會消耗非常多的仿真時間,影響用例的執(zhí)行效率。

另一方面是這種耗時的讀寫不滿足“實時性”比對的驗證要求。某些驗證環(huán)境中,可能需要在幾個cycle內(nèi)完成對DUT狀態(tài)的獲取和比對,這種場景下前門讀取方式則無法滿足。

后門讀寫

后門讀寫:繞過前門總線,直接通過DUT內(nèi)信號的hierarchy路徑強制force或者讀取信號值。

后門操作的方式可以分為:按信號的Hierarchy讀取、interface連接DUT信號、和VPI訪問。

1. 信號的Hierarchy讀取

DUT經(jīng)過編譯后,內(nèi)部的信號都有對應的hierarchy路徑,如dut.a.b.c,dut.out。在驗證環(huán)境中可以直接使用,例如:

bit A; A=dut.sub_block.A; if(A==0) begin ..... end

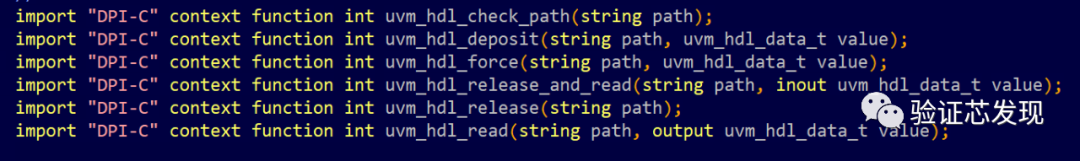

bitA; bit[15:0] B if(uvm_hdl_read("dut.sub_block.A",A))begin ..... end //bit[31:0] Y uvm_hdl_read("dut.X.Y[15:0]",B)//錯誤!使用VPI訪問缺點:不能按位域驅(qū)動和讀取。對于多bit信號,無法只對其中的部分bit操作。

一般而言對于黑盒驗證中的加密代碼,使用Hierarchy和VPI方式都是無法獲取加密代碼內(nèi)部信號的狀態(tài)。當然如果在已知加密代碼層次前提下,通過一些處理,還是可以通過Hierarchy方式進行后門操作。

審核編輯:湯梓紅

-

芯片

+關注

關注

456文章

51192瀏覽量

427336 -

寄存器

+關注

關注

31文章

5363瀏覽量

121199 -

仿真

+關注

關注

50文章

4124瀏覽量

134007 -

信號

+關注

關注

11文章

2807瀏覽量

77116 -

DUT

+關注

關注

0文章

189瀏覽量

12491

原文標題:驗證環(huán)境獲取DUT內(nèi)部信號的方法

文章出處:【微信號:處芯積律,微信公眾號:處芯積律】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關推薦

基于VMM驗證方法學的MCU驗證環(huán)境

基于VMM驗證方法學的MCU驗證環(huán)境

基于VMM的驗證環(huán)境的驗證MCU指令實現(xiàn)設計

基于VMM驗證方法學的MCU驗證環(huán)境實現(xiàn)方法介紹

SoC驗證環(huán)境搭建方法的研究

DUT 和 testbench 連接教程

UVM驗證平臺頂層有什么作用

驗證組件配置參數(shù)

基于DUT內(nèi)部寄存器值的鏡像

北京清微智能科技有限公司發(fā)布IC驗證新方法,實現(xiàn)雙DUT驗證

驗證環(huán)境獲取DUT內(nèi)部信號的方法

驗證環(huán)境獲取DUT內(nèi)部信號的方法

評論