背景

AD9144是一款支持jesd204b協議高速DAC芯片。AD9144-FMC-EBZ是基于AD9144的評估板(Evaluation Board),它是主要由AD9144,AD9516,與PIC16F單片機組成的系統。工程上使用AD9144具有時鐘時序要求很高和寄存器配置復雜的難點。

配置AD9144-FMC-EBZ,有兩種途徑:

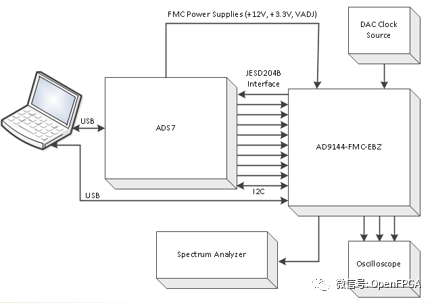

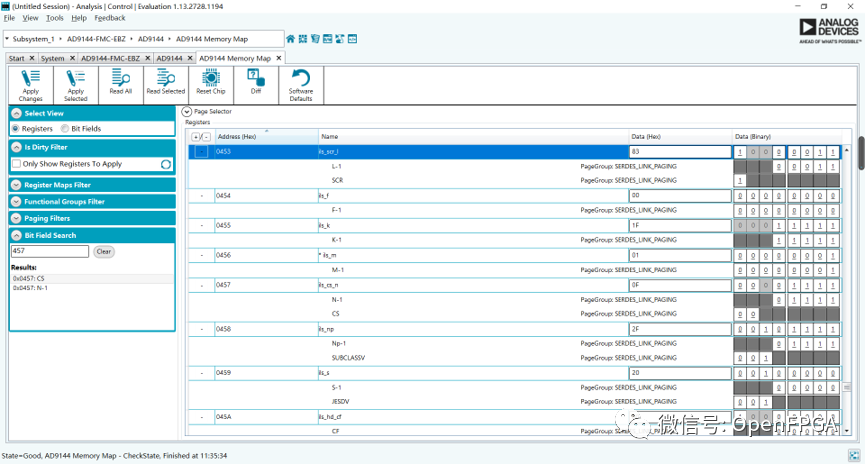

2、通過ADI提供的軟件工具,配合母板(ADS7)來配置寄存器,如圖所示:

遇到問題:

我們在嘗試第一種方法的時候,遇到了SPI寄存器寫不進的情況和讀寫不一致的情況。而第二種方法則需要ADS7用作母板。

調試

完成了以KC705作為母板,正確配置AD9144,并輸出62.5MHz正弦波。

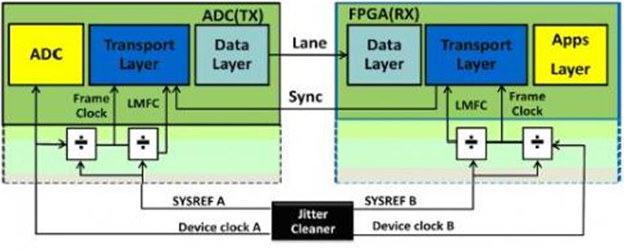

整個流程需要先在KC705上運行提供的HDL工程,隨后進入軟件工具配置流程。這里的HDL工程主要完成的是:Jesd204發送端的配置與正弦余弦信號的輸出。另外,這里的軟件工具配置流程既使用ADI官方提供的工具對AD9144和AD9516分別進行配置。

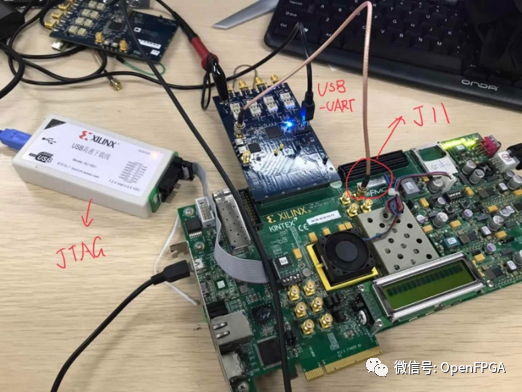

在調試開始前,硬件鏈接如下圖所示:

1、AD9516寄存器配置獲得

AD9516的作用是對輸入時鐘分頻,為AD9144分別提供:sysref(3.91M),和refclk(125M)。

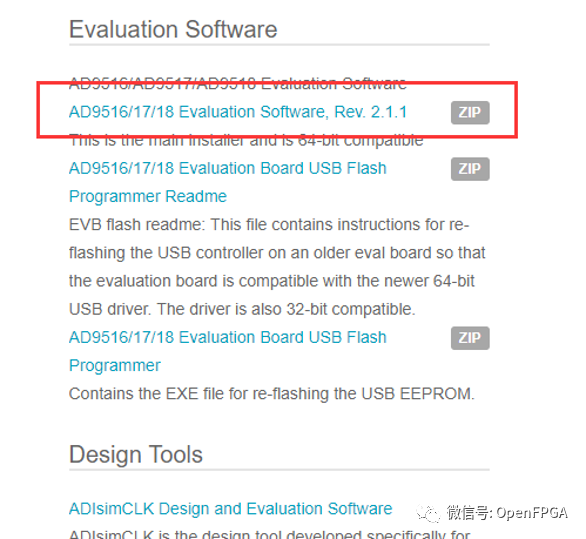

這里使用了AD9516-Evaluation-Software完成配置。

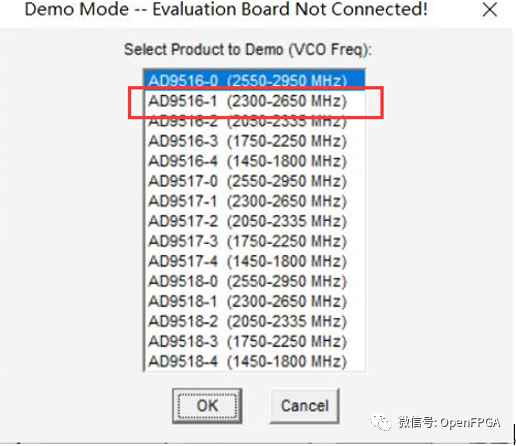

在安裝結束后,打開軟件并選擇正確的型號,這里選AD9516-1

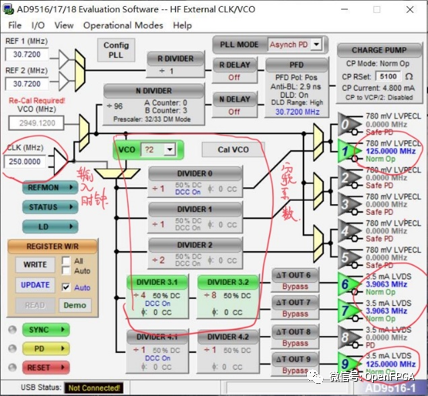

分別按下圖所示進行配置:輸入時鐘(來自KC705)設置為2500;分頻系數如圖設置:最后得到兩組頻率為120M和3.9063M的時鐘;點擊左下角的橙色框(RGISTER W/R)中的WRITE。

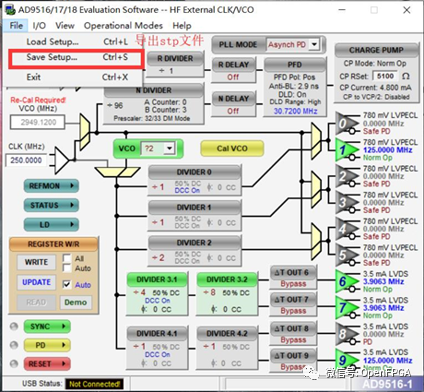

點擊“file”,點擊“Save Setup”,導出“stp”文件,如下圖所示。

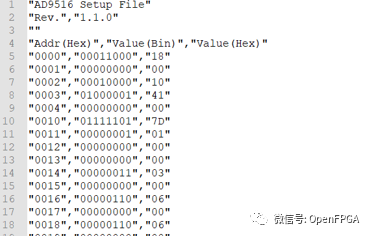

打開導出的.stp文件,如圖:這個文件記錄了寄存器地址與對應的值,將于后續步驟導入。

2、AD9144&AD9516寄存器配置:

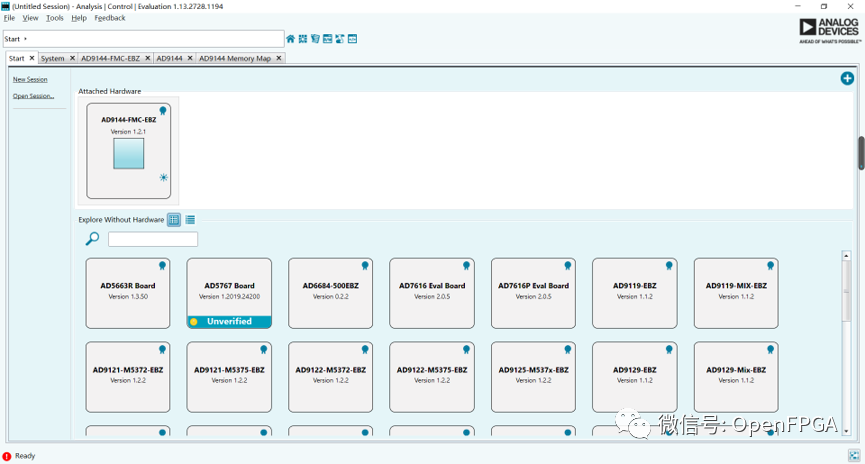

A、首先到AD公司官網搜索DAC Software Suite和Analysis Control Evaluation軟件,下載并安裝;

B、打開已經安裝好的ACE軟件,界面如下圖所示。在硬件連接正確的情況下,圖中紅圈會檢測到所連接的硬件板卡,點擊圖中綠圈的LED狀按鈕,AD9144-FMC-EBZ板卡上的藍色LED燈會隨之閃爍,說明連接成功。

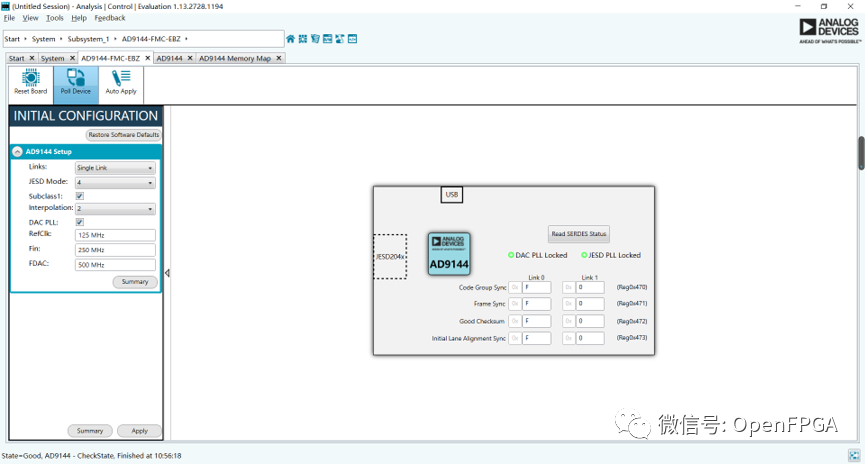

C、雙擊打開“AD9144-FMC-EBZ”板卡。在“initial configuration”界面中按如圖所示進行設置,點擊“summary”并“apply”,雙擊右側紅色圖框中的AD9144芯片。

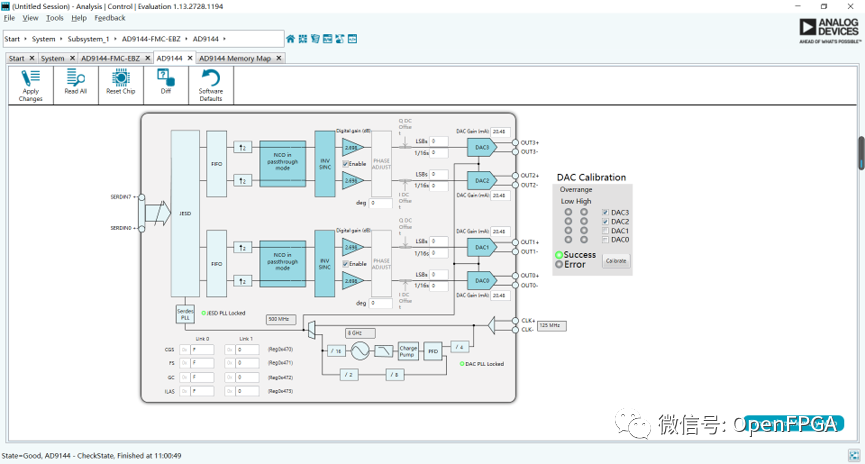

D、在打開的界面中按圖中配置設置DAC calibration,選擇“DAC3 DAC2”并點擊“calibrate”。

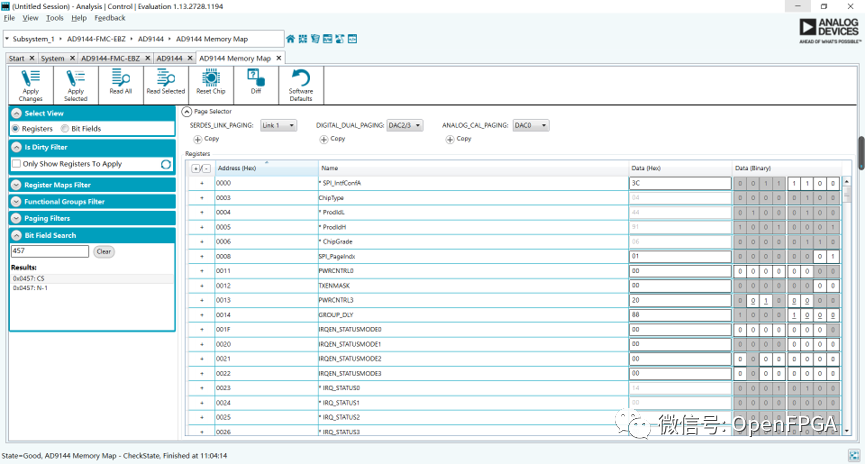

E、點擊上圖右下角的“Proceed to memory map”,按照項目所需配置好AD9144相關的寄存器表的值,點擊右上apply selected將對應的寄存器值寫入AD9144芯片。

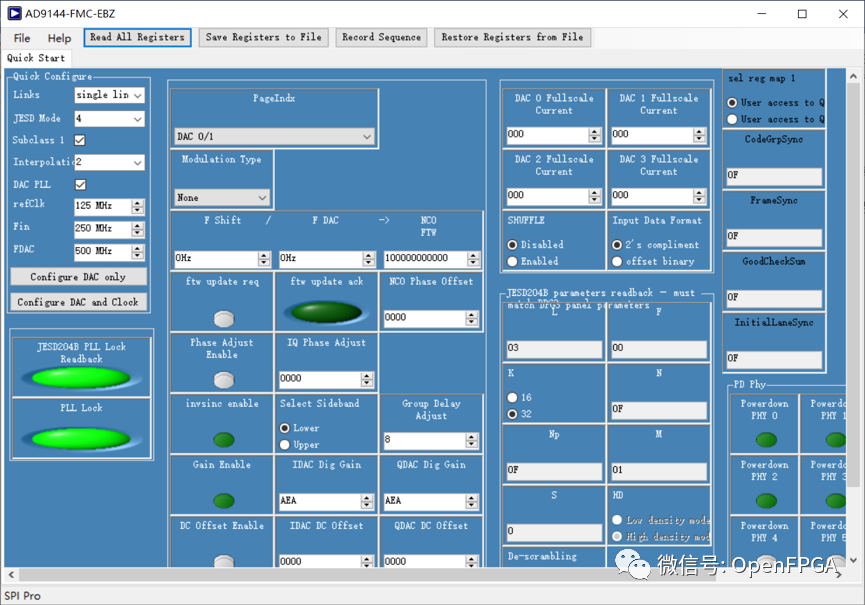

F、在電腦開始菜單>Analog Devices尋找“AD9144&AD9135&AD9136 SPI”并打開,軟件界面如圖所示:

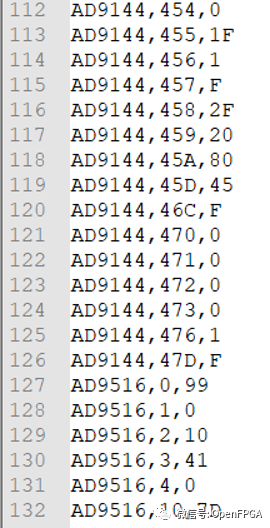

G、在上方框中點擊“read all registers”,然后點擊“save registers to file”得到“.csv”文件,右鍵將其用記事本打開,如圖所示,找到AD9516芯片開頭的寄存器區域,將之前通過AD9516 Evaluation Software得到的stp文件中的寄存器值添加進.csv文件中并保存。

如圖所示,第一列是AD9144/AD9516的芯片,第二列是對應芯片的寄存器地址,第三列是寄存器對應的值,將AD9516所有寄存器的值添加進來并保存。

H、打開“AD9144&AD9135&AD9136 SPI”軟件并選擇“restore registers from file”,將上一步中修改保存好的.csv文件導入。

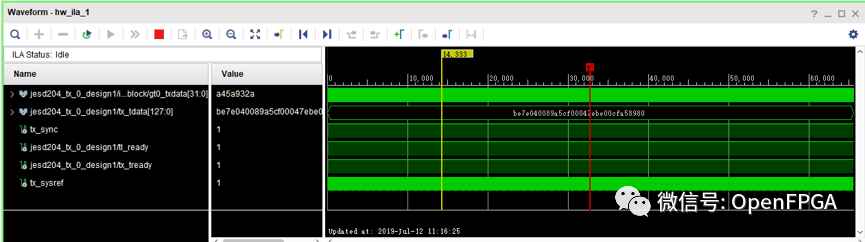

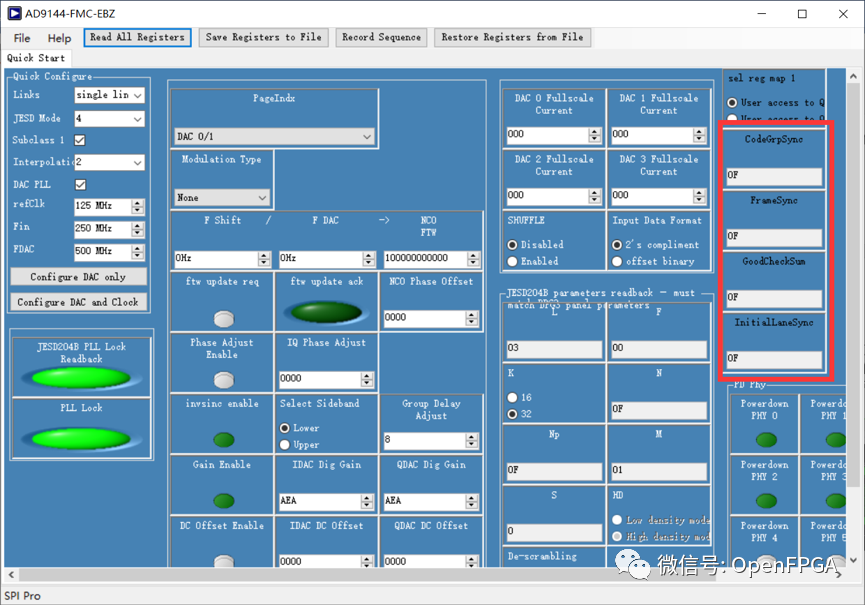

I、將vivado中的工程bit流文件燒錄到板子上,通過ila抓取并觀察tx_sync信號,發現信號持續拉高,返回AD9144&AD9135&AD9136 SPI軟件read all registers,觀察如圖區域,如果圖中所示四個寄存器值都為0F,vivado tx_sync持續拉高,并且txdata有數值輸出,則說明AD9144與JESD204B同步成功,此時用示波器測量AD9144板卡輸出可觀測到波形輸出。

調試過程中遭遇問題

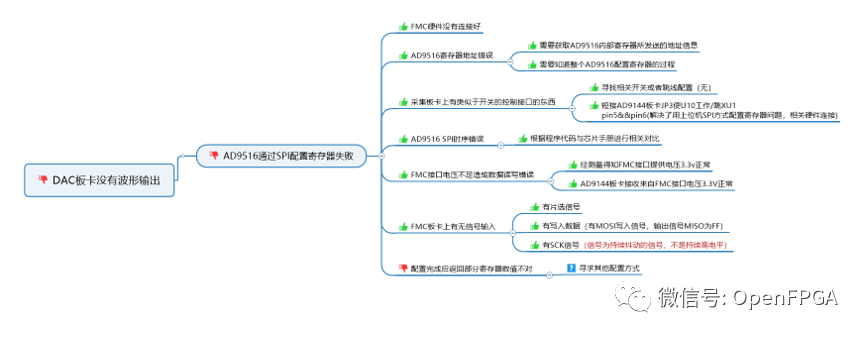

1.SPI配置失敗問題?

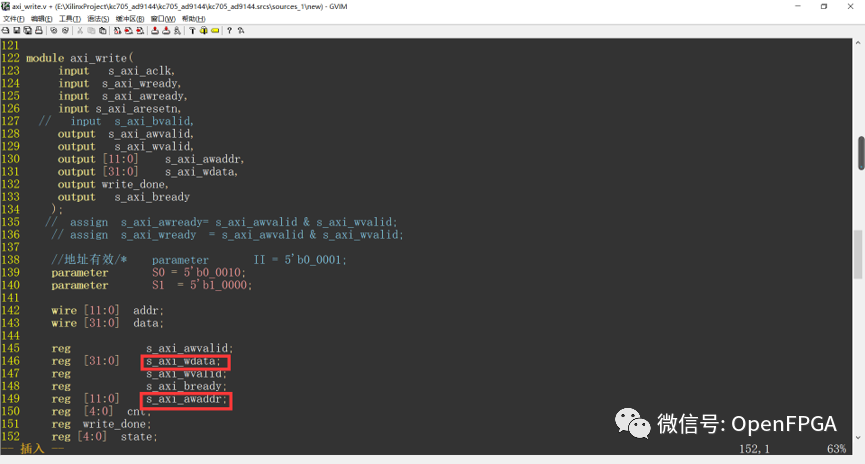

2.AXI-Lite的參數設置?

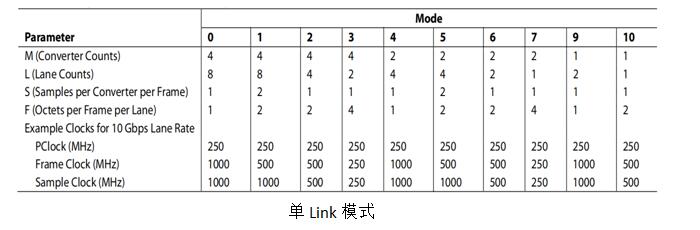

通過在Analysis Control Evaluation軟件中讀取AD9144寄存器表值,查詢0x453-0x45A寄存器值,得到關鍵參數L,SCR,F,K,M,N,N’,S,CF,HD等的值。

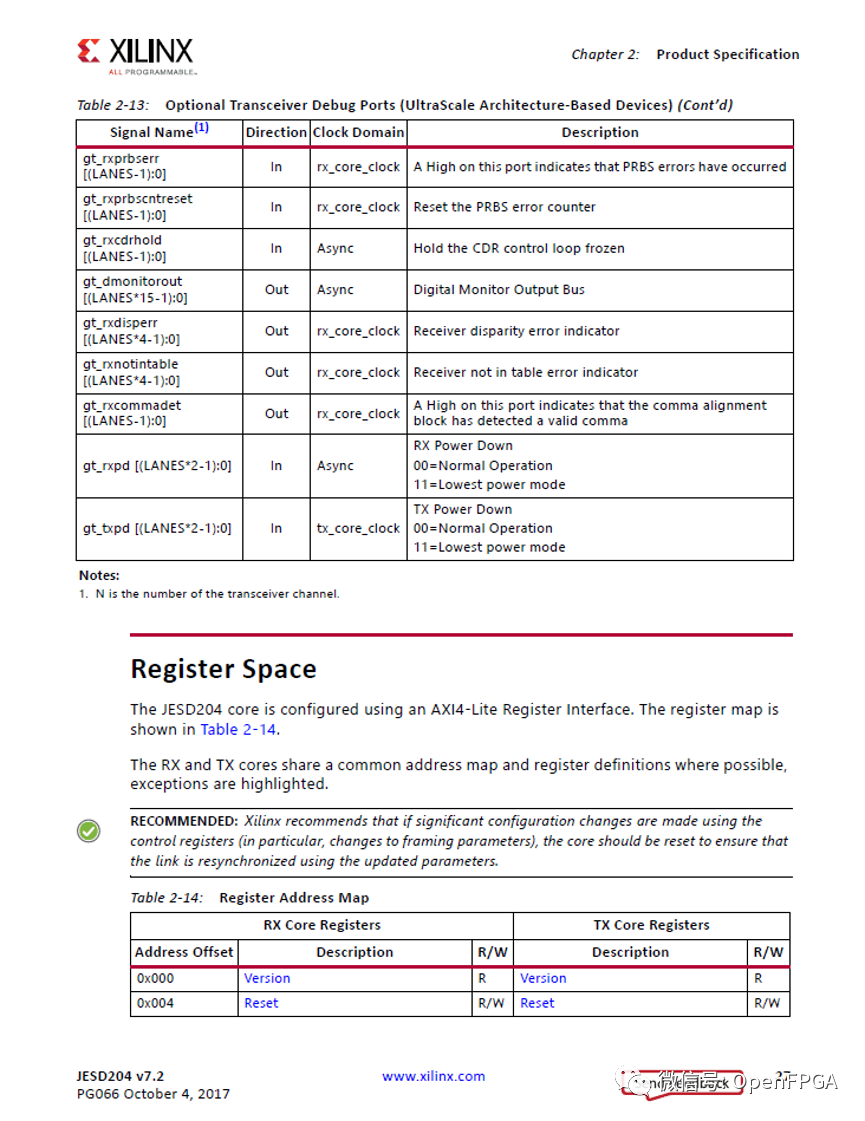

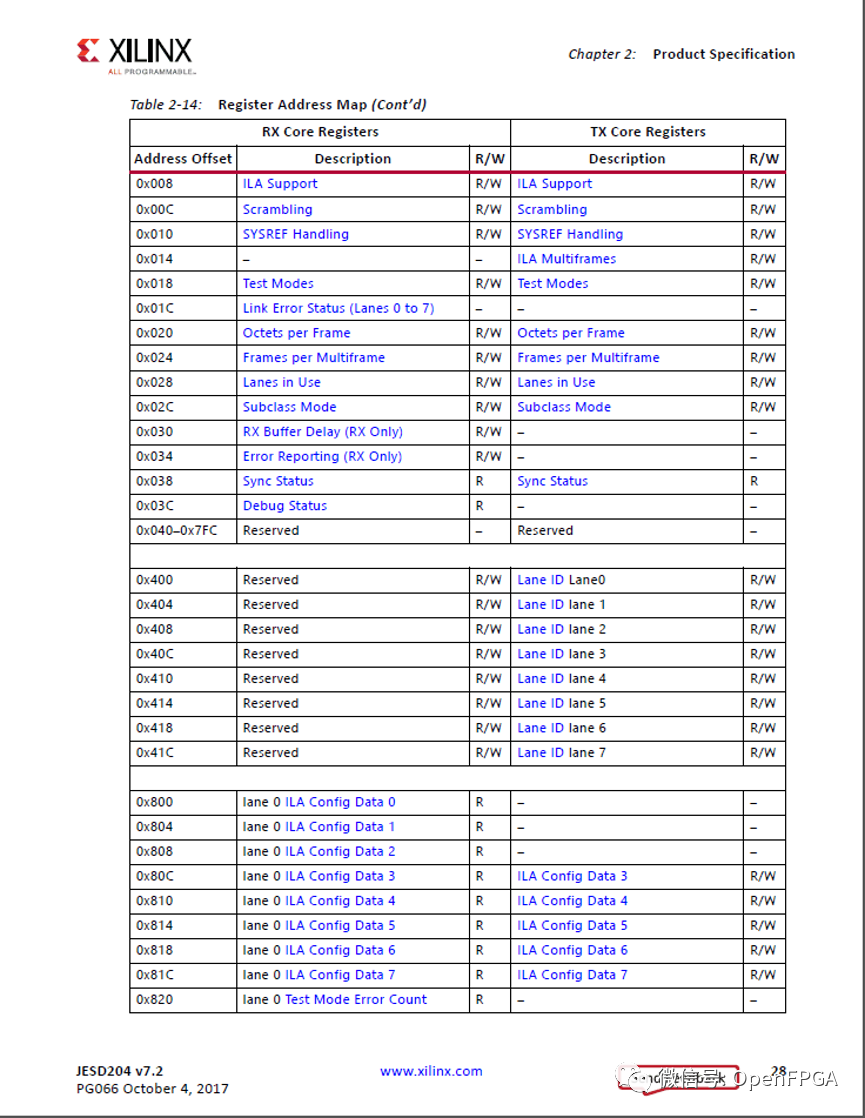

通過文檔PG066 P27-P28中所示的值,計算出AXI協議所需要的每個寄存器地址的值。填入到vivado工程模塊中的AXI協議部分。

Vivado工程中的AXI協議部分:地址填入PG066 P27-P28中的寄存器地址,值填入更據關鍵參數算出來的值。

審核編輯:劉清

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605996 -

芯片

+關注

關注

456文章

51170瀏覽量

427239 -

單片機

+關注

關注

6043文章

44622瀏覽量

638529 -

寄存器

+關注

關注

31文章

5363瀏覽量

121158 -

PIC單片機

+關注

關注

64文章

693瀏覽量

102086 -

dac

+關注

關注

43文章

2309瀏覽量

191563 -

DAC芯片

+關注

關注

1文章

32瀏覽量

14714 -

ad9144

+關注

關注

0文章

8瀏覽量

1918

原文標題:支持jesd204b協議高速DAC芯片AD9144-FMC-EBZ配置筆記

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

JESD204B的系統級優勢

FPGA高速數據采集設計之JESD204B接口應用場景

FPGA高速數據采集設計之JESD204B接口應用場景

支持jesd204b協議高速DAC芯片AD9144-FMC-EBZ配置筆記

如何讓JESD204B在FPGA上工作?FPGA對于JESD204B需要多少速度?

JESD204B協議有什么特點?

JESD204B協議介紹

JESD204B協議概述

基于NI PXI模塊化測試平臺對采用JESD204B協議進行測試

JESD204B時鐘網絡原理概述

使用JESD204B接口的AD9144高速DA轉換模塊參數設定(私人總結版)

JESD204B使用說明

支持jesd204b協議高速DAC芯片AD9144-FMC-EBZ

支持jesd204b協議高速DAC芯片AD9144-FMC-EBZ

評論