1、IAR IDE

IAR一直是Renesas強有力的合作伙伴,IAR IDE支持Renesas全系列MCU的開發(fā)和調(diào)試。IAR Embedded Workbench是一個完整的開發(fā)工具鏈,在易于使用的集成開發(fā)環(huán)境中提供了強大的代碼優(yōu)化和全面的調(diào)試功能。

2、Renesas RL78系列MCU

Renesas RL78系列MCU是Renesas 16-bit低功耗產(chǎn)品線,專為超低功耗設(shè)計,可以為客戶提供以較低的成本建立高集成度和高效節(jié)能的應(yīng)用平臺。

RL78系列MCU有三大主要特點:

1)低功耗:最低46uA/MHz

2)可擴展性:1KB~512KB Flash

3)高效:最高1.39DMIPS/MHz

此外,RL78系列MCU具有超級全面的產(chǎn)品線,同時也在不斷地推進新產(chǎn)品的開發(fā),以滿足客戶未來的產(chǎn)品升級需求。

3、使用IAR IDE仿真RL78內(nèi)置硬件乘法器 除法器注意事項

在使用IAR IDE進行RL78系列MCU仿真調(diào)試時,可執(zhí)行硬件仿真或軟件仿真(Simulator),但是,如果需要應(yīng)用硬件乘法器/除法器,則必須使用硬件仿真,不能使用軟件仿真(Simulator),軟件仿真(Simulator)不支持MCU內(nèi)部的硬件乘法器/除法器。

當執(zhí)行硬件仿真時,如果不勾選“Disable Hardware Multiplier/Divider Unit”:

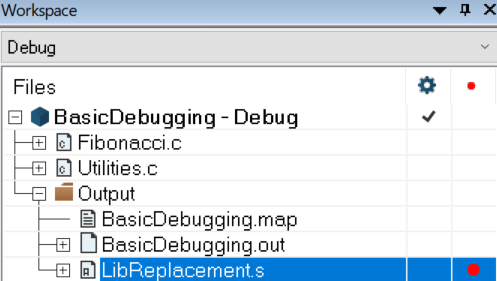

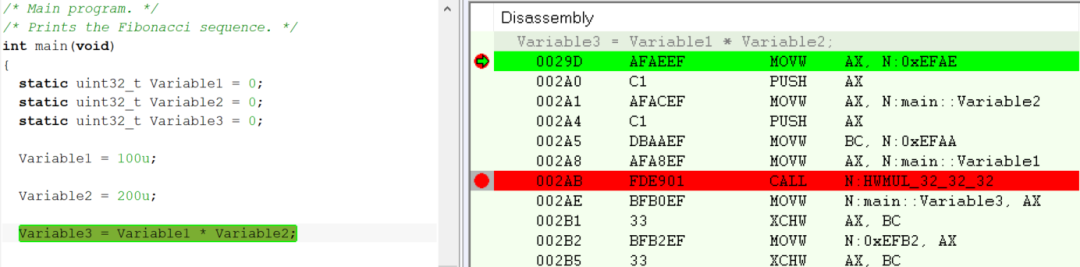

對應(yīng)的乘法操作會調(diào)用函數(shù)HWMUL_32_32_32,(HWMUL_32_32_32存在于工具自動生成的文件LibReplacement.s中,當不勾選“Disable Hardware Multiplier/Divider Unit”時,會自動在Output文件夾生成LibReplacement.s文件),例如:

在程序中可以看到:

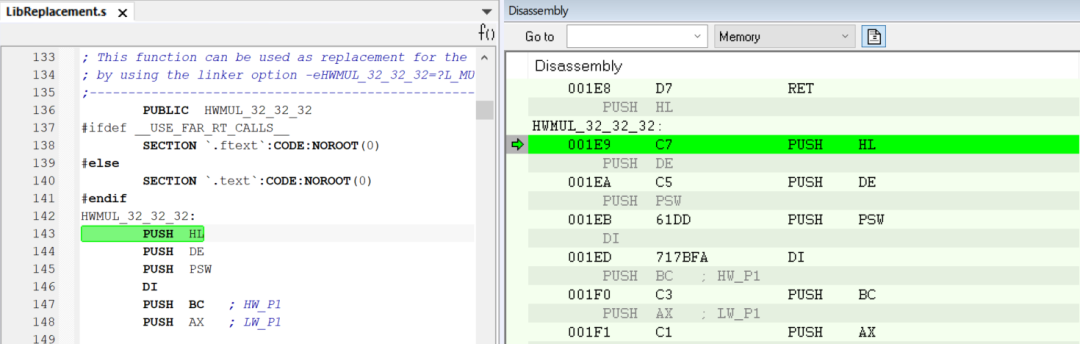

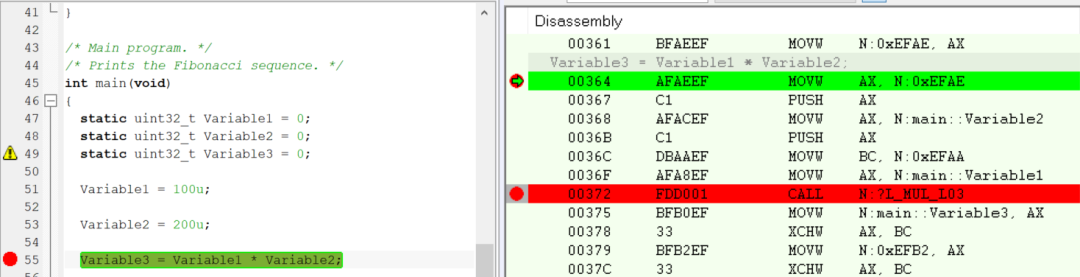

當勾選“Disable Hardware Multiplier/Divider Unit”時,編譯器會選擇對應(yīng)的軟件乘法庫函數(shù)L_MUL_L03來實現(xiàn)乘法操作:

需要注意的是,軟件乘法庫函數(shù)L_MUL_L03相對于HWMUL_32_32_32函數(shù)會需要更多的資源及運行時間。

來源:瑞薩MCU小百科

審核編輯:湯梓紅

-

mcu

+關(guān)注

關(guān)注

146文章

17317瀏覽量

352630 -

仿真

+關(guān)注

關(guān)注

50文章

4124瀏覽量

133984 -

IAR

+關(guān)注

關(guān)注

5文章

354瀏覽量

36779 -

IDE

+關(guān)注

關(guān)注

0文章

341瀏覽量

46877 -

除法器

+關(guān)注

關(guān)注

2文章

14瀏覽量

13914

發(fā)布評論請先 登錄

相關(guān)推薦

硬件乘法器的相關(guān)資料分享

并行除法器 ,并行除法器結(jié)構(gòu)原理是什么?

乘法器的基本概念

1/4平方乘法器

變跨導(dǎo)乘法器

進位保留Barrett模乘法器設(shè)計

使用verilogHDL實現(xiàn)乘法器

乘法器原理_乘法器的作用

AD533:低成本乘法器、除法器、平方器、平方器、根過時數(shù)據(jù)表

AD533:低成本乘法器、除法器、平方器、平方根過時數(shù)據(jù)表

使用IAR IDE仿真RL78內(nèi)置硬件乘法器和除法器注意事項

使用IAR IDE仿真RL78內(nèi)置硬件乘法器和除法器注意事項

評論