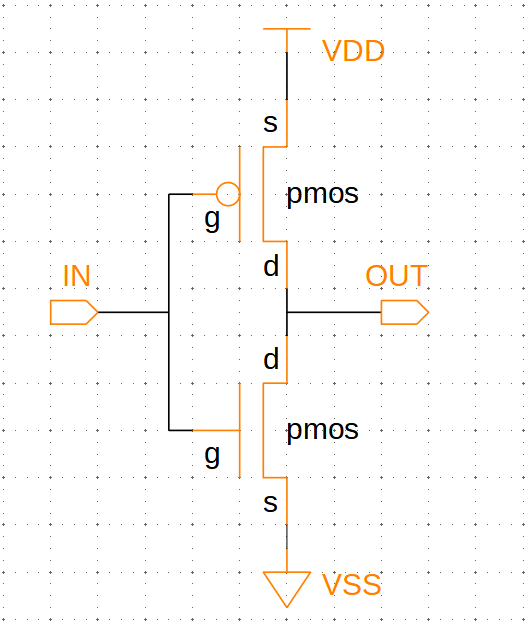

反相器的晶體管級電路

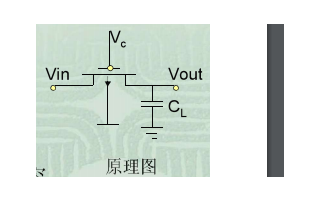

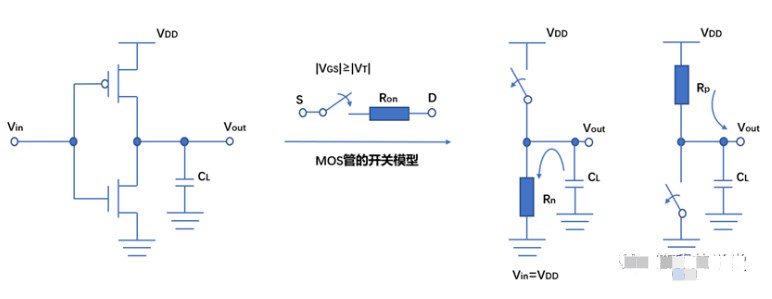

反相器,是數字集成電路最基本的電路之一。由一個pmos和一個nmos組成,輸入信號IN接到pmos和nmos的柵極,輸出信號OUT由漏極引出,如下圖。

假設VDD=3.3V,VSS=0V,mos管的開啟電壓Vt=0.7V:

- 當IN=3.3V時,

- nmos的柵源電壓Vgs>Vt,nmos導通,導通后漏源間的電阻Rds變得很小(比如0.1Ω),所以nmos漏極電壓Vds就被拉到接近地。

- pmos的Vgs=0V,小于開啟電壓Vt,pmos關斷,所以pmos的漏極電壓由nmos決定。

- 綜上,OUT≈0V。

- 當IN=0V時,

- nmos的Vgs=0V,nmos關斷,輸出由pmos決定。

- pmos的Vgs=-3.3V,大于開啟電壓Vt,pmos導通,Rds變得很小,pmos的輸出被拉到接近VDD。

- 綜上,OUT≈3.3V。

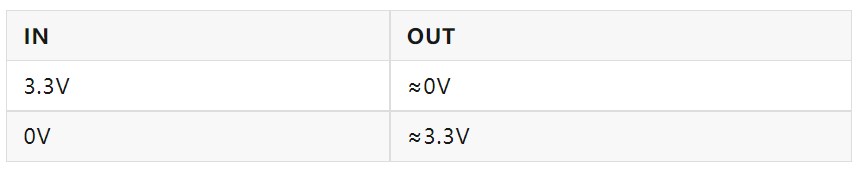

我們把輸入輸出關系整理如下表:

反相器的數字邏輯關系

數字集成電路不太關心電源和地的具體電壓值,只關心輸入輸出邏輯關系。通用把接近VDD的電壓稱為高電平,用數字1表示,而接近VSS的電壓稱為低電平,用數字0來表示。

所以,反相器的輸入輸出電壓關系用邏輯電平可表示為:

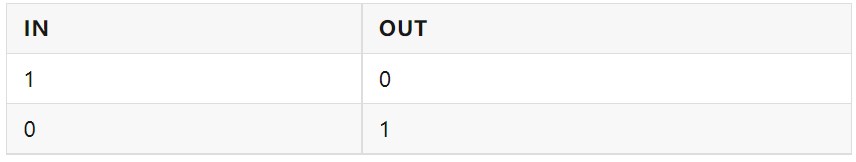

反相器的數學表示法

20世紀初,英國科學家香農指出,布爾代數(一種用來推理的數學)可以用來描述電路:布爾代數的運算法則正好與組合邏輯電路里的“與”、“或”和“非”相同。

交集(與):OUT = IN1 · IN2

并集(或):OUT = IN1 + IN2

差集(反相):OUT =

所以,非邏輯就對應反相器。

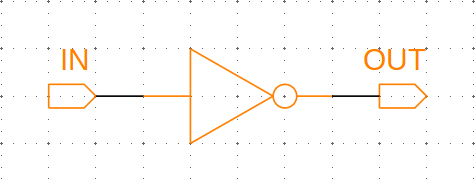

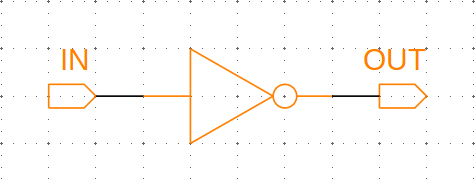

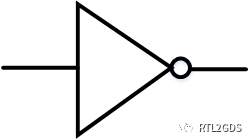

反相器的電路符號

在畫反相器的門級電路符號時可以抽象成下面的符號。輸出端的圓圈表示邏輯上相反。

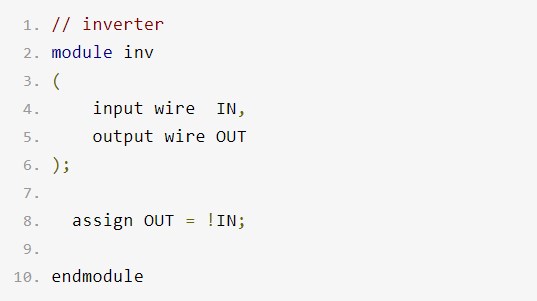

verilog描述

verilog,全稱Verilog HDL,一種硬件描述語言,由美國gateway公司1983年創立。因為verilog從C語言里借鑒了一些語法規則,看起來與C語言有點像,所以在工程中得到廣泛地推廣和應用,因此成為了IEEE標準,IEEE1364。

我們來用verilog描述這個反相器電路的形為(也稱為形為級描述):

第1行:注釋

第2行:定義一個電路模塊,電路模塊的名字是inv

第4~5行:定義這個電路模塊的輸入和輸出端口

第8行:描述了輸出和輸入之間的邏輯關系

第10行:結束這個電路模塊的定義和描述

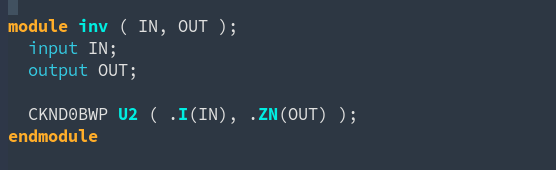

把這段verilog代碼變成電路

用verilog寫出來的這段代碼,只是描述了電路模塊端口和內部的邏輯。然后,使用邏輯綜合工具,把verilog映射成由若干個提前設計好的基本單元電路(即工廠提供的標準單元庫)連線而成的復雜電路。這種自動化的設計方法不再需要像模擬電路一樣手工設計晶體管級的電路了,不僅大大加快了設計效率,也使得設計超大規模集成電路成為可能。

我們把上面的verilog用綜合工具(比如synopsys dc)綜合一下,得到下面的網表:

可以看到,綜合工具把verilog描述的邏輯表達式自動替換成了由標準單元組成的電路了。(注:這里端口的定義格式稍有不一樣,是采用的verilog95的風格。)

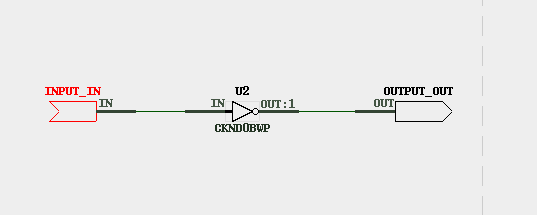

我們可以用網表查看工具自動繪制出門級電路圖:

總結

本文從數字集成電路設計角度闡述了反相器的原理、數字邏輯表示方法、verilog語言的描述、再到把verilog代碼轉換回電路的方法和過程。后面會繼續用這種思維帶領大家學習和設計數字集成電路中的常用電路。

-

反相器

+關注

關注

6文章

311瀏覽量

43507 -

Verilog

+關注

關注

28文章

1351瀏覽量

110391 -

晶體管

+關注

關注

77文章

9745瀏覽量

138892 -

NMOS管

+關注

關注

2文章

121瀏覽量

5534 -

PMOS管

+關注

關注

0文章

83瀏覽量

6722

發布評論請先 登錄

相關推薦

從零開始學CPLD和Verilog HDL編程技術教程免費下載

《從零開始學電路基礎》(從零開始學電子技術叢書)

[從零開始學CPLD和Verilog HDL編程技術]高清版

《從零開始學電子》叢書全套網盤分享

從零開始學CPLD和Verilog HDL編程技術

從零開始學CPLD和Verilog HDL編程技術

cmos反相器設計電路圖

MOS反相器和CMOS反相器的詳細資料說明

從零開始反相器的verilog設計

從零開始反相器的verilog設計

評論