引言

在數(shù)字系統(tǒng)中,總是需要對(duì)一些數(shù)據(jù)進(jìn)行比較,比較兩個(gè)數(shù)值甚至多個(gè)數(shù)值的大小,然后進(jìn)行排序,于是,數(shù)值比較器(Comparator)的邏輯電路便應(yīng)運(yùn)而生。

一、半加器的 Verilog 代碼實(shí)現(xiàn)和 RTL 電路實(shí)現(xiàn)

比較器呢,比較簡(jiǎn)單,那就讓我們從底層硬件代碼看一看到底有多簡(jiǎn)單!!!

下面是比較器的 Verilog 代碼實(shí)現(xiàn):

module Comparator(

input wire [7:0] a, // 比較數(shù)

input wire [7:0] b, // 比較數(shù)

output reg result, // 比較結(jié)果

output reg equal // 比較結(jié)果

);

// 行為描述

always @(a or b) begin

if(a > b)

{equal,result} <= 2'b01; // a 比 b 大

else begin

if(a < b)

{equal,result} <= 2'b00; // a 比 b 小

else

{equal,result} <= 2'b10; // 相等

end

end

// 數(shù)據(jù)流描述

// assign equal = (a == b) ? 1 : 0;

// assign result = (a > b) ? 1 : 0;

endmodule

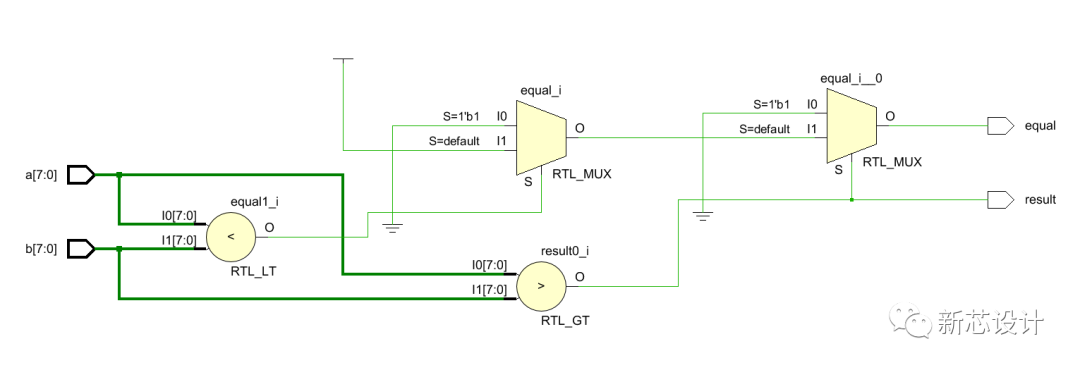

這是一個(gè) 8 位數(shù)值比較器,其 RTL 電路圖如下所示:

8 位數(shù)值比較器的 RTL 電路圖

對(duì)兩個(gè) 8 位二進(jìn)制輸入信號(hào)進(jìn)行大小判斷:如果 a 大,則 out 為高電平;如果 b 大,則 out 為低電平;如果 a 和 b 大小相等,那么 equal 則輸出高電平,否則輸出低電平。

-

邏輯電路

+關(guān)注

關(guān)注

13文章

494瀏覽量

42709 -

比較器

+關(guān)注

關(guān)注

14文章

1658瀏覽量

107431 -

二進(jìn)制

+關(guān)注

關(guān)注

2文章

796瀏覽量

41757 -

RTL

+關(guān)注

關(guān)注

1文章

385瀏覽量

59950 -

Verilog設(shè)計(jì)

+關(guān)注

關(guān)注

0文章

20瀏覽量

6545

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

數(shù)字電路設(shè)計(jì)中的一款強(qiáng)大工具—Verilog編程語(yǔ)言介紹

招聘:數(shù)字電路設(shè)計(jì)師

數(shù)字電路設(shè)計(jì)的基本方法有哪些

基于LabVIEW的數(shù)字電路設(shè)計(jì)和仿真

高速數(shù)字電路設(shè)計(jì)

數(shù)字電路設(shè)計(jì)

數(shù)字電路中的FPGA和verilog教程

數(shù)字電路設(shè)計(jì)方案中DSP與FPGA的比較與選擇

FPGA CPLD數(shù)字電路設(shè)計(jì)經(jīng)驗(yàn)分享.

Verilog數(shù)字系統(tǒng)設(shè)計(jì)——復(fù)雜數(shù)字電路設(shè)計(jì)2(FIFO控制器設(shè)計(jì))

基于Verilog的經(jīng)典數(shù)字電路設(shè)計(jì)(2)比較器

基于Verilog的經(jīng)典數(shù)字電路設(shè)計(jì)(2)比較器

評(píng)論